### Design and Implementation of a Write-based version of Exanet MPI

Michail Nikoloudakis

Thesis submitted in partial fulfillment of the requirements for the

Masters' of Science degree in Computer Science and Engineering

University of Crete School of Sciences and Engineering Computer Science Department Voutes University Campus, 700 13 Heraklion, Crete, Greece

Thesis Advisor: Associate Prof. Polyvios Pratikakis

This work has been performed at the University of Crete, School of Sciences and Engineering, Computer Science Department.

The work has been supported by the Foundation for Research and Technology - Hellas (FORTH), Institute of Computer Science (ICS).

UNIVERSITY OF CRETE COMPUTER SCIENCE DEPARTMENT

#### Design and Implementation of a Write-based version of Exanet MPI

Thesis submitted by **Michail Nikoloudakis** in partial fulfillment of the requirements for the Masters' of Science degree in Computer Science

#### THESIS APPROVAL

Author:

Michail Nikoloudakis

Committee approvals:

euren

Polyvios Pratikakis Associate Professor, Thesis Supervisor

Mattin

Konstantinos Magoutis Associate Professor, Committee Member

Vasileios Papaefstathiou Assistant Professor, Committee Member

Emmanouil Ploumidis PhD, Thesis Advisor

Departmental approval:

ente

Polyvios Pratikakis Associate Professor, Director of Graduate Studies Heraklion, April 2022

#### Design and Implementation of a Write-based version of Exanet MPI

#### Abstract

MPI is one of the leading communication protocols used in HPC (High Performance Computing) suites today due to its portability and scalability. Many HPC applications make use of MPI in order to enable communication between different processes. In the scope of the ExaNeST project, an HPC prototype was deployed in the CARV Laboratory of FORTH consisting of 512 ARMv8 cores coupled with FPGA logic. This prototype makes use of special network primitives designed to allow the low latency transmission of control messages as well as the efficient transfer of large data through the Exanet network. In order to exploit the aforementioned capabilities of the prototype, a highly optimized MPI implementation (Exanet MPI) was developed in the scope of the same project prior to our work. This implementation makes use of the prototype's communication primitives and manages to outperform the well known MPI implementation, MPICH (TCP/IP) by achieving up to 30x lower latency. Examet MPI supports both an eager and a long communication protocol used for short and large MPI transfers respectively. The long protocol depends on emulated DMA reads and supports exclusively sender initiation. Sender initiation is defined as the ability of the sender of an MPI message to initiate the communication with the receiver by issuing an appropriate control message. Despite its simplicity, sender initiation does not let us exploit scenarios in which the receiver posts its request earlier than the sender. In addition, the use of emulated reads requires the receiver to notify the sender about the end of a DMA transfer through the use of an Ack control message which incurs extra latency. In this thesis, we design and implement from scratch a writebased version of the Exanet MPI that supports both sender and receiver initiation. With the use of DMA writes, we render the sender able to determine the end of a DMA transfer by itself without the need of acknowledgment from the receiver. Additionally, we take advantage of cases where a receive request gets posted earlier than a matching send request by letting the receiver initiate communication by asynchronously transferring its DMA related information to the sender. Consequently, a sender that posts its send request after the receiver, can immediately transfer data without the need of further synchronization with the receiver. However, simply adding receiver initiation support to the long protocol also infers some complications including (but not limited to) the significant increase of the eager protocol's latency. We propose our method for successfully facing the complications that arise from the support of receiver initiation and we also further optimize the long protocol by eliminating the need of some control messages. In order to break down the performance gain caused by our optimizations we develop in total 4 variants of the write based Exanet MPI. In each variant, we provide implementations for most point-to-point, collective as well as communicator manipulating functions. We describe the use cases of each developed variant and evaluate them

against the already optimized read based original version of Exanet MPI on the HPC prototype. We offer insight into the ways our control path optimizations improve performance and the factors that let our implementation show more benefit. For the evaluation we use both microbenchmarks and real scientific applications. We show that our implementation can outperform the read based protocol by up to 50% in communication latency while also reduce the total execution time of specific applications by up to 10% (depending on the percentage of communication time they contain).

#### $\Sigma$ χεδιασμός και υλοποίηση μιας έκδοσης του Exanet MPI βασισμένης σε εγγραφή

#### Περίληψη

Το MPI είναι ένα από τα κυρίαρχα πρωτόκολλα επικοινωνίας που χρησιμοποιούνται στις πλατφόρμες HPC (Υπολογισμού Υψηλής απόδοσης) σήμερα λόγω της φορητότητάς και της κλιμακοσιμότητάς του. Πολλές HPC εφαρμογές κάνουν χρήση του MPI για να καταστήσουν εφικτή την επικοινωνία μεταξύ διφορετικών διεργασιών.Στα πλαίσια του έργου ExaNeST, ένα νέο HPC πρωτότυπο αναπτύχθηκε στο εργαστήριο CARV του I.T.E αποτελούμενο από συνολικά 512 ARMv8 πυρήνες συνδυασμένους με λογική FPGA. Το πρωτότυπο αυτό κάνει χρήση ειδικών μονάδων επικοινωνίας σχεδιασμένων να επιτρέπουν τη διάδοση μηνυμάτων συγχρονισμού με πολύ μικρή καθυστέρηση (latency) καθώς και την αποδοτική μεταφορά μεγάλων δεδομένων μέσω του δικτύου Exanet.

Προκειμένου να αξιοποιηθούν οι προαναφερθείσες ικανότητες του πρωτοτύπου, αναπτύχθηκε μια υψηλά βελτιστοποιημένη MPI υλοποίηση (Exanet MPI) στα πλαίσια του ίδιου έργου, πριν από την αρχή της δουλειάς μας. Η υλοποίηση αυτή κάνει χρήση των μονάδων επικοινωνίας του HPC πρωτοτύπου και καταφέρνει να επιτύχει καλύτερη απόδοση από την γνωστή MPI υλοποίηση MPICH επιτυγχάνοντας μέχρι και 30x μικρότερη καθυστέρηση διάδοσης δεδομένων (latency). Το Exanet MPI υποστηρίζει ένα eager και ένα long πρωτόκολλο επικοινωνίας για μικρές και μεγάλες μεταφορές δεδομένων αντίστοιχα. Το πρωτόκολλο long βασίζεται σε προσομοιωμένα DMA reads (read based) και υποστηρίζει εκκίνηση της επικοινωνίας αποκλειστικά από τον αποστολέα. Η "εκκίνηση από τον αποστολέα" ορίζεται ως η ικανότητα του αποστολέα ενός MPI μηνύματος να ξεκινήσει την επικοινωνία με τον παραλήπτη εκδίδοντας το κατάλληλο μήνυμα συγχρονισμού. Παρά την απλότητα της, η εκκίνηση αποκλειστικά από τον αποστολέα. Επιπρόσθετα, η χρήση προσομοιωμένων DMA reads απαιτεί από τον αποστολέα. Επιπρόσθετα, η χρήση προσομοιωμένων DMA reads απαιτεί από τον αποστολέα δεν μας επιτρέπει να εκμεταλλευτούμε περιπτώσεις όπου ο παραλήπτης καταχωρεί την αίτηση του νωρίτερα από τον αποστολέα. Επιπρόσθετα, η χρήση προσομοιωμένων DMA reads απαιτεί από τον παραλήπτη ου ενημερώσει τον αποστολέα σχετικά με το τέλος μιας DMA μεταφοράς μέσω ενός Ack μηνύματος συγχρονισμού, κάτι που επιφέρει επιπλέον καθυστέρηση (latency).

Σε αυτή την εργασία, σχεδιάζουμε και υλοποιούμε εξ αρχής μια έκδοση του Exanet MPI βασισμένη σε εγγραφή (write-based) η οποία υποστηρίζει εκκίνηση επικονωνίας από τον αποστολέα αλλά και από τον παραλήπτη. Με τη χρήση DMA writes, καθιστούμε τον αποστολέα ικανό να αντιληφθεί το τέλος μιας DMA μεταφοράς δίχως να χρειάζεται επιβεβαίωση από τον παραλήπτη. Επιπρόσθετα, εκμεταλλευόμαστε περιπτώσεις όπου η αίτηση παραλαβής καταχωρείται νωρίτερα από την αίτηση αποστολής επιτρέποντας στον παραλήπτη να μεταφέρει ασύγχρονα στον αποστολέα όλες τις πληροφορίες που χρειάζονται για μια DMA μεταφορά. Συνεπώς, ο αποστολέας που θα καταχωρήσει την αίτηση αποστολής επιτρέποντας στον παραλήπτη, μπορεί να μεταφέρει ασύγχρονα στον αποστολέα όλες τις πληροφορίες που χρειάζονται για μια DMA μεταφορά. Συνεπώς, ο αποστολέας που θα καταχωρήσει την αίτηση αποστολής μετά τον παραλήπτη, μπορεί να μεταφέρει άμεσα τα δεδομένα του χωρίς να υπάρχει ανάγκη για περαιτέρω συγχρονισμό με τον παραλήπτη. Παρ'όλα αυτά, η απλή προσθήκη της δυνατότητας εκκίνησης από τον παραλήπτη στο long πρωτόκολλο επιφέρει κάποιες επιπλοκές συμπεριλαμβανομένης και της μεγάλης αύξησης της καθυστέρησης στο eager πρωτόκολλο. Προτείνουμε δικές μας μεθόδους για την επιτυχή αντιμετώπιση των επιπλοκών που προκύπτουν από την υποστήριξη εκκίνησης από τον παραλήπτη καθώς επίσης βελτιστοποιούμε περαιτέρω το long πρωτόκολλο εξουδετερώνοντας την ανάγκη χρήσης κάποιων μηνυμάτων συγχρονισμού. Προκειμένου να αναλύσουμε το όφελος απόδοσης των βελτιστοποιήσεων μας, αναπτύσσουμε συνολικά τέσσερις παραλαγές του

Εxanet MPI βασισμένου σε εγγραφή. Σε κάθε παραλλαγή, παρέχουμε υλοποιήσεις για τις περισσότερες εκ των point-to-point, collective, και communicator manipulating συναρτήσεων. Περιγράφουμε τις περιπτώσεις χρήσης της κάθε παραλλαγής και αξιολογούμε τις παραλλαγέςτης υλοποίησής μας έναντι της αρχικής, ήδη βελτιστοποιημένης, read based έκδοσης του Exanet MPI στο HPC πρωτότυπο. Εμβαθύνουμε στους τρόπους με τους οποίους οι βελτιστοποιήσεις μας στο μονοπάτι συγχρονισμού βελτιώνουν την απόδοση καθώς και στους παράγοντες που επιτρέπουν στην υλοποίησή μας να δείξει περισσότερο όφελος. Για την αξιολόγηση χρησιμοποιούμε τόσο microbenchmarks όσο και πραγματικές επιστημονικές εφαρμογές. Δείχνουμε ότι η υλοποίησή μας μπορεί να ξεπεράσει σε απόδοση το read based πρωτόκολλο προσφέροντας έως και 50% μικρότερη καθυστέρηση (latency) ενώ μπορεί να μειώσει το συνολικό χρόνο εκτέλεσης ορισμένων εφαρμογών έως και κατά 10%. (ανάλογα με το ποσοστό χρόνου επικοινωνίας που περιέχουν)

#### Acknowledgments

First of all, I am grateful to my supervisor Polyvios Pratikakis as well as to my advisor Manolis Ploumidis for their constant support and guidance throughout this thesis. I would also like to thank Associate Professor Konstantinos Magoutis and Assistant Professor Vassilis Papaefstathiou for agreeing to be members of my thesis' examination committee.

Special thanks to the CARV Laboratory members Pantelis Xirouchakis, Fabien Chaix, Marios Asiminakis and Astrinos Damianakis for their useful tips regarding the HPC Prototype, its hardware blocks' userspace API and benchmark applications used in the evaluation chapter of this thesis.

Last but not least, I would like to thank my family for their mental support and help which made the process of completing my studies a lot easier.

στους γονείς μου

## Table of Contents

| Contents                                                                                         |

|--------------------------------------------------------------------------------------------------|

| Table of Contentsi                                                                               |

| List of Tablesii                                                                                 |

| List of Figuresiii                                                                               |

| 1 Introduction                                                                                   |

| 2 Background                                                                                     |

| 2.1 MPI                                                                                          |

| 2.2 Packetizers and Mailboxes                                                                    |

| 2.3 RDMA Engine                                                                                  |

| 2.4 User Level Communication Libraries                                                           |

| 2.5 The HPC Prototype                                                                            |

| 2.6 Read Based Exanet MPI Implementation                                                         |

| 3 Design and Implementation of the Write-based Exanet MPI Protocol10                             |

| 3.1 Designing a preliminary sender and receiver initiated write based protocol10                 |

| 3.1.1 Designing a preliminary sender and receiver initiated write based long protocol10          |

| 3.1.2: Designing a preliminary sender and receiver initiated write based eager protocol.15       |

| 3.2 Basic description of the preliminary write-based MPI protocol's implementation18             |

| 3.2.1 Initiation of the MPI library                                                              |

| 3.2.2 Structure of Request Object in our Implementation                                          |

| 3.2.3 General Control logic of Basic Point-to-Point primitives in the first version of the       |

| Write-based Exanet MPI                                                                           |

| 3.2.4 General Control logic of the Progress Engine                                               |

| 3.2.5 Implementation of Synchronization and Locking Mechanisms                                   |

| 3.2.6 Data Structures Design                                                                     |

| 3.3 Designing an improved sender and receiver initiated write based long protocol:               |

| Elimination of the Env Control message                                                           |

| $3.4$ Basic description of the second write-based MPI variant's implementation $\ldots\ldots.33$ |

| 3.4.1 Structure of Request Object                                                                |

| 3.4.2 General Control logic of Basic Point-to-Point primitives in the second version of          |

| the Writebased Exanet MPI                                                                        |

| 3.4.3 General Control logic of the Progress Engine Thread in the second version of the           |

| Write-based Exanet MPI                                                                           |

| 3.5 Designing an improved sender and receiver initiated eager based protocol: Elimination        |

| of the Ack control message and receiver initiation in eager communication $\ldots\ldots.35$      |

| $3.6$ Basic description of the third write-based MPI variant's implementation $\ldots\ldots.44$  |

| 3.6.1 Structure of Request Object                                                                |

| 3.6.2 General Control logic of Basic Point-to-Point primitives in the third version of the       |

| Write-based Exanet MPI                                                                           |

| 3.6.3 General Control logic of the Progress Engine Thread in the third version of t | he |

|-------------------------------------------------------------------------------------|----|

| Write-based Exanet MPI                                                              | 45 |

| 3.7 Changing type of MPI_Request                                                    | 45 |

| 3.8 Handling Communicator manipulation                                              | 46 |

| 3.9 Memory Allocation Optimizations                                                 |    |

| 3.10 Supported MPI Send modes                                                       |    |

| 3.11 Support for Persistent Point-to-Point MPI Requests                             |    |

| 3.12 Support for Probing Primitives                                                 |    |

| 3.13 Support for Collective Primitives                                              | 50 |

| 3.13 Support for Collective Primitives                                              | 50 |

| 3.14 Support for an Optimistic version of the write based variant                   | 52 |

| 4 Evaluation                                                                        | 54 |

| 5 Related Work                                                                      |    |

| 6 Conclusions and Future Work                                                       |    |

## List of Tables

Table 3.1: Comparison of bandwidth with original modified MPI\_Request ......46

## List of Figures

| Figure 2.1: HPC prototype's Example topology                                                 | 3 |

|----------------------------------------------------------------------------------------------|---|

| Figure 2.2 Long Protocol of the Read Based Exanet MPI                                        | 3 |

| Figure 2.3 Eager protocol of the Read Based Exanet MPI                                       |   |

| Figure 3.1: Sender initiated communication in the write based Exanet MPI                     |   |

| Figure 3.2: Receiver initiated communication in the write based Exanet MPI                   | 2 |

| Figure 3.3: MPI_ANY_SOURCE receiver initiation suspension                                    | 3 |

| Figure 3.4: MPI_ANY_SOURCE receiver initiation suspension, non blocking receives14           | 1 |

| Figure 3.5 Concurrent Receiver and Sender initiation                                         | 5 |

| Figure 3.6 Problematic scenario in the write based MPI's eager protocol16                    | 3 |

| Figure 3.7: Eager protocol, Matching Eager Send and Receive requests posted concurrently 16  | 3 |

| Figure 3.8 Eager Protocol, Eager receive request posted before matching eager send request   |   |

|                                                                                              | 7 |

| Figure 3.9: Eager Protocol, Eager send posted before matching receive request1               | 7 |

| Figure 3.10: Eager protocol: Non blocking send and MPI_Wait23                                | 3 |

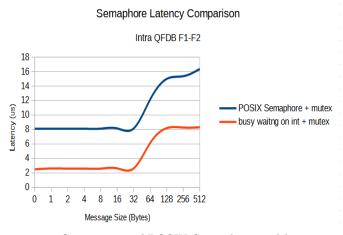

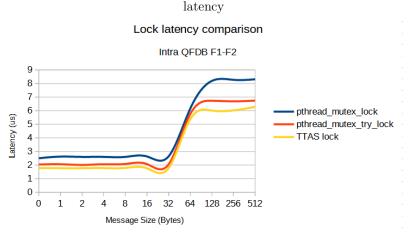

| Figure 3.11: Comparison of POSIX Semaphore and busy waiting latency28                        | 5 |

| Figure 3.12: Comparison of different locking mechanisms' latency                             | 5 |

| Figure 3.13: Receiver initiation with omitted Env control messsage                           | 3 |

| Figure 3.14: Sender initiation with omitted Env control message                              | 3 |

| Figure 3.15: Problematic scenario of concurrent sender and receiver initiation with omitted  |   |

| Env control message                                                                          | ) |

| Figure 3.16: Sender initiation with omitted Env control message, correct execution           | 1 |

| Figure 3.17: Receiver initiation with omitted Env control message, correct execution32       | 1 |

| Figure 3.18: Concurrent sender and receiver initiation with omitted Env control message,     |   |

| correct execution                                                                            | 2 |

| Figure 3.19: Problematic scenario with two sending threads and omitted Env control message   |   |

| Figure 3.20: Non blocking sends with omitted Env control message                             | 3 |

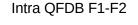

| Figure 3.21: Comparing read based and write based MPI in eager communication latency30       | 3 |

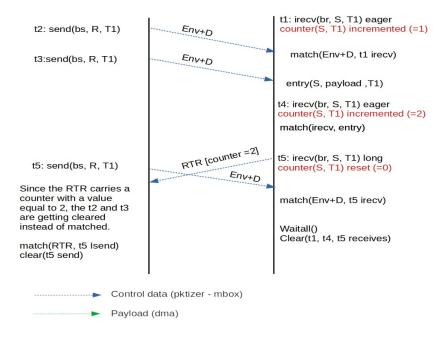

| Figure 3.22: Eager protocol: Piggybacked counter in RTR optimization, match of long received | 9 |

| with eager send                                                                              | 7 |

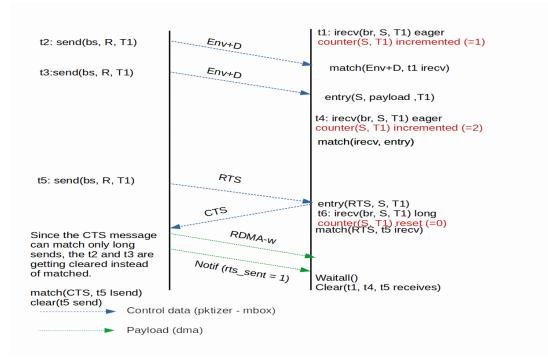

| Figure 3.23: Eager protocol: Piggybacked counter in RTR optimization, CTS message clears     |   |

| pending eager sends                                                                          | 3 |

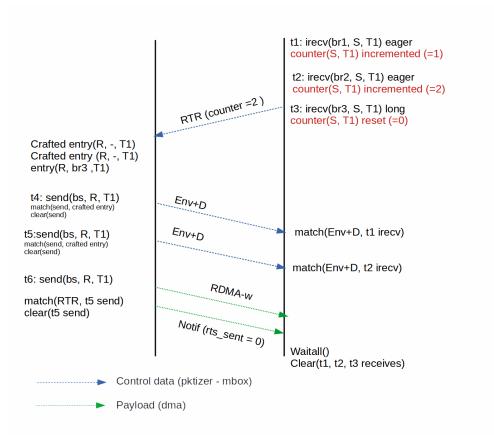

| Figure 3.24: Eager protocol: Piggybacked RTR issued before any matching eager send           |   |

| request is posted. Use of crafted requests                                                   | ) |

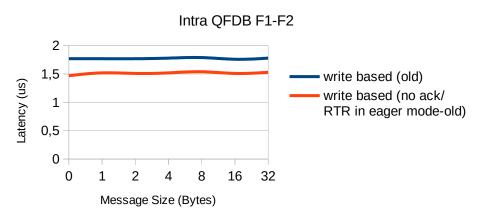

| Figure 3.25: Comparison of the initial write based MPI eager protocol with the optimized     |   |

| eager protocol in terms of latency                                                           | ) |

| Figure 3.26: Piggybacked ticket_ID in RTR optimization, long receive matching long send.42   | 1 |

| Figure 3.27: Piggybacked Ticket ID optimization, eager receive matching eager send           | 1 |

| Figure 3.28: Posted Send request clears useless received requests (RTRs)                     | 3 |

| Figure 3.29: Comparison of the original eager protocol of the write based MPI with the two |

|--------------------------------------------------------------------------------------------|

| different optimizations                                                                    |

| Figure 3.30: Original MPI_Request type in mpi.h46                                          |

| Figure 3.31: Modified MPI_Request type in mpi.h46                                          |

| Figure 3.32: Added function to support communicator ID exporting                           |

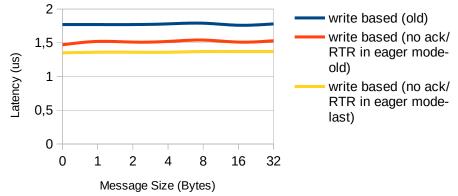

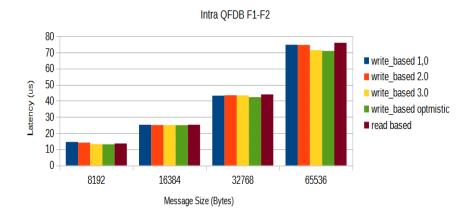

| Figure 4.1 OSU Latency: Comparison of all Exanet MPI variants, Eager Messages              |

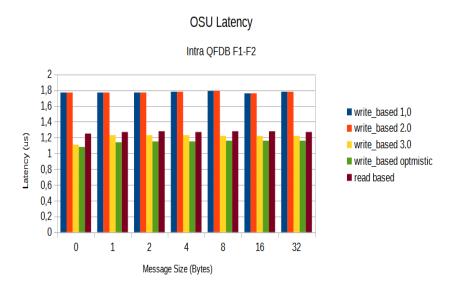

| Figure 4.2 OSU Latency: Comparison of all Exanet MPI variants, Short Messages              |

| Figure 4.3 OSU Latency: Comparison of all Exanet MPI variants, Medium Messages57           |

| Figure 4.4 OSU Latency: Comparison of all Exanet MPI variants, Large Messages              |

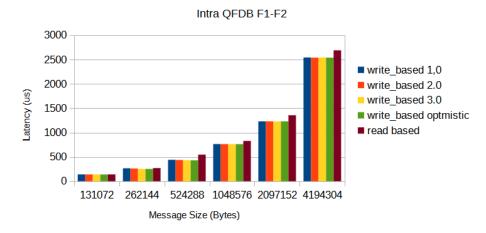

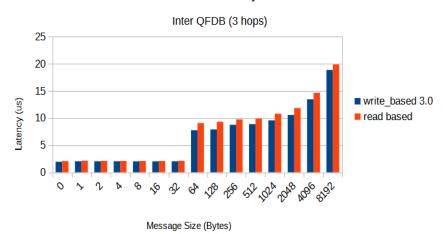

| Figure 4.5: OSU Latency: Comparison of small messages' latency between 2 QFDBs in a 3      |

| hops distance                                                                              |

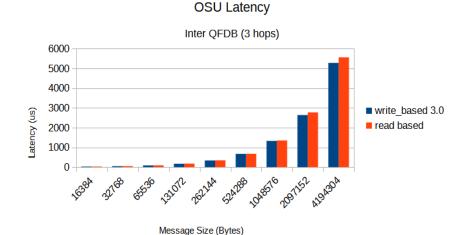

| Figure 4.6: OSU Latency: Comparison of big messages' latency between 2 QFDBs in a 3        |

| hops distance                                                                              |

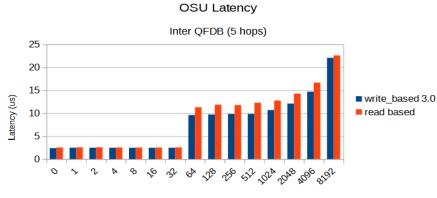

| Figure 4.7: OSU Latency: Comparison of small messages' latency between 2 QFDBs in a 5      |

| hops distance                                                                              |

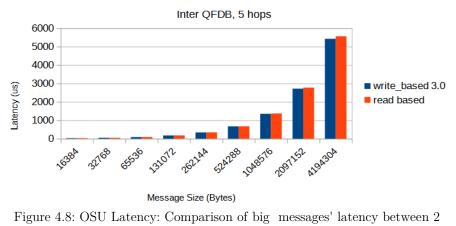

| Figure 4.8: OSU Latency: Comparison of big messages' latency between 2 QFDBs in a 5        |

| hops distance                                                                              |

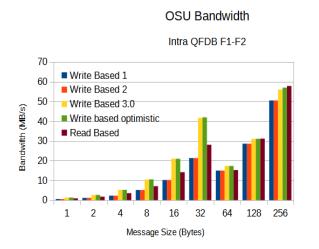

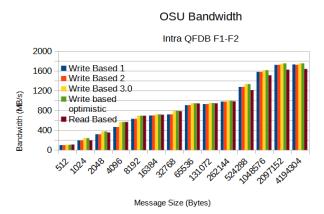

| Figure 4.9: Comparison of all Exanet MPI variants' bandwidth, small messages               |

| Figure 4.10: Comparison of all Exanet MPI variants' bandwidth, big messages                |

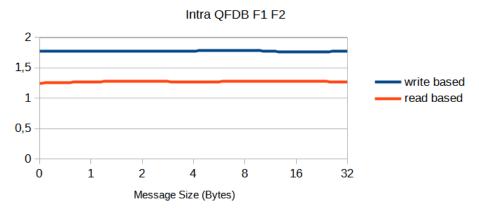

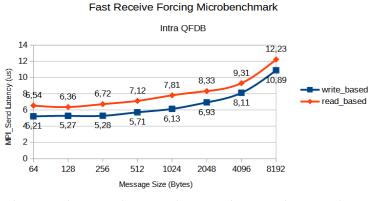

| Figure 4.11: Comparison of Read and Write Based MPI in fast receives, intra QFDB61         |

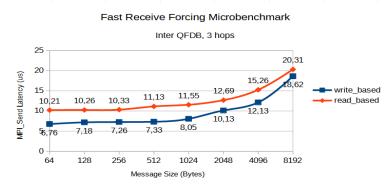

| Figure 4.12: Comparison of Read and Write Based MPI in fast receives, 3 hops distance61    |

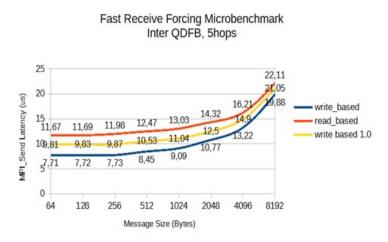

| Figure 4.13: Comparison of Read and Write Based MPI in fast receives, 5 hops distance62    |

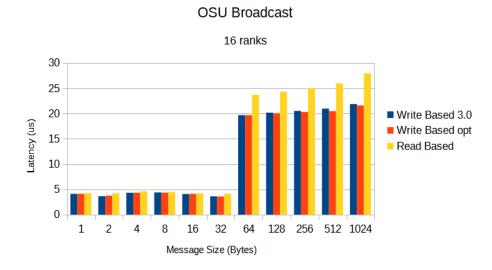

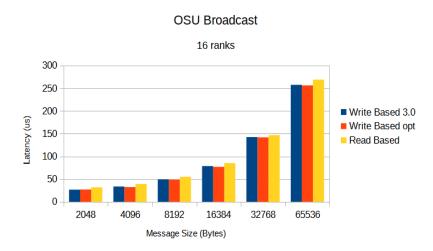

| Figure 4.14: OSU_Broadcast latency comparison, small messages with 16 ranks                |

| Figure 4.15: OSU_Broadcast latency comparison, medium messages with 16 ranks               |

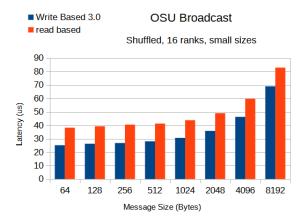

| Figure 4.16: OSU_Broadcast latency comparison, small messages with 16 ranks inshuffled     |

| hostfie                                                                                    |

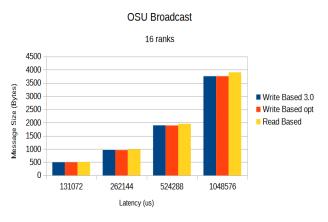

| Figure 4.17: OSU_Broadcast latency comparison, big messages with 16 ranks                  |

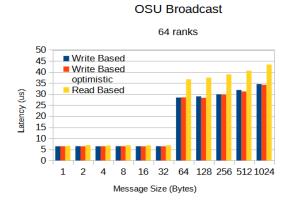

| Figure 4.18: OSU_Broadcast latency comparison, small messages with 64 ranks                |

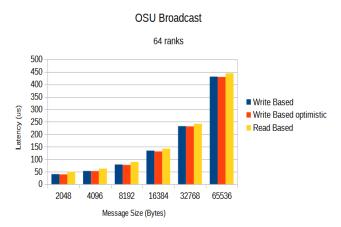

| Figure 4.19: OSU_Broadcast latency comparison, medium messages with 64 ranks               |

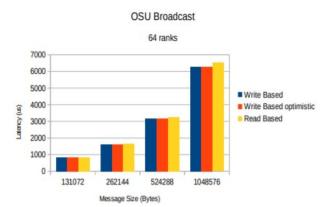

| Figure 4.20: OSU_Broadcast latency comparison, big messages with 64 ranks                  |

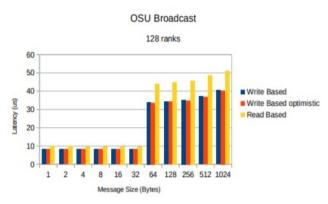

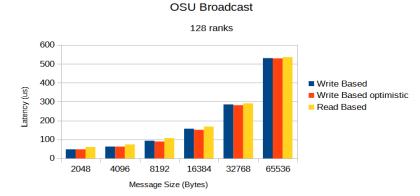

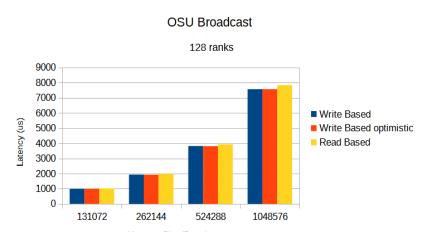

| Figure 4.21: OSU_Broadcast latency comparison, small messages, 128 ranks                   |

| Figure 4.22: OSU_Broadcast latency comparison, small messages with 128 ranks65             |

| Figure 4.23: OSU_Broadcast latency comparison, big messages with 128 ranks65               |

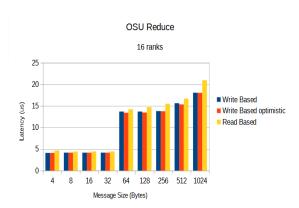

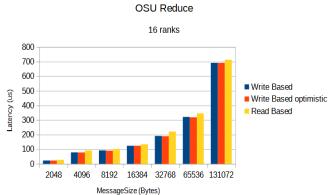

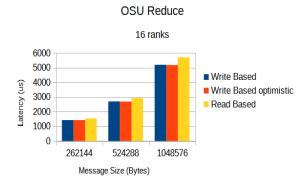

| Figure 4.25: OSU Reduce: latency comparison, medium messages with 16 ranks                 |

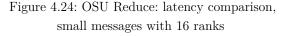

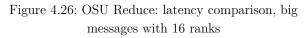

| Figure 4.26: OSU Reduce: latency comparison, big messages with 16 ranks                    |

| Figure 4.27: OSU Reduce: latency comparison, small messages with 64 ranks                  |

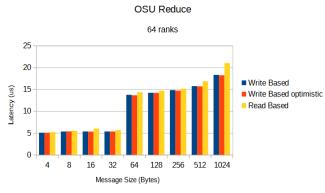

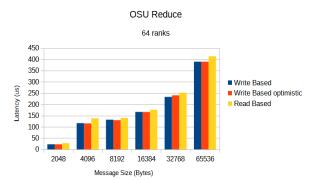

| Figure 4.28: OSU Reduce: latency comparison, medium messages with 64 ranks67               |

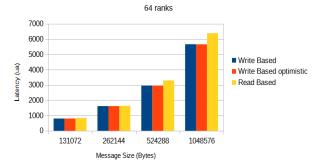

| Figure 4.29: OSU Reduce: latency comparison, big messages with 64 ranks                    |

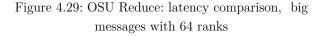

| Figure 4.30: OSU Reduce: latency comparison, small messages with 128 ranks                 |

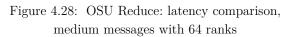

| Figure 4.31: OSU Reduce: latency comparison, medium messages with 128 ranks                |

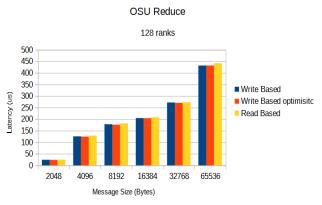

| Figure 4.32: OSU Reduce: latency comparison, big messages with 128 ranks                   |

| Figure 4.33: OSU Reduce: latency comparison, small messages with 128 ranks in a shuffled   |

| hostfile                                                                                   |

| Figure 4.34: | OSU Barrier: latency comparison                                                                 | .68 |

|--------------|-------------------------------------------------------------------------------------------------|-----|

| Figure 4.35: | OSU_Scatter latency comparison, small messages with 16 ranks                                    | .69 |

| Figure 4.36: | OSU_Scatter latency comparison, medium messages with 16 ranks                                   | .69 |

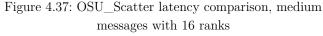

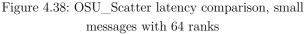

| Figure 4.37: | OSU_Scatter latency comparison, medium messages with 16 ranks                                   | .69 |

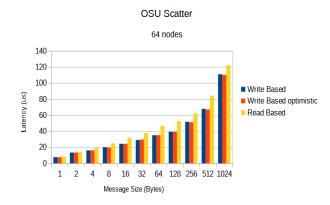

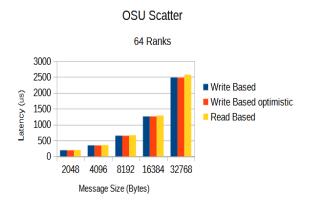

| Figure 4.38: | OSU_Scatter latency comparison, small messages with 64 ranks                                    | .69 |

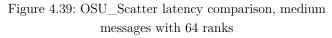

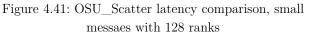

| Figure 4.39: | <code>OSU_Scatter</code> latency comparison, medium messages with 64 ranks                      | 70  |

| Figure 4.40: | OSU_Scatter latency comparison, big messages with 64 ranks                                      | .70 |

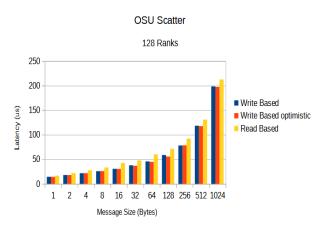

| Figure 4.41: | OSU_Scatter latency comparison, small messaes with 128 ranks                                    | .70 |

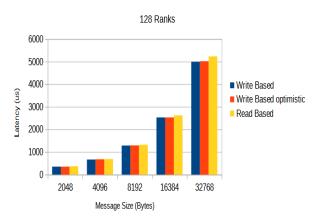

| Figure 4.42: | OSU_Scatter latency comparison, medium messages with 128 ranks $\ \ldots \ldots$                | .70 |

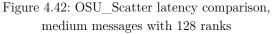

| Figure 4.43: | OSU_Scatter latency comparison, big messages with 128 ranks                                     | .70 |

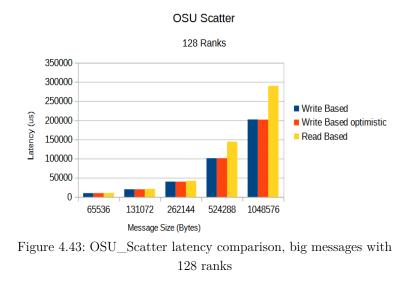

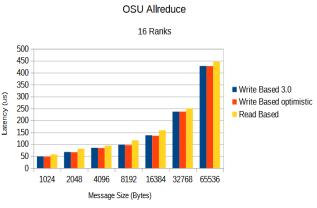

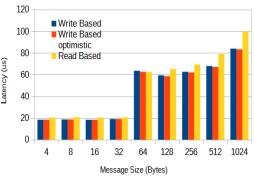

| Figure 4.44: | OSU_Allreduce latency comparison, small messages with 16 ranks                                  | .71 |

| Figure 4.45: | OSU_All<br>reduce latency comparison, medium messages with 16 ranks<br>$\ \ldots \ldots \ldots$ | .71 |

| Figure 4.46: | OSU_Allreduce latency comparison, big messages with 16 ranks                                    | .71 |

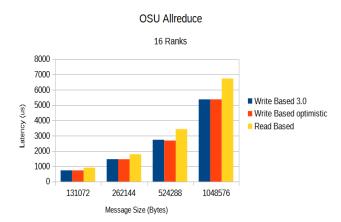

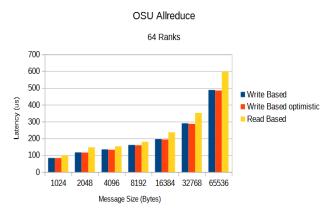

| Figure 4.47: | OSU_All<br>reduce latency comparison, small messages with $64\ {\rm ranks}\ \ldots \ldots$      | .71 |

| Figure 4.48: | OSU_All<br>reduce latency comparison, medium messages with $64\ {\rm ranks}\ \ldots \ldots$     | .72 |

| Figure 4.49: | OSU_Allreduce latency comparison, big messages with 64 ranks                                    | .72 |

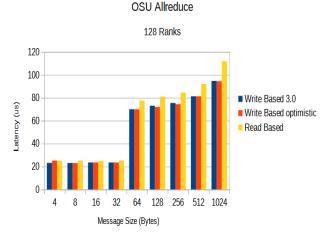

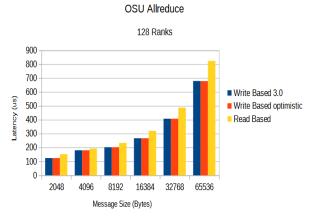

| Figure 4.50: | OSU_All<br>reduce latency comparison, small messages with 128 ranks<br>$\ \ldots \ldots \ldots$ | .72 |

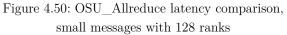

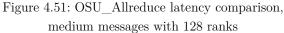

| Figure 4.51: | OSU_All<br>reduce latency comparison, medium messages with 128 ranks<br>$\ \ldots \ldots$       | .72 |

| Figure 4.52: | OSU_Allreduce latency comparison, big messages with 128 ranks                                   | .72 |

| Figure 4.53: | Total duration comparison, LU NAS Benchmark                                                     | .74 |

| Figure 4.54: | Communication time comparison, LU NAS Benchmark                                                 | .74 |

|              | Mops/s comparison, LU NAS Benchmark                                                             |     |

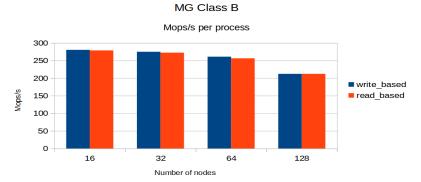

|              | Total duration comparison, MG NAS Benchmark                                                     |     |

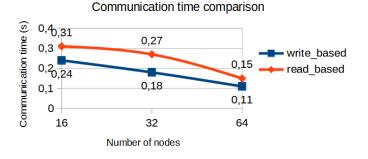

| Figure 4.57: | Communication time comparison, MG NAS Benchmark                                                 | .75 |

| -            | Mop/s comparison, MG NAS Benchmark                                                              |     |

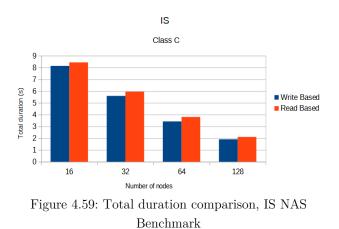

| Figure 4.59: | Total duration comparison, IS NAS Benchmark                                                     | .76 |

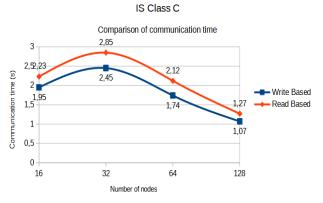

| Figure 4.60: | Communication time comparison, IS NAS Benchmark                                                 | .76 |

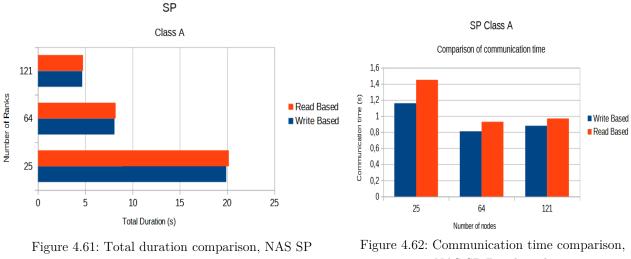

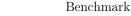

| Figure 4.61: | Total duration comparison, NAS SP Benchmark                                                     | .77 |

| -            | Communication time comparison, NAS SP Benchmark                                                 |     |

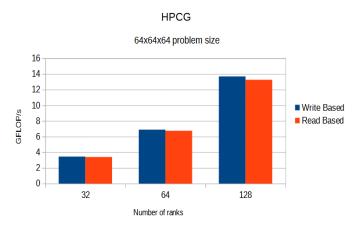

| Figure 4.63: | GFLOP/s comparison, HPCG Benchmark                                                              | .78 |

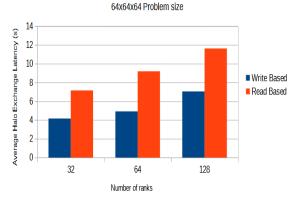

| Figure 4.64: | Halo Exchange average latency comparison, HPCG Benchmark                                        | .78 |

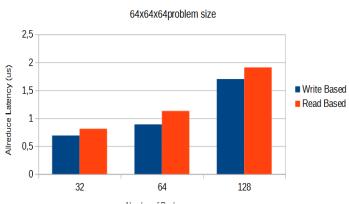

| Figure 4.65: | All Reduce average latency comparison, HPCH Benchmark                                           | .78 |

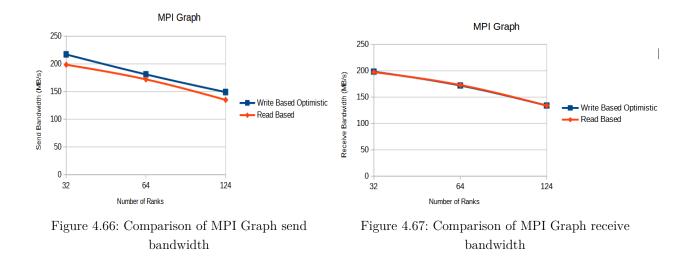

| Figure 4.66: | Comparison of MPI Graph send bandwidth                                                          | .79 |

| -            | Comparison of MPI Graph receive bandwidth                                                       |     |

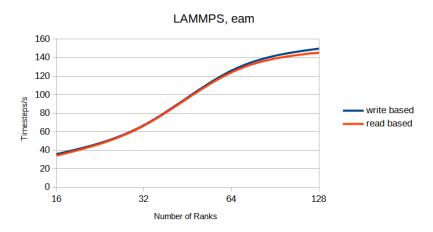

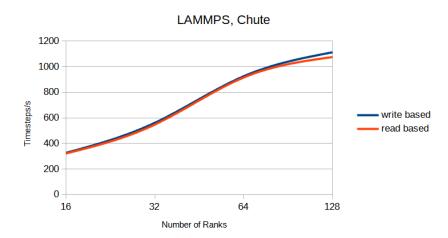

| Figure 4.69: | LAMMPS eam Problem, Throughput Evaluation                                                       | .80 |

|              | Entition Scalin Problem, Philoughput Evaluation                                                 |     |

### Chapter 1

### Introduction

High Performance Computing (HPC) is the practice of using parallel processing units in order to achieve much higher performance and perform complex calculations. Through years of technological advancement, the computation power required for HPC applications has started moving towards exascale. This fact constitutes a motive towards a general reconsideration of the modern HPC suites' design in order to keep their cost viable. To this end, a new HPC prototype has been deployed in the CARV Laboratory of FORTH, which makes use of novel, low cost communication primitives developed in the scope of the ExaNeST project. The proposed architecture used in that prototype offers near optimal message latency with minimum kernel involvement while at the same time keeping the cost low. The new communication primitives make use of an accelerated a custom packet-based hierarchical interconnect network called Exanet, developed in the scope of the same project. In order to enable support for the majority of HPC applications, an MPI runtime has also been deployed called Exanet MPI [16]. MPI is currently the dominant communication protocol used in HPC due to its portability, scalability and high performance. The MPI standard provides definitions of a wide range of primitive functions which focus mainly on message handling and are extremely useful for the development of parallel applications while it also determines how the features of the interface must behave in any different implementation. More specifically, MPI library consists of functions related to point point communication (between two processes) as well as functions related to collective communication regarding groups of processes. MPI implementations typically use two different protocols for transferring messages depending on their size. For small messages an eager protocol is used in which the sender sends the entire message to the receiver, where the receiver provides sufficient buffering space for the incoming messages. On the other hand, for large messages that cannot fit in a control message, a rendezvous long protocol is used in which the sender and the receiver negotiate before the data transfer takes place. The data transfer of a long rendezvous protocol usually happens through a Remote Direct Memory Access (RDMA) engine. A rendezvous long protocol can be sender initiated, receiver initiated or hybrid. Sender initiation means that the sending process is responsible for initiating the synchronization process with the receive before the DMA transfer takes place. Respectively, receiver initiation gives the capability of initiating the communication to the receiving process.

Exanet MPI supports both an eager and a long protocol. Exanet MPI's long protocol uses exclusively sender initiation and relies on **emulated DMA reads**. Specifically, a sending process initiates the communication by advertising the address of the send buffer to the receiving process. Subsequently, the receiver transfers the contents of the send buffer to its receive buffer by initiating a DMA write from the sender's side with the use of control messages. At the end of the emulated read, it notifies the sender about the end of the transfer with an acknowledgment control message. Exanet MPI manages to outperform MPICH by achieving up to 96% lower latency and thus offers HPC applications a high performing communication interface in the aforementioned HPC prototype. However, sender initiation, despite being the dominant form of communication initiation used in the long protocol of most implementations, also has some drawbacks. First, in cases where a receiving process posts a receive request before the posting of matching send request by the sender, the protocol does not let the receiver initiate the communication. In that way, the intermediate time between the receive's and the send's posting is not exploited. Secondly, relying on emulated reads requires the receiver to notify the sender about the end of DMA transfers which incurs extra latency. Consequently, it was a topic of our research whether the already optimized Exanet MPI can be urther improve.

In this thesis, we designed and implemented from a scratch a write-based version of Exanet MPI. This new MPI implementation relies exclusively on DMA write operations and supports both sender and receiver initiation. With the use of DMA writes, we render the sender able to determine the end of a DMA transfer by itself without the need of an acknowledgment control message from the receiver. Specifically, the receiver

is able to initiate communication by asynchronously transferring its DMA related information to the sender. As a consequence, a sender that posts its send request after the receiver can immediately perform a DMA write without the need of further synchronization with the receiver. Our implementation combines the benefits of both types of initiations of the long protocol while supporting an eager protocol as well. Through implementing four variants of the write-based implementation we managed to find out and face the complexities the coexistence of receiver and sender initiations infers and even outperform the already existing version of the Exanet MPI. In addition, we broke down the performance gain of our implementation by comparing all four variants with each other, each one of them contributing different optimizations. Our MPI implementation relies on reimplementing most of the point-to-point, collective and communicator manipulation MPI routines and delegating them through the Exanet network by making use of network primitives of the HPC prototype for inter-process communication. Initially, we created an MPI variant that combines sender and receiver initiation in the long protocol but also contains some overheads that arise from the coexistence of the two initiation methods. Secondly, we further optimized the long protocol of receiver initiation by eliminating the need of one control message and, in a third axis, we came up with a method of eliminating the overhead receiver initiations infers to the eager protocol. Lastly, we implemented an optimistic (speculative) variant of our implementation that makes some assumptions that may partly violate the MPI standard but can be used to improve performance with some applications. Our evaluation showed that our implementation can compete and outperform the read-based version of the Exanet MPI in both the long and eager protocol. Overall, we make the following contributions:

- We design a write-based protocol that utilizes the network primitives of the new HPC prototypes while supporting

- We detect and face all the complexities that arise by supporting both sender and receiver initiation

- We manage to optimize the control path of the long protocol in both sender and receiver initiation scenarios. Specifically, with our optimizations, the long protocol requires one less message in comparison to the read-based version's control path. In scenarios where a receive request gets posted first, our implementation uses 2 less synchronization messages compared to the read-based variant.

- We propose an optimistic variant that can suggest new changes to the MPI standard

- We underline the impact of the topology of MPI processes and how it can affect performance.

- We attempt to find a sweet spot for the cost and benefit each of our optimization provides and suggest the most suitable variant for different scenarios.

The rest of this thesis is organized as follows. We first give the necessary background information on MPI, the HPC prototype, the network primitives it uses and the Read-based MPI implementation. In Chapter 3 we provide a detailed analysis of our implementation as well as our thinking process towards aeach one of the variants implemented. Chapter 4 contains our thorough evaluation's methodology and results while in Chapter 5 we present related work from the academic literature. Finally, in Chapter 6, we sum up our conclusions and discuss future work.

### Chapter 2

### Background

#### $2.1 \ \mathrm{MPI}$

As mentioned in the introduction, our work includes the reimplementation of several MPI routines. MPI is a specification for message passing libraries designed to function on parallel computer architectures and it is maintained by the MPI Forum [19]. Its purpose is to constitute a standard for writing message passing programs while offering portability, efficiency and flexibility. Originally, MPI was designed for distributed memory architecture but through years of development and technological advancement. MPI supports both distributed and shared memory as well as hybrid architectures. Up to this day, MPI has managed to replace all previous libraries regarding message passing and is considered a standard supported on virtually all HPC platforms. There are many different implementations [20, 21] of the MPI Standard which have emerged through the years by different vendors. However, due to the standard's portability, source code that uses MPI can be used with different MPI implementations with little or no modification at all. The MPI standard undergoes constant changes and improvements and, up to the time of writing, its latest version is MPI-3 which consists of more than 430 routines. MPI's communication routines can be split into two major categories: Point-to-point and Collective routines. Point-to-Point routines are functions that regard communication between two processes while collective routines include all the process of a communicator in the data exchange. A communicator can be defined as a subgroup of processes. Each MPI process of a communicator is assigned an MPI Rank, an integer that uniquely identifies it in that communicator. At the beginning of execution, a default communicator gets created, called MPI COMM WORLD, which includes all the running MPI processes. A brief look on some examples of point-to-point and collective functions can be helpful for understanding their implementation described in the rest of this thesis.

The most commonly used point-to-point functions are **MPI\_Send** and **MPI\_Recv** [22] which have the respective signatures:

# int MPI\_Send(const void \*buf, int count, MPI\_Datatype datatype, int dest, int tag, MPI\_Comm comm) int MPI\_Recv(void \*buf, int count, MPI\_Datatype datatype, int source, int tag, MPI\_Comm comm, MPI\_Status \*status)

Both functions accept as arguments a pointer to a send/receive buffer, the datatype of the transferred elements (eg., MPI\_INT, MPI\_CHAR etc), the number of elements to be transferred (count), the MPI rank of the source or destination process, a communication tag and the respective communicator the transfer regards. These two function are both **blocking** functions which means that they will block until the user is able to use the buffers without worrying whether the communication has ended. However, MPI also offers non blocking functions like **MPI\_Isend** and **MPI\_Irecv** which return immediately and the user has to use other complementary functions like **MPI\_Wait** in order to determine whether they can reuse their buffers.

While reimplementing communication routines, one must take into account that the guarantees of the MPI standard must not cease to apply. For instance, it is guaranteed by the MPI Standard that a send function will always match with a receive of the destination rank of the same communicator, which denotes the sending process' rank as source and uses the same communication tag. Thus, the source/destination ranks, the communication tag and the communicator are the matching attributes of point-to-point functions. It is

also guaranteed that all messages of a specific rank, tag and communicator combination are going to get received by the receiver in the exact same order they were sent. Thus, the FIFO property is preserved in pointto-point communications. It is worth noting that receive functions do not need to denote the exact size of the data they want to receive but rather the maximum size they can receive. As a result, it is correct for a receive request to get matched by a send request of equal or smaller size. Receive requests can use wildcards like **MPI\_ANY\_SOURCE** and **MPI\_ANY\_TAG** in order to designate all other ranks and tags, respectively, as matching attributes. As one can observe, the MPI\_Recv function has one more argument of type **MPI\_Status**. MPI\_Status is an internal data structure whose contents may vary among different MPI implementations. This object consists of at least three integers which represent a)the source rank, b)the communication tag and c) the actual size of the transfer. During a communication, these integers take the appropriate values in order to enable the user to find out the aforementioned information after the communication ends.

An example of a collective MPI function is MPI\_Broadcast, which broadcasts a message sent by a root process to the rest of the processes of the communicator. All the processes must call the function with the exact same arguments (except for the buffer address) for the communication to be executed correctly.

####

Other MPI collective functions include MPI\_Reduce, MPI\_Scatter, MPI\_Gather [22]etc. each providing functionality in accordance to the user's need.

Any MPI program should invoke **MPI\_Init** or **MPI\_Init\_thread** before calling any other MPI routine. MPI also supports multi-threaded applications and different threading modes. A multi threaded MPI program may request one of the following thread support levels:

> MPI\_THREAD\_SINGLE Only one thread will execute.

➤ MPI\_THREAD\_FUNNELED The process may be multi-threaded, but only the main thread will make MPI calls

> MPI\_THREAD\_SERIALIZED The process may be multi-threaded, and multiple threads may make MPI calls, but only one at a time: MPI calls are not made concurrently from two distinct threads

▶ MPI\_THREAD\_MULTIPLE Multiple threads may call MPI at the same time, with no restrictions.

Some thread support levels infer some changes in the development of our implementation, which we also discuss in the next chapters.

#### 2.2 Packetizers and Mailboxes

As it will get more clear in the rest of the thesis, in order to achieve the correct matching between MPI requests, an MPI implementation should utilize a mechanism for the delivery of intermediate control messages required for the processes' synchronization. In order to achieve the delivery of such messages, our prototype uses special hardware blocks called *Virtualized Packetizers* and *Virtualized Mailboxes*. In this section, a very brief description of these blocks is provided.

Packetizers and Mailboxes have been designed for latency-critical operations and support the sending and receiving of messages respectively. More specifically, the prototype makes use of an environment in which all memory locations belong to a Global Virtual Address Space and can be addressed by network packets. A network packet is created by a Virtualized Packetizer and should denote a virtual address as its destination as well as specify a **protection ID** (PDID). The protection ID is process group-specific and is used by the hardware to safely check the initiator's access rights on particular locations of the virtual address space. Additionally, a network packet must contain a **node ID**, which constitutes the physical location of the node in which the packet's destination virtual address is contained. The virtualized packetizer offers a limited number of virtual interfaces (pages) that can be allocated to different threads and processes. In order to make use of that hardware block, a process may acquire a virtual interface of a packetizer from a kernel driver. The driver writes into a special hardware register the PDID of the requesting process and returns a virtual address which is mapped to the physical address of the packetizer page. Subsequently, that process is able to use the packetizer to target any location of the virtual address space or a virtual mailbox. At the time of writing, a packetizer can transmit messages of up to 64 bytes.

A virtualized mailbox is a hardware block responsible for receiving messages sent from a packetizer. Processes can again acquire mailboxes from a kernel driver which associates each virtual mailbox interface with the PDID of the corresponding process group. When a packetizer sends a message to a virtualized mailbox, the receiving hardware checks the packet's PDID and tries to match it against that of the virtual mailbox. A user can poll for new arrivals in their mailboxes by reading from a virtual address that has been memory-mapped to the physical address of their virtualized mailbox. It's worth noting that the described network primitives guarantee the FIFO delivery of control messages. This means that all messages sent from a process A will get received by a process B in the same order they were sent. This fact plays a crucial role in preserving MPI's FIFO property described in section **2.1**

#### 2.3 RDMA Engine

While packetizers and mailboxes are sufficient for the transmission and receiving of short and low latency control messages, for large data transfers the prototype utilizes a simple virtualized RDMA engine, with coordinated units running at the sending and receiving endpoints. The RDMA engine provides an effective multi-path transport based completely on hardware allowing to bypass the kernel stack on I/O operations. An RDMA operation transfers a message between two locations of the aforementioned Virtual Address Space: the source, which in our prototype is always local to the sending point's engine that will realize the transfer, and the destination, which is local to the receiving point's engine. In order to signify the end of the transfer to the receiving point, the DMA engine delivers an additional notification message to an arbitrary virtual address local to the receiver, called **notification address** in the rest of the thesis. By polling on the notification data (i.e., the contents of the notification address), a receiving process is able to determine the end of an incoming transfer. The RDMA engine is used in this work for the transfer of large MPI messages it offers high throughput and requires no copies at all. For converting local buffer addresses to virtual Exanet addresses within the Global Virtual Address Space, special routines are provided that make use of a DMA offset, different for each node. More information about the DMA related routines is available in the next section.

#### 2.4 User Level Communication Libraries

For the utilization of the hardware blocks described in 2.2 and 2.3, a user-space API that allows user-level access to them has been deployed. As a result, this communication library is widely used in this work. By making use of that API, a process is able to attach a virtual interface of the mailbox and packetizer that reside on the local compute node as well as acquire all the relevant information regarding the Ids and DMA offsets of the node. More precisely, the MBOX\_ATTACH() and dma\_alloc\_chan(); `routines are used in order to attach a mailbox/packetizer interface and allocate a DMA protection domain respectively. Both functions return handles which can be used by the user in order to initiate DMA transfers and poll for new messages in mailbox. Additionally, functions like get\_exanet\_offset(dma\_channel), the MBOX\_GET\_PROTECTION\_ID() and getBoardID() return the aforementioned node specific DMA offsets and IDs. Each node should be aware of this information regarding any other node it wishes to transfer data to. When a process has obtained the Protection ID and node ID of another node, it can derive the remote node's Mailbox Address and, subsequently, use the packetizer to send messages to its Mailbox by calling

MBOX ENQUEUE 64B (address, message) function of the User Level API. Respectively, a process is able read itsmailbox for incoming messages using dequeuing functions like to \_MBOX\_TRY\_DEQUEUE\_64B and providing the mailbox handle returned from MBOX\_ATTACH. It's worth mentioning that attaching functions like MBOX ATTACH and dma alloc chan are the only functions of the API that involve the kernel. As far as the RDMA engine is concerned, a user can initiate DMA transfers without requiring kernel intervention by using dma\_init\_write(dma\_handle\_t \*handle, void \*src, void \*dst, long size, void \*notif\_addr, uint64\_t \*notif\_data) and passing to it as arguments the DMA handle returned by **dma\_alloc\_chan()** as well as the source and destination buffers, the size of transfer in bytes, the notification address of the receiver and the notification data to be written to the remote notification address. It should be noted that the destination buffer address and notification address should be valid Exanet addresses returned from the function dma\_get\_exanet\_addr(void \*addr, void \*offset); which transforms a local address (addr) to an Exanet address using the receiving node's DMA offset. that initiates the DMA transfer, can determine its completion state by calling The process dma\_test\_transfer(dma\_transfer\_t \*transfer); and passing to it, as argument, the handle returned by dma\_init\_write. The receiver can also determine the end of the transfer by polling the contents of the notification address.

#### 2.5 The HPC Prototype

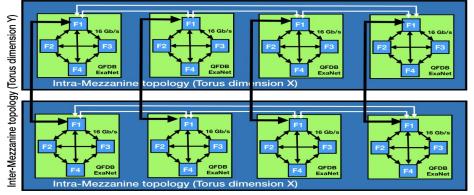

In the scope of the ExaNeST project, a new HPC cluster has been deployed in the CARV Laboratory of FORTH [23], which utilizes the network primitives described in the previous sections and gets used for the testing and evaluation of our implementation in this thesis. At the time of writing, the prototype consists of 8 mezzanines, each one of them carrying 4 Qaud FPGA Daughter Boards (QFDBs) for a total of 128 FPGAs.e FPGAs are Xilinx Zynq Ultrascale+ devices (ZCU9EG), featuring four (4) ARM-A53 [31], 16-GByte DDR4 each. As a result, our prototype contains in total 512 ARM v8 processors. The platform supports two different networks. The first one being a custom packet-based hierarchical interconnect realized over high speed serial links, developed by FORTH and INFN [24] called Exanet, which is used by the primitives described in Sections 2.2. and 2.3. The second network our prototype supports is a common 10G Ethernet interface. Within a QFDB, there is an all-to-all connectivity among all four of its FPGAs (called F1, F2, F3 and F4) through the Exanet interconnect offering a link capacity of 16 GB/s. In addition, all QFDBs are connected with each other in a 3D Torus topology using 10 GB/s serial links. Depending on the position of two FPGAs in the 3D Torus, a different number of network hops may exist between them. The number of hops between two FPGAs can play a crucial role in latency as it is shown in the next chapters. Figure 2.1 depicts an example of the prototype's 3D Torus topology. QFDBs are illustrated as green boxes which contain 4 FPGAs interconnected through 16 GB/s links while the links connecting different QFDBs of the same mezzanine as well as different mezzanines are depicted as white and black arrows respectively. Both types of inter QFDB links have a capacity of 10 GB/s as stated.

Figure 2.1: HPC prototype's Example topology

#### 2.6 Read-based Exanet MPI Implementation

In order to exploit the described architecture and network primitives for the execution of HPC applications, an MPI implementation, prior to our work, was deployed. That MPI implementation is based on **emulated DMA reads** in order to transfer large messages while it uses the packetizer to transfer messages of size of less than 40 bytes between two MPI processes. This implies that the implementation supports two different kinds of MPI Communication protocols; The **long rendezvous protocol** and the **eager protocol**. The former protocol is used for the transfer of large messages and the eager protocol is restricted to small messages that can "fit" inside a packetizer message.

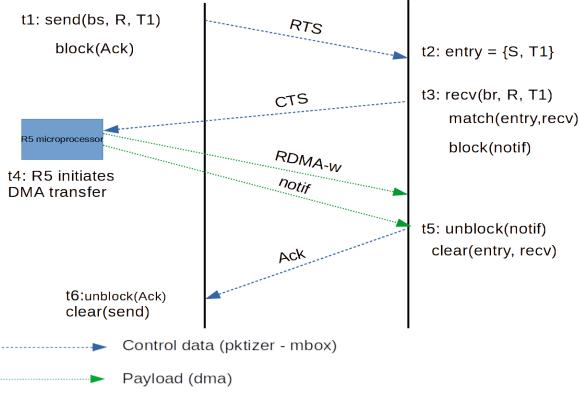

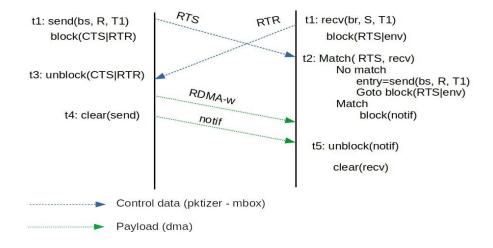

The long rendezvous protocol relies exclusively on sender initiation. More precisely, a sending MPI process is able to initiate the communication by transmitting an **RTS** (Request to Send) control message to the receiving process, notifying it about the posting of a send MPI primitive (eg. MPI Send) on its side. The RTS control message should contain the address of the send buffer, the size of transfer as well as the matching attributes of the send request (tag, MPI\_Rank of the sender) and the ID of the communicator). At this point, it should be mentioned that each MPI process preserves internal data structures that are used to store Posted and Received MPI requests. The **Posted MPI Requests** data structure regards communications posted by the process itself (by MPI Send) while the **Received MPI Requests** data structure regards incoming control messages emerged from communications posted by other processes. For instance, a sending process should insert a new object on its Posted MPI Requests structure as soon as it calls MPI Send. The receiving process that receives the RTS control message from the sender should search its Posted MPI Requests data structure for an already posted matching receive request. If no matching receive request exists yet, the receiving process stores the RTS message in the Received MPI Requests for future matching. In either case, when a receive requests gets matched by a matching RTS, it transmits a CTS (Clear to Receive) control message targeting an R5 AMR microprocessor [32] in the sender's side and instructing it to perform a DMA write using the send buffer contained in the RTS message as source buffer and designating the receiver's receive buffer as destination. Through the CTS control message, the notification address of the receiver is also conveved. As soon as the R5 microprocessor receives a CTS message it initiates a DMA write and informs the receiver about its completion by writing into its notification address. Since the DMA write is actually initiated by the receiver, we call that operation an emulated read operation since actual DMA reads are not supported by our RDMA engine. In addition, since the sender process did not initiate the write itself, it cannot determine whether it is completed without receiving an acknowledgment control message from the receiver. As a consequence, the receiving process transmits an Ack control message informing the sender about the end of the emulated read.

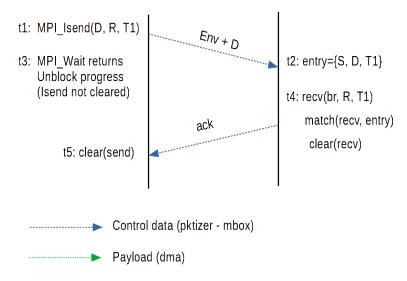

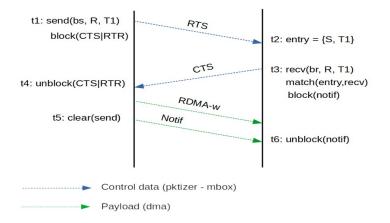

In Figure 2.2, a scenario where the long rendezvous protocol is used is illustrated. We assume that the left vertical line depicts the execution of an MPI process with rank  $\mathbf{S}$  while the right line depicts the execution of the process with rank  $\mathbf{R}$ . At timestamp t1, the sending process invokes a blocking sending primitive (e.g., MPI Send) denoting rank R as destination rank, T1 as the communication tag and bs as the send buffer. As a result, it inserts a new request into the Posted MPI Requests data structure, issues an RTS control message that contains the matching attributes of the request and the address of the send buffer and block its progress waiting for an Ack message. At t2, the receiving process receives the RTS message and due to the fact that there is no receive request posted to match it yet, it stores it into the Received MPI Requests data structure (entry = {S, T1}). At t3, the receiver calls a receive MPI primitive (e.g., MPI\_Recv) denoting rank S as source rank, T1 as communication tag and **br** as receive buffer (for simplicity, communicator ID is omitted. The process searches its Received MPI Requests and it manages to perform a match with the RTS stored at t2. Consequently, the receiving process transmits a CTS control message to the sender's R5 microprocessor instructing it to perform a DMA write using be as source and br as destination buffer. Afterwards, it blocks waiting for a change in the contents of the notification address that will indicate the completion of the transfer. At  $t_4$ , the microprocessor initiates the transfer and at  $t_5$ , the notification arrives. This fact makes the receiver unblock its progress and transmit an Ack message to the receiver notifying about the end of the emulated read. The Ack message also contains the request's matching attributes in order to successfully match the send request at the sender's side. At t6, the sender receives and matches the Ack message to the send request and

unblocks its progress. Ultimately, both processes clear the respective requests and the send and receive MPI primitives return.

Figure 2.2 Long Protocol of the Read Based Exanet MPI

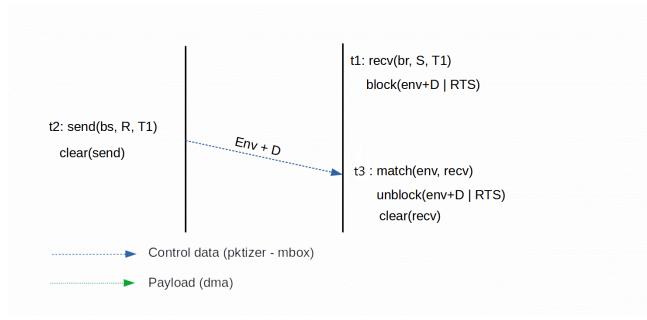

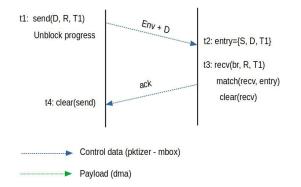

The eager protocol also relies on sender initiation and it is much simpler as it does not involve DMA transfers at all. A sending process that performs a send of size less than 40 bytes can immediately transmit the message to the receiver without requiring any rendezvous or synchronization beforehand. Instead, it piggybacks the data to get transferred in a packetizer message which also includes the request's matching attributes in order to get successfully matched with a receive request of a receiver. This new control message is called **Env+D** (Envelope and Data, where **Envelope** is another name used in scientific literature for the matching attributes of a message) Additionally, the sending process doesn't need to insert any request to the Posted MPI Requests since eager sends do not need to get matched by Ack messages.

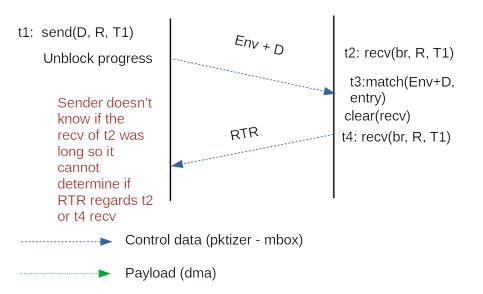

Figure 2.3 illustrates an example of eager communication in the read-based protocol. The receiving process posts a blocking receive request at t1 and denotes S as the source rank and T1 as the communication tag. After inserting the request into the Posted MPI Requests data structure, the process blocks its progress waiting for an RTS or Env+D control message. At t2, the sender posts an eager send and immediately transmits the Env+D message that includes as payload the contents of its send buffer and returns without inserting any object in the Posted MPI requests. At t4, the receiving process receives the Env+D and matches it against the receive posted at t1. Subsequently, it unblocks its progress, copies the payload of the Env+D message to its receive buffer, it clears its state and returns.

Figure 2.3 Eager protocol of the Read Based Exanet MPI

As one can notice, the eager protocol offers optimal performance since it constitutes the simplest form of communication possible between two MPI processes. Moreover, since it regards messages of small size (less than the size of a packetizer message, which is 64 bytes), the memory copy (from the Env+D message's payload to the source buffer of the receiver) it requires has not noticeable latency.

However, the long rendezvous protocol has some serious disadvantages. First of all, because of the fact that it is based on an emulated read, the receiver must inform the sender about the end of the transfer by issuing a control message (i.e., Ack) back to the sender. In addition, the inability of the receiver to initiate MPI communication itself does not let us exploit cases where the receive request gets posted earlier than a matching send. Instead, the receiving process has to wait for the sender to initiate the communication with the use of an RTS control message, thus not taking advantage of the intermediate waiting time. In the next chapter, we present our attempt to develop a write-based version of the Exanet MPI, addressing the drawbacks of the readbased variant.

## Design and Implementation of the Write-based Exanet MPI Protocol

Designing and implementing the write-based variant of Exanet MPI was a highly experimental process which resulted to the development of different variants of the write-based protocol itself. In this chapter, the basic variants of the protocol that emerged from this work are getting described and partly evaluated in an attempt to underline our thinking process towards the final version of the write-based protocol. Additionally, several details regarding the implementation of certain aspects of the protocol, common to all of the variants are getting presented.

#### 3.1 Designing a preliminary sender and receiver initiated write-based protocol

## 3.1.1 Designing a preliminary sender and receiver initiated write-based long protocol

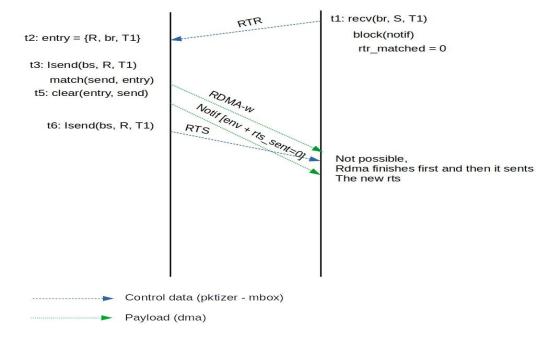

As already mentioned in the previous chapters, an important weakness of the read-based variant of Exanet MPI is the inability of a sending process to become aware of the end of a DMA write since the write gets initiated from the receiver's side in an attempt to emulate a DMA read operation. Thus, an acknowledgment (ACK) control message sent from the receiver is the sole way of the sender determining the end of the DMA transfer which is expected to cause measurable overhead. For that reason, one of our initial goals was to eliminate the need of that control message by rendering the sending process the initiator of the DMA write. In addition, we aimed to exploit the new DMA feature of delivering the end of a transfer to an arbitrary remote address of the receiving process' address space. More specifically, as described in Section 2.2, he DMA engine of the developing HPC prototype, supports notifying the receiver that a DMA transfer is over by performing an additional write to a remote address, called notification address. Subsequently, the receiving process can determine the end of the DMA data transfer by polling on the notification address and waiting for a change in its contents. Another one of our main motives for working towards a write-based protocol of the Exanet MPI is the fact that the preexisting read-based protocol relies exclusively on sender-initiated communication. This renders the read-based protocol unable to take advantage of scenarios in which the receiving process posts a receive request (e.g., MPI Recv) before a matching send request (e.g., MPI Send) gets posted by a sending process. This kind of early receive posting will be denoted in the rest of this thesis as **fast receive**. In such a case, in the read-based protocol, the receiving process cannot initiate the communication by advertising its receive buffer and local notification addresses to the sender but instead it has to wait for an RTS control message from the sending process. As a consequence, the matching happens only in the receiving process' side. In order to address that drawback of the read-based protocol and allow the initiation of the communication from the receiving process's side, a new type of control message was introduced called Request-to-Receive (RTR). With the use of an RTR control message the receiver is able to advertise its receive buffer and local notification address to the sending process (just like with a CTS message) as soon as it posts its receive request., asynchronously, without waiting for the posting of a matching send as it happens in the read-based implementation. In addition to the DMA related information, an RTR control message also contains all the necessary matching attributes thus enabling the request matching to take place on the senders' side as well. After receiving an RTR message, a sender is aware of all the necessary information required to perform a DMA write operation without the need for further synchronization. In such a case, however, due to the absence of the RTS conrol message in the communication, the receiving process may be unable to fill its MPI\_Status struct

because it misses essential information like the tag of communication (in case MPI\_ANY\_TAG was used) or the size of the transfer. Additionally, without a control message from the sender, the receiver is not able to mark its receive request as matched before the communication ends which poses the risk of it becoming mistakenly matched by a future RTS message regarding another receive request with the same matching attributes. The aforementioned reasons render the use of another control message, called Envelope (Env), necessary. This type of message contains the information required to fill the receiver's MPI\_Status struct and gets transmitted from the sender before the DMA transfer takes place. The use of an Envelope control message may seem to infer the same cost as the sender initiated scenario but in reality, fast receives still outperform the sender initiation used in the read-based protocol since they allow asynchronously transferring the matching iand DMA related information to the sender before it posts its send request. As a result, a typical long writebased protocol should contain the following control messages:

- **RTS** (Request to Send): The RTS control message constitutes the message containing all the attributes used to match the send request with a matching receive request at the side of the receiver as well as the envelope information needed in order to fill the MPI\_Status struct of the matched receive (ie. Rank of the sender, communication tag, size of transfer). It gets transmitted from the sending process to the receiver and it is used to initiate the communication between them.

- **CTS** (Clear to Send): The CTS control message conveys, besides the necessary matching information, the address of the receive buffer which will be the destination of the sender's DMA write as well as the local notification address for that specific write. This message always gets transmitted in response to an already received RTS message and it indicates that receiver is ready to receive DMA data.

- **RTR** (Request to Send): The RTR control message contains the same DMA information as the CTS message. Unlike CTS, a receiving process issues an RTR message when no matching RTS has arrived at the time the receive request gets posted. It is, thus, a message used to initiate communication from the receiver's side.

- Env (Envelope): The Env control message contains the essential envelope information required for the completion of the MPI\_Status struct. It gets issued by the sender just before the DMA transfer unless a RTS control message has already been issued for the same receive request before.

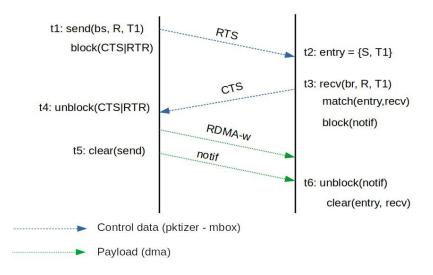

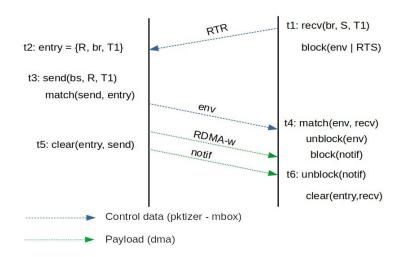

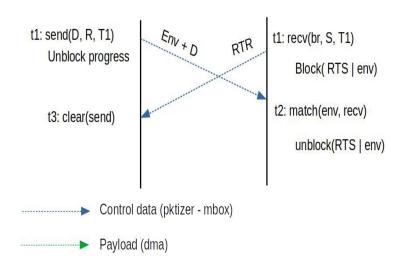

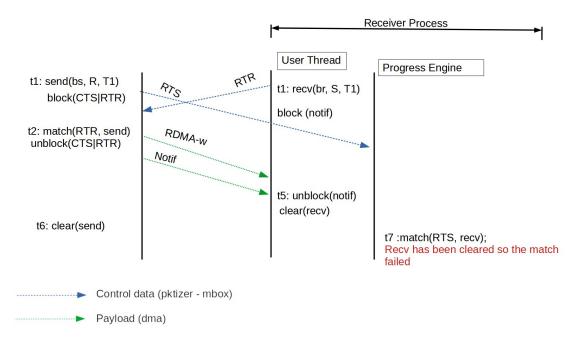

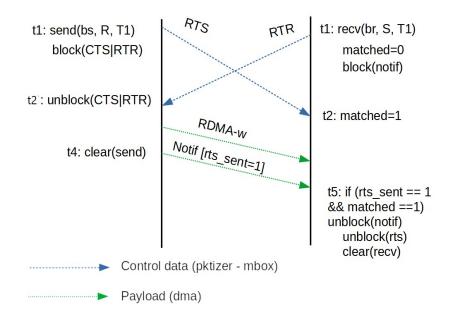

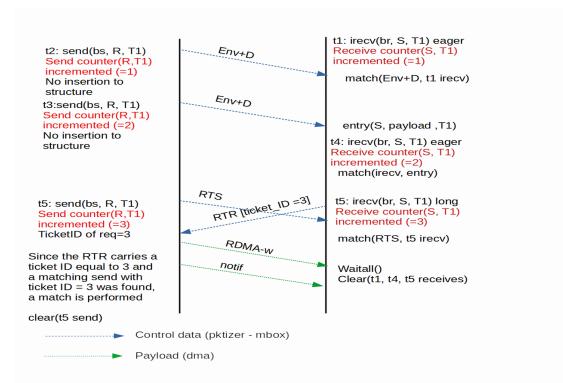

In Figure 3.1 the case where the sender arrives first at a matching send-receiver pair is presented. At t1, the sender posts a send request designating bs as a source buffer and denoting R as the destination rank. The corresponding communication tag is denoted as T1. Since no matching receive request exists in its Received MPI Requests, the sender posts a new request object in the Posted MPI requests and issues a request-to-send (RTS) message to the receiver specifying the communicator, tag and desired size of the transfer. It is assumed that the send request emerged from a blocking MPI primitive like MPI Send. For that reason, the sending process blocks its execution waiting for either a matching CTS or RTR message. After receiving the RTS message, the receiver temporarily stores that received send request to an internal data structure used to store incoming requests at t2 (entry =  $\{S, T1\}$ ). At t3>t1, the receiver posts a matching receive request and after matching it against the formerly received send request, it sends back a clear-to-send (CTS) message specifying the destination buffer (br) where it wishes to receive the data along with the virtual address where it will expect a notification of the DMA write's completion. We assume that the receive request emerged from a blocking MPI primitive like MPI Recv, thus the receiving process blocks its execution while waiting for the DMA notification. Upon receiving the CTS control message, the sender uses the information that message contains in order to match it with the send it posted at t1. When the CTS message gets successfully matched, the sending process writes the data to br along the corresponding notification to the notification address. Note that since the DMA is initiated from the sender's side, the sender knows when the transfer is complete and does not require an acknowledgment back from the receiver, unlike the read-based protocol. At the end completion of the communication, both processes clear the send and receive requests from their respective data structures. More information regarding the mechanisms used in order to receive control messages as well as the

data structures necessary for storing MPI communication requests are available in the next chapters.

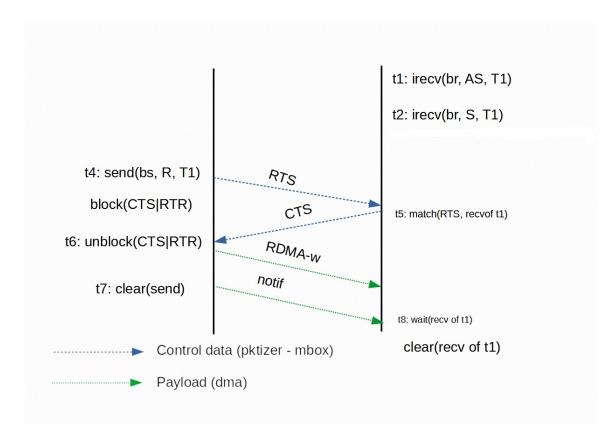

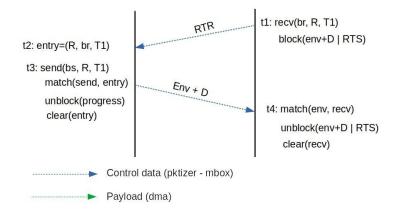

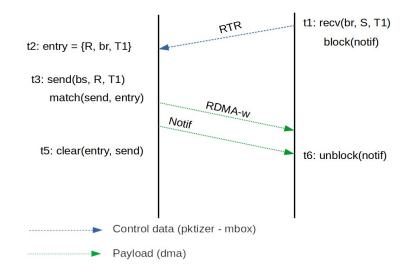

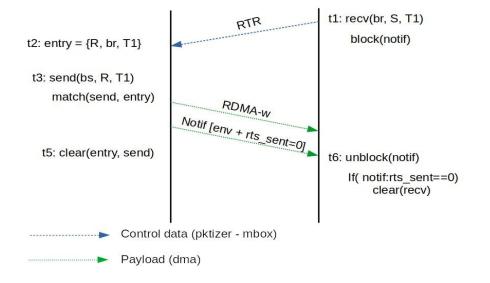

In the scenario illustrated in Figure 3.2 the receiver posts its receive request at t1 before the sending process posts its send request. Consequently, the receiving process, having received no matching RTS yet, initiates the communication by transmitting an RTR control message to the sender advertising the destination buffer (br)and the notification address, specifying the communicator, the communication tag and inserting a new receive request in its Posted MPI Requests denoting S as the source rank. After the issuing of RTR, the receiver blocks its progress waiting for either a matching Env or RTS message and subsequently for a change in the contents of the notification address. The sending process, after receiving the RTR message at t2, stores a specific receive request in its internal data structure regarding incoming requests since there is no posted send to match it yet. At t3, a matching send gets posted by the sender. By matching its send request with the previously received RTR successfully, the sender is aware of the destination buffer and notification address of the receiver and performs the DMA write operation after issuing the necessary Env message. As a result, the receiving process unblocks its progress after successfully receiving the Env message and observing the write the sender performed on the notification address' data. Both processes, ultimately, clear their respective requests.

Figure 3.1: Sender initiated communication in the write-based Exanet MPI

Figure 3.2: Receiver initiated communication in the write-based Exanet MPI

As it becomes apparent, the presented write-based long protocol offers more flexibility and timing exploitation capabilities since it allows the initiation of the communication from both the sender's and receiver's side. This fact renders the case where a receive request gets posted first nearly optimal, since the synchronization needed since the posting of a matching send request gets minimized. However, the possibility of both sender and receiver initiation for the same transfer can give rise to some complications which we examine in the next paragraphs.

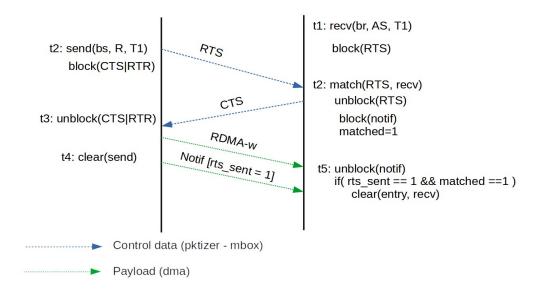

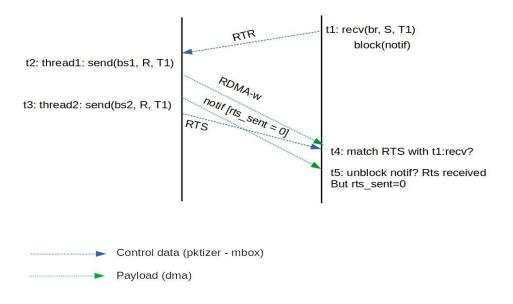

At this point, we should remind that the MPI standard allows the use of a wildcard called MPI\_ANY\_SOURCE at the place of the source rank of a receive request, designating any rank of the denoted communicator as a possible sender of the expected message. This fact obliges to take into account several scenarios both in the design as well as the implementation of the write-based protocol. As it is easily conceivable, in the case where an MPI receive request gets posted earlier than the matching send request, it is not feasible to issue RTR messages towards all the other ranks of the communicator. Even in small communicators, sending the same RTR control message to all other ranks will most likely lead to an erroneous result since more than one sending rank may attempt to perform the DMA transfer to the same buffer. In addition, there is no way for each of the receivers of that RTR message to know which of them has received it first. As a consequence, the receiver initiation gets unavoidably suspended while receive requests that use MPI\_ANY\_SOURCE remain active in an MPI program.

Figure 3.3: MPI\_ANY\_SOURCE receiver initiation suspension

In Figure 3.3 the case of a receiver posting its receive request designating MPI\_ANY\_SOURCE as source is depicted. Despite the fact that the receiver posted its receive request before the posting of the matching send request by the sender, it cannot initiate the communication with the issuing of an RTR control message due to the aforementioned complications. Instead, it inserts the receive request in its internal data structure regarding posted requests and waits for a matching RTS. On the sender's side, the progress is identical to the one depicted in Figure 3.1 where the sending process, being unaware of any matching posted receive request,

attempts to initiate the communication by transmitting an RTS control message to the receiver. It is worth noting that the RTS control message also conveys the MPI Rank of the process initiating the communication, thus rendering the receiver able to log that information in the MPI\_Status struct that regards the specific receive request. After successfully matching the received RTS message, the receiver issues a response CTS message thus advertising the necessary DMA information to the sender which in turn performs the DMA write. The communication ends in the exact same way it was illustrated in Figure 3.2 with both processes unblocking and clearing their state. At this point, it must also get clarified that the receiver initiation suspension does not regard only the receive request that uses MPI\_ANY\_SOURCE but rather **all** receives that get issued while MPI\_ANY\_SOURCE is still in use.

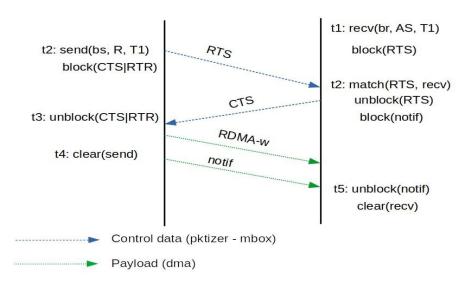

Figure 3.4 presents an example of a receiving process posting two non blocking receive requests at t1 and t2 respectively. The first receive request makes use of MPI\_ANY\_SOURCE while the second denotes rank S as the source rank. As we observe, both requests do not issue RTR messages, thus, RTR suspension is not limited to only the first request. If the second receive request did issue an RTR message, there would be the risk of the sender matching that RTR upon posting and perform the DMA write to the buffer of the second receive request and in that way violating the FIFO guarantee of the MPI Standard.

Figure 3.4: MPI\_ANY\_SOURCE receiver initiation suspension, non blocking receives

Another complication that may arise in a both receiver and sender initiated write-based protocol is the possible concurrent posting of both the send and the receive requests by the respective processes. In such a scenario, both of the processes issue their initiatory control messages (i.e., RTS, RTR). However, both type of messages get treated like an Env and CTS message respectively. More precisely, a receiver which has already sent an RTR message and receives a matching RTS will first check whether that RTS matches an already posted receive request before treating it as an attempt to initiate a new communication. If there is already a matching receive posted, then the receiver uses the information included in the RTS message in order to fill the MPI\_Status struct and discards that RTS. Similarly, a sender which has already initiated the communication

will treat an RTR control message, which matches that request, as a CTS message and will not store a new receive request in its internal data structure. The described case is illustrated in Figure 3.5. This scenario is pretty similar to the receiver initiated communication depicted in Figure 3.2 with the difference that the RTS message substitutes the Envelope message.

Figure 3.5 Concurrent Receiver and Sender initiation

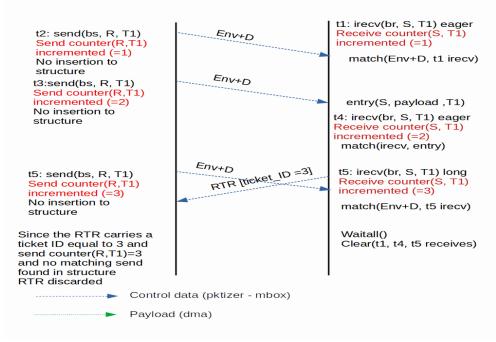

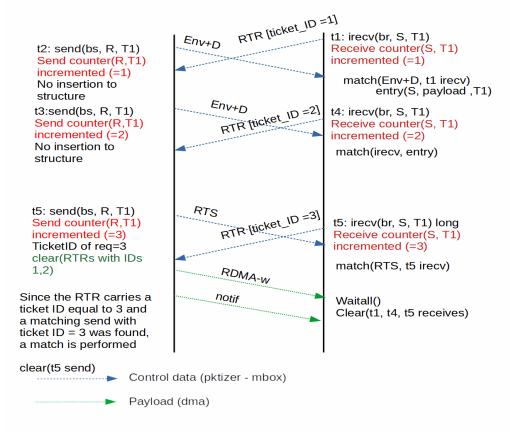

## 3.1.2 Designing a preliminary sender and receiver initiated write-based eager protocol

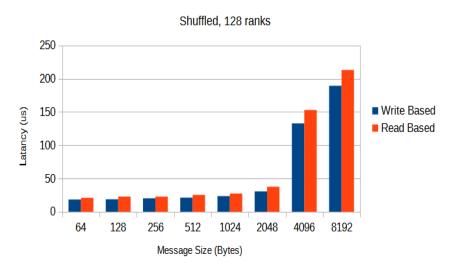

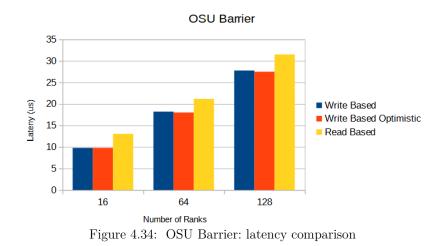

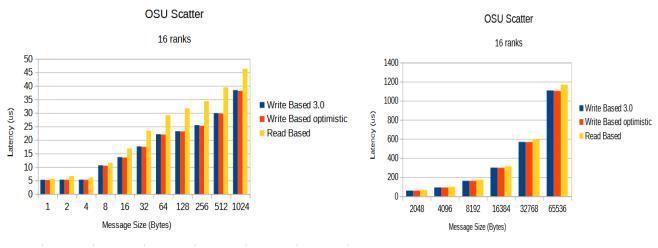

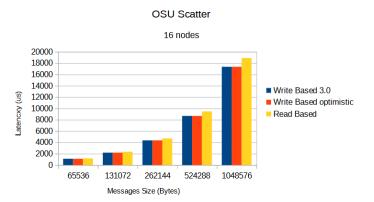

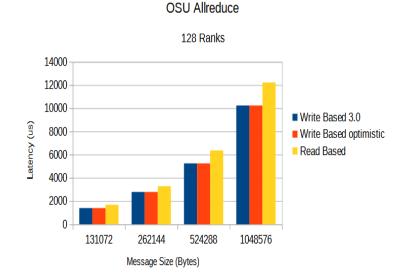

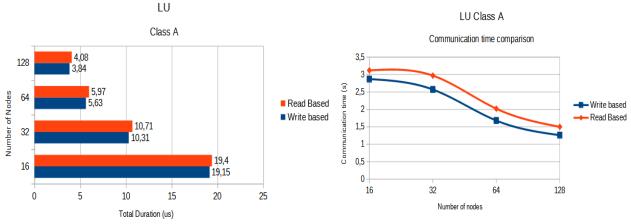

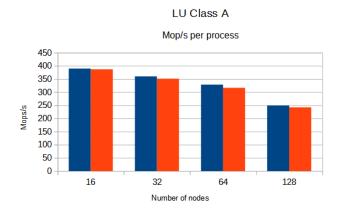

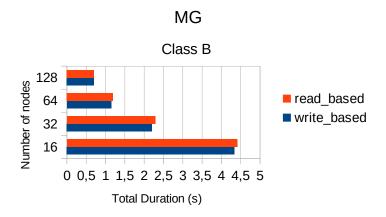

As mentioned in 2.5, the read-based protocol uses an eager protocol in order to transfer messages of up to 40 bytes (a packetizer message has a maximum size of 64 bytes out of which, 24 bytes constitute the messages Envelope). The write-based and the read-based protocol coincide in this regard. For such small messages we choose to exploit the low latency mechanisms of the mailbox and packetizer hardware blocks described in 2.2 and, as a consequence, avoid the startup latency of the DMA engine. For that reason, an eager message gets packed as *payload* together with envelope data into a new control message call Envelope and Data (Env+D). This message gets issued by the sending process and has the receiving process as destination. Respectively, a receiving process that expects to receive a message smaller than 40 bytes should have no need to issue an RTR message since it useless for it to advertise DMA specific information as the eager communication takes place exclusively through the use of control messages. However, in the write-based eager protocol another complication arises from the fact that receiver initiation is also supported. As it is already mentioned in this chapter, the MPI standard allows the matching of receive and send requests of different sizes. More specifically, a receive request that regards a specific size may correctly match with a send request that regards equal or smaller size in bytes which means that a long receive (i.e., a receive request that expects a transfer of size bigger than 40 bytes) can match with an eager send. This fact renders the sending process issuing an eager send unable to know whether an incoming matching RTR message matches that eager send request or should match a future send request. Such a scenario is depicted in Figure 3.6 where the sender performs an eager sendat t1 while the receiver posting an eager receive at t2 doesn't issue a control message. This implication made us to initially allow eager receives to also issue RTR messages, even if they don't need to advertise DMA information, in order to prevent mismatches.