**University of Crete Department of Physics**

**Institute of Electronic Structure and Laser**

# STUDY AND OPTIMIZATION OF FIELD EFFECT TRANSISTORS BASED ON GRAPHENE

# **Triantopoulos Konstantinos**

Thesis for the degree of Master of Science in Microelectronics- Optoelectronics

Academic advisor: Prof. Georgakilas Alexandros Thesis supervisor: Dr. Deligeorgis Georgios

> Heraklion, June 2016

| A  | Acknowledgment                                             | 7  |

|----|------------------------------------------------------------|----|

| П  | <b>Ι</b> ερίληψη                                           | 8  |

| A  | Abstract                                                   | 9  |

| 1. | . Graphene                                                 | 11 |

|    | 1.1 Introduction                                           | 11 |

|    | 1.2 Graphene Structure                                     | 11 |

|    | 1.3 Density of States                                      | 12 |

|    | 1.4 Graphene Synthesis Methods                             | 14 |

|    | 1.4.1 Mechanical exfoliation                               | 14 |

|    | 1.4.2 Graphitization of silicon carbide SiC                | 15 |

|    | 1.4.3 Chemical vapor deposition                            | 15 |

| 2. | Metal-Graphene junction                                    | 16 |

|    | 2.1 Introduction                                           | 16 |

|    | 2.2 Metal-Semiconductor Contacts                           | 16 |

|    | 2.3 Conduction Mechanisms for Metal/Semiconductor Contacts | 18 |

|    | 2.4 Contact resistance                                     | 19 |

|    | 2.5 Definition of contact resistance                       | 20 |

|    | 2.6 Measurement Techniques                                 | 21 |

|    | 2.6.1 Two-contact Two-terminal Method                      | 22 |

|    | 2.6.2 Multiple – Contact Two-Terminal Methods              | 24 |

|    | 2.6.3 Transfer length Method                               | 25 |

|    | 2.6.4 Four-Terminal Contact Resistance Method              | 31 |

|    | 2.6.5 Six-Terminal Contact Resistance Method               | 33 |

|    | 2.7 Comparison of measurement techniques                   | 34 |

|    | 2.8 Carrier transport from metal into graphene             | 34 |

|    | 2.9 The origins of metal-graphene contact resistance       | 36 |

|    | 2.10 Optimization of metal-graphene junctions              | 36 |

|    | 2.10.1 Metal choice                                        | 36 |

|    | 2.10.2 Cleaning methods                                    | 39 |

|    | 2.10.2.1 Thermal annealing                                 | 39 |

|    | 2.10.2.2 Plasma Cleaning                                   | 40 |

|    | 2.10.2.3 Ultraviolet/ozone treatment                       | 41 |

|    | 2.10.2.4 CO2 cluster cleaning                              | 42 |

| 3. | Dielectrics                                                         | 43 |

|----|---------------------------------------------------------------------|----|

|    | 3.1 Introduction                                                    | 43 |

|    | 3.2 Definition of dielectrics                                       | 43 |

|    | 3.3 Parallel plate Capacitor                                        | 44 |

|    | 3.4 Dielectric strength                                             | 48 |

|    | 3.5 Dielectric breakdown in solids                                  | 48 |

|    | 3.5.1 Intrinsic breakdown or Electronic breakdown                   | 48 |

|    | 3.5.2 Thermal breakdown                                             | 49 |

|    | 3.5.3 Insulator Aging                                               | 49 |

|    | 3.6 High-k materials                                                | 50 |

|    | 3.6.1 From SiO <sub>2</sub> to high- k dielectrics                  | 50 |

|    | 3.6.2 Candidate high- k materials                                   | 50 |

|    | 3.7 Leakage current                                                 | 52 |

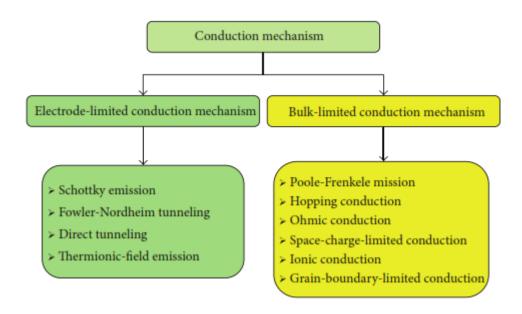

|    | 3.7.1 Conduction mechanisms in dielectric films                     | 52 |

|    | 3.8 Deposition of Dielectric Thin Films                             | 56 |

|    | 3.8.1 Atomic Layer Deposition (ALD) of Dielectric Films on Graphene | 56 |

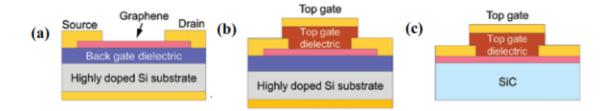

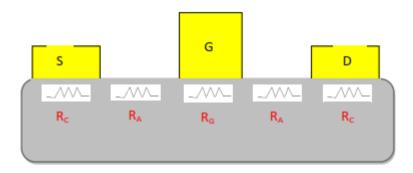

| 4. | Graphene Field Effect Transistors                                   | 58 |

|    | 4.1 Structure of a GFET                                             | 58 |

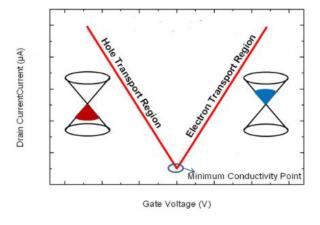

|    | 4.2 Electric field effect in graphene                               | 59 |

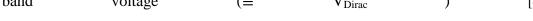

|    | 4.3 Current- Voltage characteristics of GFETs                       | 60 |

|    | 4.4 Important parameters of GFETs                                   | 63 |

|    | 4.4.1 Transconductance                                              | 63 |

|    | 4.4.2 Quantum Capacitance                                           | 63 |

|    | 4.4.3 Mobility in Graphene                                          | 63 |

|    | 4.4.3.1 Extraction of mobility in the GFETs                         | 65 |

| 5. | Micro fabrication                                                   | 68 |

|    | 5.1 Lithography                                                     | 68 |

|    | 5.2 Photo-resist coating                                            | 68 |

|    | 5.3 Mask generation and image transfer                              | 69 |

|    | 5.4 Etching.                                                        | 69 |

|    | 5.4.1 Wet chemical etching                                          | 69 |

|    | 5.4.2 Dry etching                                                   | 70 |

|    | 5.4.2.1 Chemical dry etching                                        | 71 |

|    | 5.4.2.2 Physical dry etching                                        | 71 |

| 5.4.2.3 Reactive Ion etching                        | 72  |

|-----------------------------------------------------|-----|

| 5.4.2.4 Ion Beam Milling                            | 72  |

| 5.5 Dry etching parameters                          | 72  |

| 5.6 Thin film deposition                            | 73  |

| 5.6.1 Thermal evaporation                           | 73  |

| 5.6.2 Sputtering as a physical deposition technique | 73  |

| 5.6.3 Chemical vapor deposition                     | 74  |

| 5.6.4 Plasma enhanced chemical vapor deposition     | 74  |

| 5.6.5 Electrochemical deposition                    | 74  |

| 5.6.6 Electron beam evaporation                     | 75  |

| 5.6.7 Atomic layer deposition                       | 75  |

| 5.7 Rapid Thermal Annealing                         | 76  |

| 6. Experimental                                     | 77  |

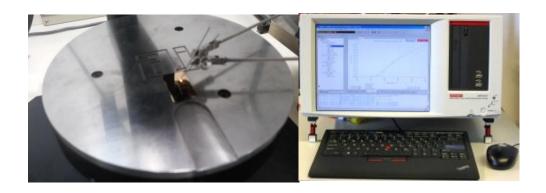

| 6.1 Metal-graphene contacts (Part I)                | 77  |

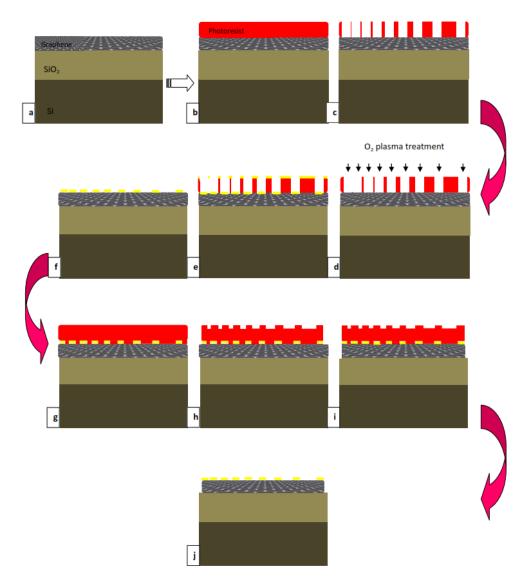

| 6.1.1 Sample preparation                            | 77  |

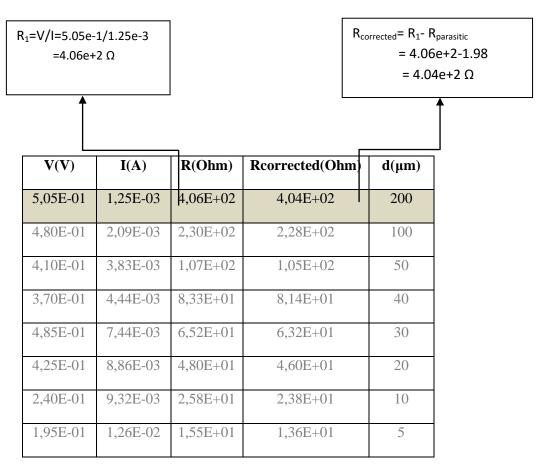

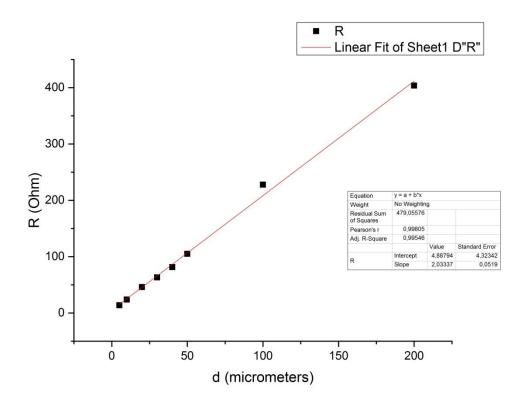

| 6.1.2 Data analysis                                 | 79  |

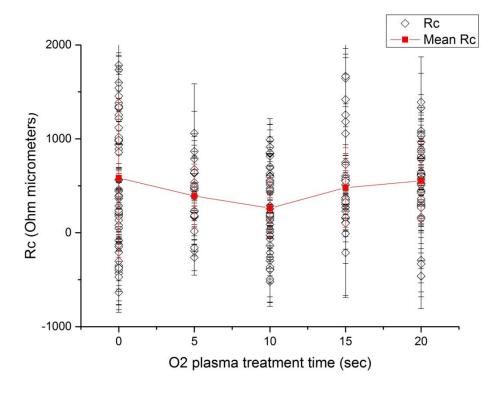

| 6.1.3 Results and discussion                        | 82  |

| 6.1.4 Conclusions                                   | 89  |

| 6.2 Dielectrics (Part II)                           | 91  |

| 6.2.1 Sample preparation                            | 91  |

| 6.2.2 Data analysis                                 | 92  |

| 6.2.3 Results and discussion                        | 95  |

| 6.2.4 Conclusions                                   | 103 |

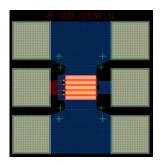

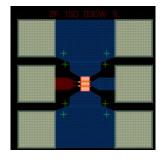

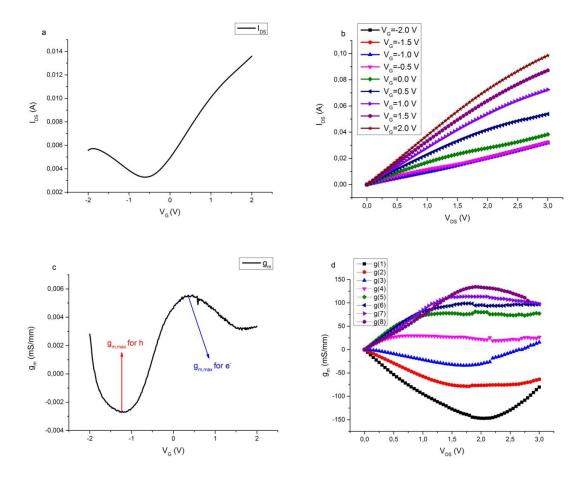

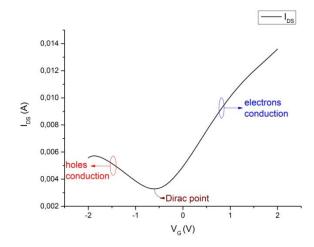

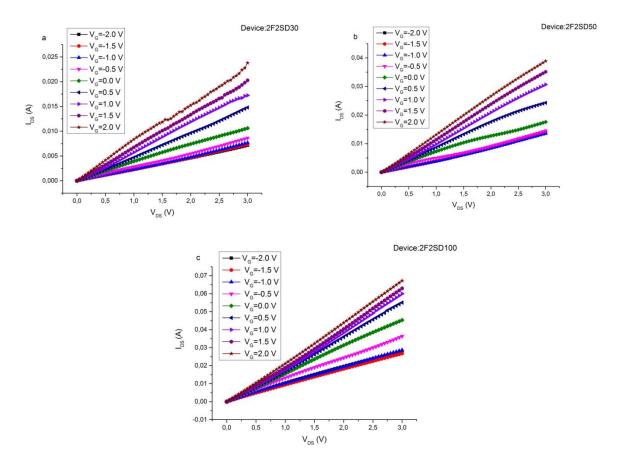

| 6.3 Graphene Field-Effect Transistors (PART III)    | 104 |

| 6.3.1 Sample preparation                            | 104 |

| 6.3.2 Data analysis                                 | 107 |

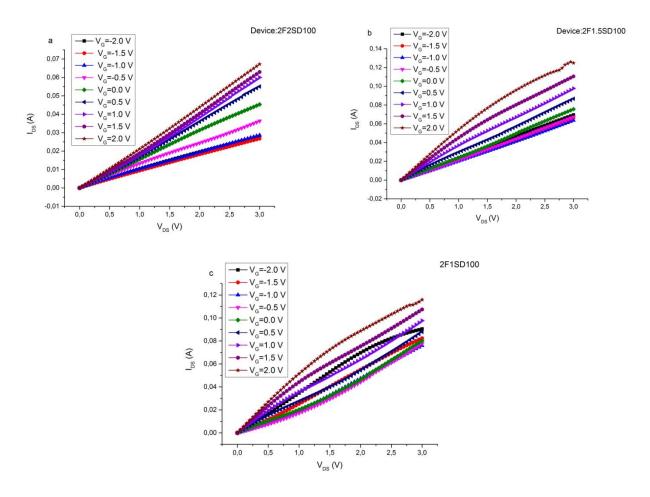

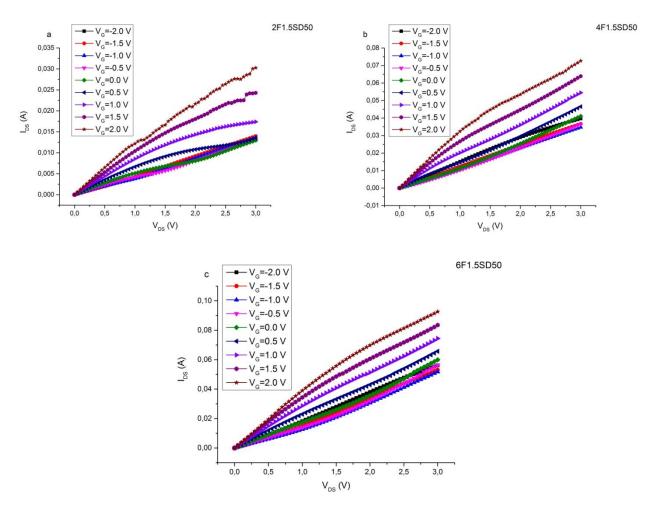

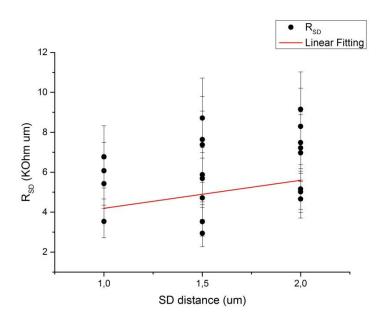

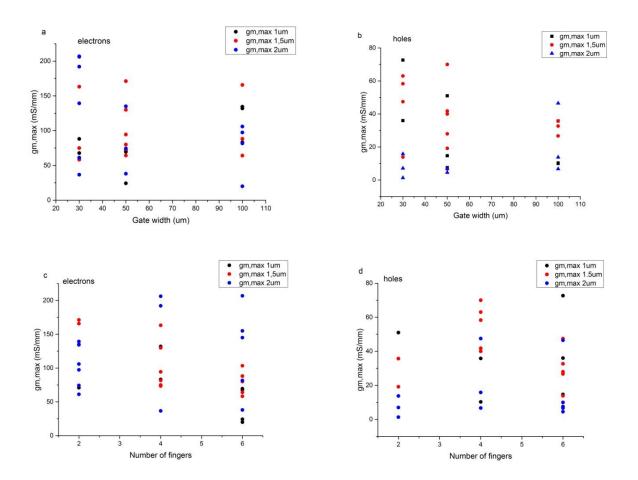

| 6.3.3 Results and discussion                        | 112 |

| 6.3.4 Conclusions                                   | 125 |

| References                                          | 127 |

# Acknowledgment

Firstly, I would like to express my gratitude to my examination committee consisting of Prof. Georgakilas Alexandros, Associate Prof. Hatzopoulos Zaharias, and Assistant Prof. Iliopoulos Eleftherios for giving me the opportunity to work in the Microelectronics Research Group facilities (Electrical Characterization Laboratory), in the Institute of Electronic Structure and Laser at FORTH.

Furthermore, I am particularly grateful for the assistance given by my thesis supervisor Dr. Deligeorgis George for his scientific and personal guidance. He was always available to discuss with me the issues of my experimental thesis providing me with precious and valuable advices to continue my study. I would like to express to him my deep appreciation because not only have I gained a great deal of knowledge but also he helped me to further develop my academic background.

Following, I wish to acknowledge the help provided by Mr. Doundoulakis George for the implementation of electrical measurements. Also, I must thank Mr. Stavrinidis George for the fabrication of the studied samples.

Finally, a special thanks to my friends and colleagues Ioanna Demeridou, Maria Patakaki, Kiki Blazaki, Andreas Lemonis, Elisa Papadopoulou, Alexandra Stavrakaki, Marina Stivaktaki, Christiana Alexandridi, Rafael Skalidis, and Myronas Sgouros for their emotional support and the enjoyable moments that we spent together.

# Περίληψη

Στην παρούσα εργασία σκοπός μας είναι η μελέτη και βελτιστοποίηση τρανζίστορ επίδρασης πεδίου από γραφένιο. Αρχικά, μελετήσαμε, επαφές παλλαδίου (Pd) σε γραφένιο και την επίδραση που είγαν στις επιδόσεις των τρανζίστορ, τον καθαρισμό της διεπιφάνειας παλλαδίου-γραφενίου με πλάσμα οξυγόνου για χρόνους έκθεσης 0, 5, 10, 15 και 20 δευτερολέπτων, πριν την εναπόθεση του μετάλλου, καθώς επίσης και την θερμική ανόπτηση υπό συνθήκες αέρα, κενού και ατμόσφαιρας υδρογόνου/αζώτου (Η2/N2) μετά την ολοκλήρωση της κατασκευής των δειγμάτων. Τα μεγέθη που εξάγαμε από τον ηλεκτρικό χαρακτηρισμό ήταν η αντίσταση επαφής και η επιφανειακή αντίσταση του γραφενίου. Ακολούθως, μέρος της εργασίας ήταν η μελέτη του οξειδίου του Αφνίου (HfO2) ως διηλεκτρικό πύλης. Ο ηλεκτρικός του χαρακτηρισμός έγινε κατασκευάζοντας δομές μετάλλου-οξειδίου-μετάλλου και εξετάστηκε η αξιοπιστία του ως προς την τάση κατάρρευσης, το ρεύμα διαρροής αλλά και της μεθόδου εναπόθεσης του διηλεκτρικού. Δύο μέθοδοι εναπόθεσης χρησιμοποιήθηκαν, η θερμική εξάχνωση με χρήση τηλεβόλου ηλεκτρονίων και η ατομική εναπόθεση στρώματος. Τέλος, η εργασίας ολοκληρώθηκε με τη μελέτη των τρανζίστορ επίδρασης πεδίου από γραφένιο ως ολοκληρωμένη πλέον ηλεκτρονική διάταξη. Διαγράμματα Dirac, χαρακτηριστικές εξόδου, ηλεκτρική αντίσταση μεταξύ πηγής-απαγωγού και η διαγωγιμότητα, όπως αυτά πρόεκυψαν από τον ηλεκτρικό χαρακτηρισμό, εξεταστήκαν με βάση το πλάτος της πύλης των τρανζίστορ, το μήκος πηγής-απαγωγού και καναλιού.

#### **Abstract**

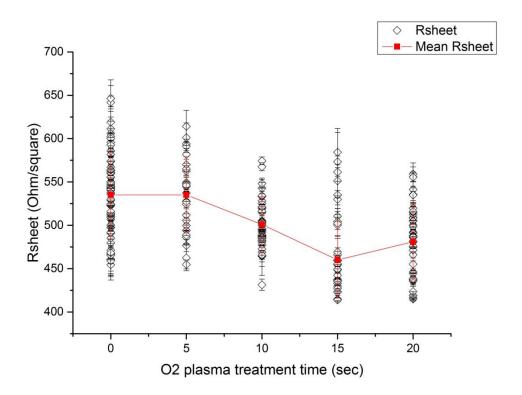

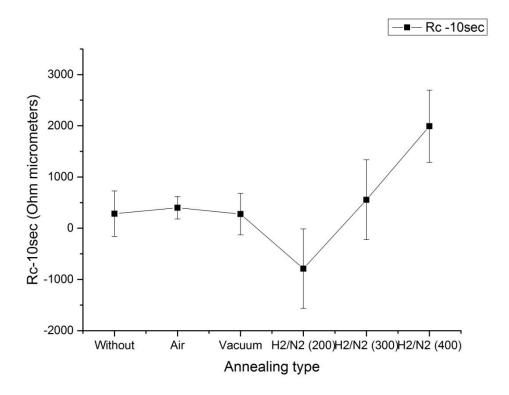

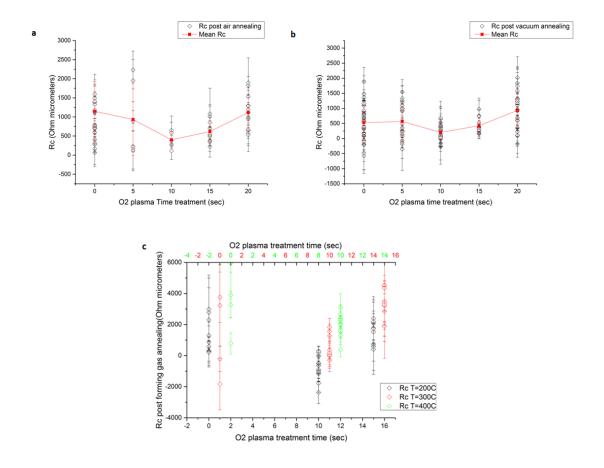

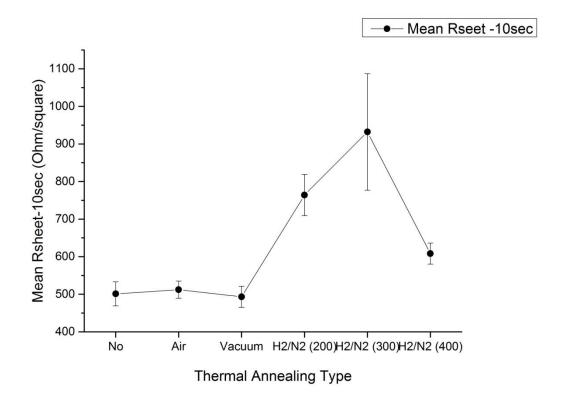

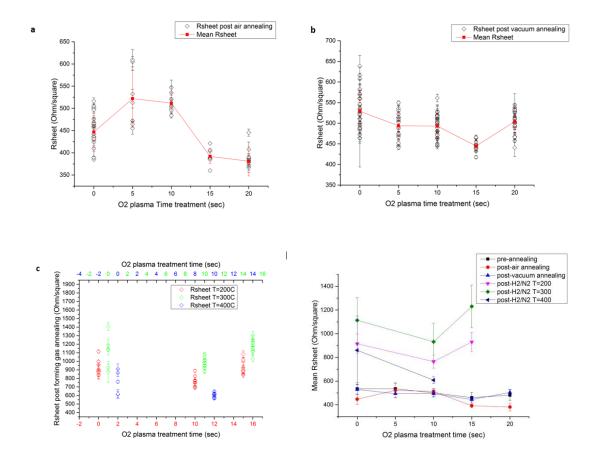

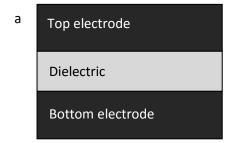

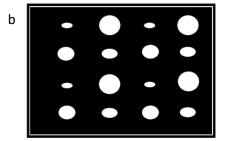

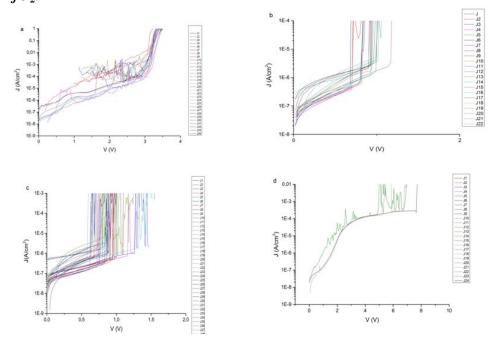

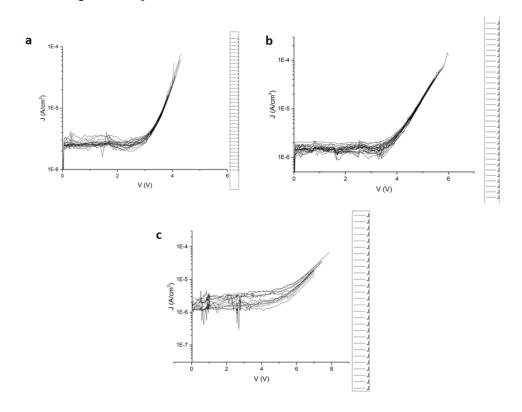

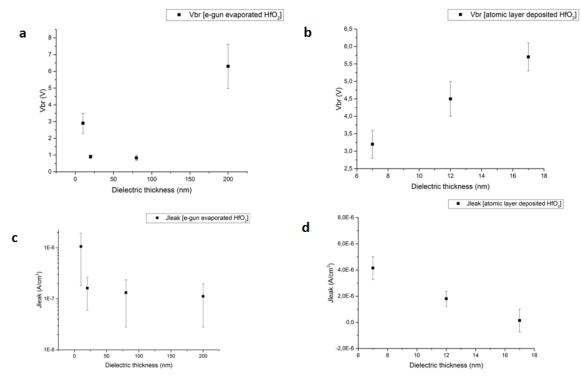

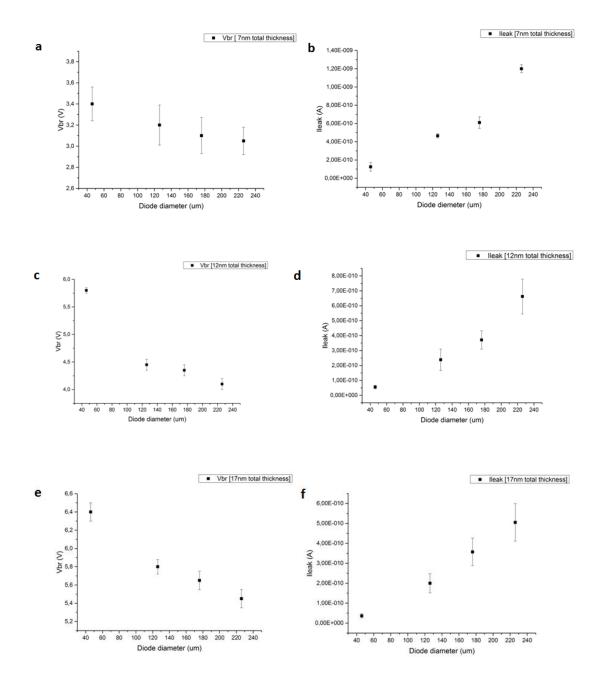

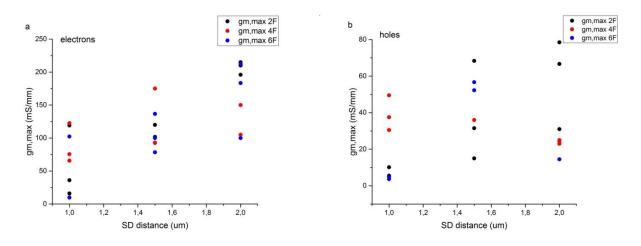

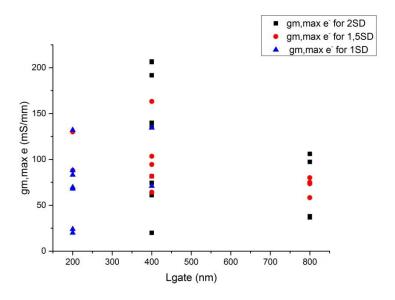

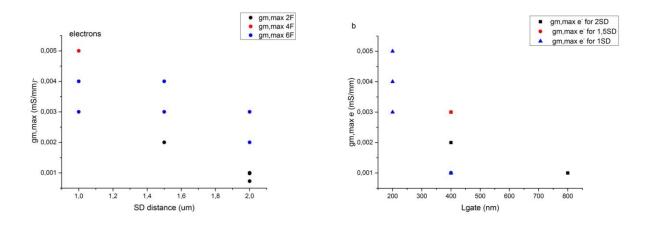

The purpose of this thesis is the study and optimization of field effect transistors based on graphene. Initially, we studied, palladium (Pd)- graphene contacts and their impact on the transistors performance, the O2 plasma cleaning of the Pdgraphene interface prior to metal deposition for exposure times of 0, 5, 10, 15, 20seconds, and the thermal annealing under air, vacuum and forming gas  $(H_2/N_2)$ conditions after the sample fabrication. The quantities that we extracted through the electrical characterization were the contact and graphene sheet resistance. Following, the second part of this thesis was the study of the hafnium oxide (HfO<sub>2</sub>) as a gate dielectric. Its characterization was accomplished by fabricating metal-oxide-metal (MOM) structures and its reliability was tested according to the breakdown voltage, leakage current, and the dielectric deposition method. The e-gun evaporation and atomic layer deposition were utilized to deposit the dielectric films. Finally, the thesis was concluded with the study of the graphene field effect transistors as completed device. Dirac diagrams, the output characteristics, the electrical source-drain resistance and transconductance, as were extracted through the electrical characterization, were studied as a function of the gate width, the source-drain distance and gate length.

#### 1. Graphene

#### 1.1 Introduction

Graphene is the name given to the arrangement of carbon atoms on hexagonal honeycomb lattice that is exactly one atom thick [1]. In 2004 Andre Geim and Konstantin Novoselov, succeeded in obtaining graphene in the form of small flakes of the order of several microns through mechanical exfoliation of graphite using a common scotch tape [2],[3]. Because of its unusual and unique physical properties such as, high intrinsic carrier mobility, high thermal conductivity, transparency, strong field effect and flexibility, graphene is considered as a promising material and a possible alternative to silicon- based semiconductor devices [2].

### **1.2** Graphene Structure

Graphene is a two dimensional sheet of carbon atoms densely packed together into a hexagonal - honeycomb crystal structure, with two atoms in each unit cell bonded together with a carbon bond. The length of this  $\sigma$ -bond is 1.42Å [4],[5]. Each atom holds to its three nearest neighbors in a triangular planar structure of graphene, through strong covalent bonds arising from a sp² hybridization of the 2s and 2p orbitals. These  $\sigma$ -bonds are responsible for the mechanical properties of graphene. The p-orbitals of adjacent carbon atoms are normal to the planar structure, and can bind to form a half-filled  $\pi$  band where the electrons can move freely. This gives rise to graphene's unique electronic properties [4],[5].

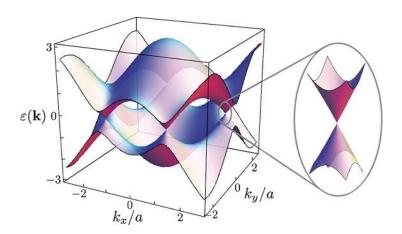

The band structure gives information about the relationship between the energy and the momentum of the charge carriers. The band structure derivation within the Tight Binding Approximation was fist done by Wallance [6]. Considering interactions only between first nearest neighbors, the eigenvalues of energy may be expressed as

$$E(k) = \pm V p p \pi \sqrt{3 + 2\cos(k \cdot a_1) + 2\cos(k \cdot a_2) + 2\cos(k(a_1 - a_2))}$$

(1.1),

where  $\alpha_1 = \left(\sqrt{\frac{3}{2}}\alpha, \frac{\alpha}{2}\right)$ ,  $\alpha_2 = \left(\sqrt{\frac{3}{2}}\alpha, \frac{\alpha}{2}\right)$  are the graphene lattice vectors and  $Vpp\pi$  is the overlapping integral between pz-orbitals. The points where the conductance and valence bands intersect are called Dirac points. Close to these points, in the range of low energies, the relation between energy and momentum becomes linear. As one can see by expanding Eq.(1.1) around k=K+q, for  $|q| \ll |K|$  obtaining [6]:

$$E(q) = \pm \hbar v_F |q|$$

(1.2),

where  $v_F = \frac{3}{2} \frac{Vpp\pi a}{\hbar} \approx 1 \times 10^8$  cm/s is the Fermi velocity at which electrons or holes move.

The linear dispersion in contrast to the conventional parabolic dispersion, means that the charge carriers are massless, often called Dirac fermions, with a velocity that is independent of the energy.

Fig.(1): Graphene electronic band-structure and linear dispersion at low energies, adapted from [4].

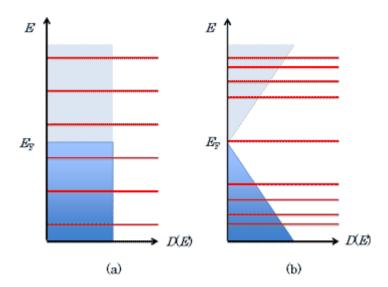

#### 1.3 Density of States

The density of states gives the number of the allowed electron or holes states per unit volume at a given energy. It can be derived from basic quantum mechanics. In the case of a conventional 2D semiconductor with parabolic bands, the density of states per unit energy and per unit volume can be easily computed as follows:

Let us consider that electrons are restricted in a two dimensional plane of L×L in the two directions x,y and in the third z-direction the plane has zero thick. The solution of Schrödinger equation for free particles is plane waves in two dimensions

$$\psi_{\overrightarrow{k|i}}(\overrightarrow{r}) = \sqrt{\frac{1}{s}} e^{i\overrightarrow{k|i}}\overrightarrow{r}$$

(1.3),

where  $|\vec{k}| = (k_x, k_y)$  and  $S = L^2$  is the area, with corresponding energy of

$$E_{\overrightarrow{k||}} = \frac{\hbar^2 k_x^2}{2m} + \frac{\hbar^2 k_y^2}{2m} = \frac{\hbar^2 k_{||}^2}{2m}$$

(1.4)

Applying the periodic conditions

$$\psi(x+L,y)=\psi(x,y)$$

and  $\psi(x,y+L)=\psi(x,y)$

the two components of  $\vec{k} = (k_x, k_y)$  get discrete values

$$k_x = \frac{n_x (2\pi)}{L}, \quad k_y = \frac{n_y (2\pi)}{L}$$

(1.5)

Thus, every state in  $\overrightarrow{k_{||}}$  - space occupies  $\overrightarrow{k_{||}}$  - area  $\delta S_k = (2\pi/L)^2$ , where  $S = L^2$  is the area of plane. As the constant energy curves in 2D space are cyclic we will consider the  $\overrightarrow{k_{||}}$  - area, which is enclosed from two cyclic constant energy curves with a separation distance between them equal to dk in 2D  $\overrightarrow{k_{||}}$  - space, with corresponding energy difference of dE.

So, one can obtain the number of states by dividing the area  $2\pi k_{||}dk_{||}$  between the two cycles with the area of one state,

$$dN = 2 \frac{2\pi k_{||} dk_{||}}{(2\pi/L)^2} = \frac{s}{\pi} k_{||} dk_{||} \quad (1.6) .$$

Finally the density of states per unit energy and per unit area can be expressed as,

$$D_{2d}(E) = \frac{dN}{S dE} = \frac{S}{\pi} k_{||} dk_{||} \frac{1}{S dE} = \frac{1}{\pi} \frac{k_{||} dk_{||}}{dE} = \frac{m}{\pi \hbar^2}$$

(1.7).

The equation (1.7) is valid for the case of parabolic bands. In order to find the right expression for the graphene density of states, we follow the above steps using

the fact of the linear relation between energy and momentum. Here the relation between energy and momentum of electron is given by equation (1.2) and the finally expression for the graphene density of states is

$$DOS_{graphene} = \frac{2E}{\pi \hbar^2 v_F^2} \quad (1.8)$$

**Fig.(2):** (a) the density of states in a conventional 2DEG with parabolic bands, (b) the density of states in graphene with linear dispersion. As we can see in the second case there is a linear relation between density of states and energy that goes all the way to zero, whereas in conventional 2Degs with parabolic bands the density of states is independent and constant over energy. Image adapted from [7].

## 1.4 Graphene Synthesis Methods

Today there are several methods for the preparation of graphene. In the following sections, some of these methods will be briefly presented and discussed. They will be compared according to the quality of graphene and the purpose of its use.

#### 1.4.1 Mechanical exfoliation

Since graphite consists of sheets of graphene kept together by weak Van Der Waals energy of the order of 2eV/nm<sup>2</sup> and the force of about 300nN/µm<sup>2</sup>[8], graphene can be detached from a graphite crystal using adhesive tape. Continuation of the peeling process can lead to multilayer and even single-layer graphene as it was done for its discovery. Afterwards, graphene from adhesive tape can be transferred to

$SiO_2/Si$  substrate. The oxide thickness plays an essential role in order to distinguish the graphene flakes. An appropriate oxide thickness is 90nm or 300nm as in that range of thicknesses the optical contrast in visible light increases [9],[10]. Graphene obtained by this method has shown properties very close to theoretical predictions e.g. mobility of the order of  $10^6$  cm<sup>2</sup>/Vs. The drawbacks of this method are that the adhesive tape leaves residues on graphene that can result in degradation of mobility, and also this method cannot provide large scale graphene [11].

#### 1.4.2 Graphitization of silicon carbide SiC

In this method graphene can be synthesized by sublimation of silicon at the temperature of about 1300 °C in an ultrahigh vacuum environment [12]. The advantages of this method are that the silicon carbide provides an insulating substrate and no further transfer of graphene layer is needed and we can obtain graphene flakes in larger scale than that of mechanical exfoliation method. But, high temperature and high cost of production are considered as obstacles to applying this method.

#### 1.4.3 Chemical vapor deposition

Chemical vapor deposition (CVD) is a well known process in which a substrate is exposed to gaseous compounds. Also, it is compatible with existing semiconductor industry processes [13]. In this technique graphene can be grown by exposing a transition metal film such as Ni, Cu, Co, Pt, Ir or Ru to a gas mixture of H<sub>2</sub>, CH<sub>4</sub> (or any other hydrocarbon) and Ar at various temperatures and pressures depending on the type of metal film and gas type. In the case of a Ni film, the metal substrate is exposed at 1000°C, in which the methane decomposes on the surface, so that the hydrogen evaporates. The carbon diffuses into the nickel, and after cooling down in Ar atmosphere, a graphene layer grows on the surface. One of the benefits of CVD method, is that the number of the graphene layers depends on the substrate thickness, that is why CVD method is considered as a controllable synthesis method of graphene. Although, CVD provides graphene in large scale, graphene layers need to be transferred to a substrate, which results in degradation of its carrier mobility due to the polymeric residues [14].

#### 2. Metal-Graphene junction

#### 2.1 Introduction

Since all semiconductor devices have contacts and all contacts have contact resistance, it is important to characterize such contacts. Contacts are generally formed when a metal and a semiconductor are joined together, but they may be formed by semiconductor-semiconductor junction, where both semiconductors can be single crystal; polycrystalline, or amorphous. Two possible types of contacts can result depending on the combination of materials used. The contacts may be ohmic or Schottky barrier contacts. In the case of ohmic contacts, the most common contacts are these of metal-semiconductor contacts [15].

Ohmic contacts have linear or quasi-linear current-voltage characteristics. It is not necessary, however, that ohmic contacts have linear I-V characteristics. The contacts must be able to supply the necessary device current, and the voltage drop across the contact should be small compared to the voltage drop across the active device regions. An ohmic contact should not degrade the device to any significant extent, and it should not inject minority carriers. On the other hand, Schottky barrier contacts have no linear I-V characteristics. Devices based on Schottky barrier contacts are usually referred to as Schottky barrier devices. This name denotes the use of these devices as rectifiers [15].

#### 2.2 Metal-Semiconductor Contacts

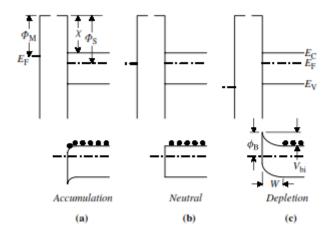

Since ohmic contact is generally modeled as a heavily doped Schottky contact, it is useful to begin the theoretical background with the Schottky model of the metal-semiconductor barrier as it is shown in Fig.(3).

**Fig.(3):** Metal-semiconductor contacts according to the simple Schottky model. The upper and lower parts of the figure show the metal-semiconductor system before and after the contact, respectively. The image is adapted from [15].

We assume intimate contact between the metal and the semiconductor with no interfacial layer. The upper part of the figure represents the energy bands before the contact while the lower part represents the energy bands after the contact. The ideal barrier height after contact for this model is given by

$$\Phi_R = \Phi_M - \chi \ (2.1)$$

where  $\Phi_M$  is the work function of the metal,( $\Phi_S$  is the work function of the semiconductor respectively, and  $\chi$  is the electron affinity. The work function of a solid is defined as the energy difference between the vacuum level and the Fermi level while the electron affinity is defined as the potential difference between the bottom of conductance band and the vacuum level at the semiconductor surface. According to the Schottky theory, the barrier height depends only on the metal work function and on the semiconductor electron affinity and is independent of the semiconductor doping density. After contact three types of barrier are possible. We have named them accumulation, neutral, and depletion contacts according to the behavior of the majority carriers [15].

As is evident from Fig.(3) an accumulation – type contact is the preferred ohmic contact because electrons in the metal encounter the least barrier to their flow into or out of the semiconductor. In practice it is difficult to alter the barrier height by using metals of varying work functions. The barrier height with various work

functions metals is many times relatively unaffected due to surface Fermi level pinning, where the Fermi level in the semiconductor surface is pinned at some energy in the band gap to create a depletion type contact [15].

Even though barrier height is independent of the doping density, the barrier width depends on the doping density. Heavily doped semiconductors have narrow space-charge region width W ( $W \sim N_D^{-1/2}$ ). In this case, electrons can tunnel from the metal to the semiconductor and vice versa. Holes tunnel for p-type semiconductor [15].

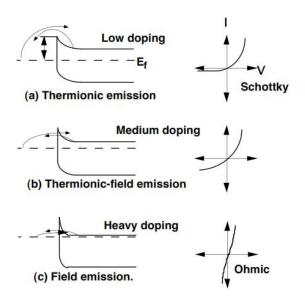

#### 2.3 Conduction Mechanisms for Metal/Semiconductor Contacts

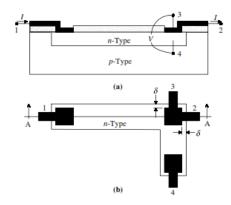

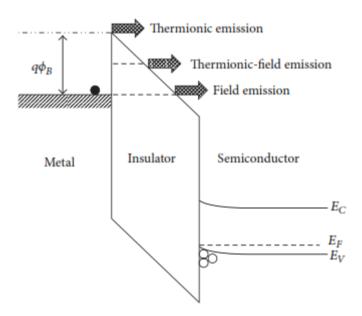

The conduction mechanisms for a metal n-type semiconductor are illustrated in Fig.(4)

**Fig.(4):** Conduction mechanisms for metal/n-semiconductor contacts as a function of the barrier height and width. (a) Thermionic emission; (b) thermionic field-emission; (c) field emission [16].

For lightly-doped semiconductors the currents flows as a result of thermionic emission (TE) with electrons thermally excited over the barrier. In the intermediate doping range thermionic-field emission (TFE) dominates with carriers thermally excited to an energy where the barrier is sufficiently narrow for tunneling to take place. Finally, for high doping densities the barrier is sufficiently narrow at or near the bottom of the conduction band for the electrons to tunnel directly, known as field

emission (FE). The last mechanism is the preferred transport mode in ohmic contacts [16].

Considering the characteristic energy  $E_{00}$  and comparing it to the thermal energy kT, where  $E_{00}$  is define by

$$E_{00} = \frac{qh}{4\pi} \sqrt{\frac{N}{K_s \varepsilon_o m_{tun}^*}} = 1.86 \times 10^{-11} \sqrt{\frac{N(cm^{-3})}{K_s(m_{tun}^*/m)}} [eV] \quad (2.2)$$

where N is the doping density,  $m_{tun}^*$  is the tunneling effective mass, and m the free electron mass we can find which of the above conduction mechanisms dominate. Thermionic emission (TE) dominates for kT>>E<sub>00</sub>, thermionic-field emission dominates for kT $\approx$ E<sub>00</sub>, and field emission occurs for kT<<E<sub>00</sub> [16].

#### 2.4 Contact resistance

The quantity that evaluates the quality of the metal-semiconductor interface in ohmic contacts is the contact resistance and gives a measure of the ease with which current can flow across this interface. Metal-semiconductor contacts fall into two basic categories. Vertical and horizontal or lateral contacts can behave quite differently, because the effective contact area may differ from the true contact area [15].

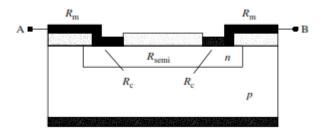

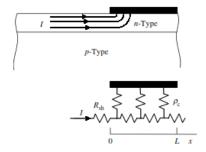

Let us consider the resistance between points A and B of the sample having metallic conductors lying on an insulator and making ohmic contacts to an n-type layer in a p-type substrate in Fig.(5)

**Fig.(5):** A schematic diagram showing two contacts to a diffused semiconductor layer, with the metal resistance, the contact resistances and the semiconductor resistance indicated. The image is adapted from [15].

The total resistance  $R_T$  is defined by the following equation

$$R_T = 2R_c + 2R_m + R_{semi} \qquad (2.3)$$

where  $R_c$  represents the contact resistance,  $R_m$  represents the metallic conductor resistance and  $R_{semi}$  represents the resistance of the semiconductor which is defined by the sheet resistance. Even though the resistance of the semiconductor is well defined we cannot say the same for the contact resistance. Contact resistance certainly includes the resistance of the metal-semiconductor contact, a portion of the metal immediately above the metal-semiconductor interface, a part of the semiconductor below the interface, current crowding effects, and any interfacial oxide or other layer that may be present between the metal and semiconductor [15].

#### 2.5 Definition of contact resistance

The current density J of a metal-semiconductor contact depends on the applied voltage V, the barrier height  $\phi_B$  and the doping density N in manner that varies for each of the three conduction mechanisms. The contact resistance is characterized by two quantities: the contact resistance  $R_c$  (ohms) and the specific contact resistivity  $\rho_c$  (ohm cm<sup>2</sup>). The specific contact resistivity includes not only the actual interface but the regions above and below the interface [15].

The specific interfacial resistivity  $\rho_i$  (includes the resistance of the metal-semiconductor interface) is defined by

$$\rho_i = \frac{\partial V}{\partial I} | V = 0 \quad (2.4)$$

Since the contact area also plays a role in the behavior of the contact, it must be noted that specific interfacial resistivity is also defined by

$$\rho_i = \frac{\partial V}{\partial J} | A \to 0 \quad (2.5)$$

where A is the contact area. This specific interfacial resistivity is a theoretical quantity referring to the metal-semiconductor interface only. It is not actually measurable because of the effects referred above. The parameter that is determined from the

measured contact resistance is the specific contact resistivity  $\rho_c$  (ohm cm<sup>2</sup>). It is a very useful term for ohmic contacts because it is independent of contact area [15].

The current density J of a metal-semiconductor contact, dominated by thermionic emission, is given by

$$J = A^* T^2 e^{-q\varphi B/kT} (e^{qV/kT} - 1) \quad (2.6)$$

where  $A^* = \frac{4\pi q k^2 m^*}{h^3} = 120 (m^*/m) A/cm^2 K^2$  is Richardson's constant, m is the free electron mass, m\* the effective mass, and T the absolute temperature. With equations (4),(6) we find the specific interfacial resistivity for

Thermionic emission

$$\rho_i(TE) = \frac{k}{qA^*T} e^{q\varphi B/kT}$$

(2.7)

Thermionic-field emission  $\rho_i(TFE) = C_1 \frac{k}{qA^*T} e^{q\varphi B/E_0}$  (2.8)

Field emission

$$\rho_i(FE) = C_2 \frac{k}{qA^*T} e^{q\varphi B/E_{00}}$$

(2.9)

where  $C_1, C_2$  are functions of N,T and  $\varphi_B$ .  $E_0$  in Eq.(2.8) is related to  $E_{00}$  by

$$E_0 = E_{00} \coth(E_{00}/kT)$$

(2.10)

Substituting for  $E_{00}$  in Eq.(9) leads to

$$\rho_i(FE) \sim \exp\left(\frac{C_3}{\sqrt{N}}\right) (2.11)$$

where  $C_3$  is a constant and N the doping density under the contact. Finally, we have to say that specific interface resistivity, primarily depends upon the potential barrier height  $\phi_B$ , as Eq.(2.11) indicates it is dependent on doping density N [15].

#### 2.6 Measurement Techniques

Contact resistance measurement techniques fall into four main categories: two-contact two-terminal, multiple-contact two-terminal, four-terminal, and six terminal methods. All these methods are capable of determining the specific contact resistivity  $\rho_c$ , which is a practical quantity describing the real contact and not only the metal-semiconductor interface [15].

#### 2.6.1 Two-contact Two-terminal Method

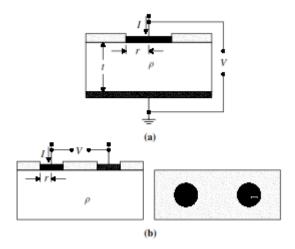

The two-contact two-terminal method is the earliest method. For an homogeneous semiconductor of resistivity  $\rho$  and thickness t with two contacts as shown in Fig.(6a) , the total resistance  $R_T$ =V/I, measured by passing a current I through the sample and measuring the voltage V across the two contacts, is

$$R_T = R_c + R_{sp} + R_{cb} + R_p$$

(2.12. a)

For Fig.(6b) with both contacts on the top surface

$$R_T = 2R_c + 2R_{sp} + 2R_p$$

(2.12.b)

**Fig.(6):** (a) A vertical two-terminal contact resistance structure, (b) a lateral two-terminal contact resistance structure. The image is adapted from [15].

where  $R_c$  is the contact resistance of the top contact,  $R_{sp}$  the spreading resistance in the semiconductor directly under the contact,  $R_{cb}$  the contact resistance of the bottom contact, and  $R_p$  the probe or wire resistance.  $R_{cb}$  is often neglected because the bottom contact has a large contact area. Similarly, the probe or wire resistance is usually negligible [15].

The spreading resistance of a flat, non indenting circular top contact or radius r on the surface of a semiconductor of resistivity  $\rho$ , thickness t, and a large bottom contact can be approximated by

$$R_{sp} = \frac{\rho}{2\pi r} \arctan(2t/r) \quad (2.13)$$

For 2t>>r Eq.(2) can be expressed by

$$R_{sp} = C \frac{\rho}{4r} \quad (2.14)$$

where C is a correction factor that depends on  $\rho$ ,r and on the current distribution. For widely separated contacts for the structure in Fig.6b, on an uniformly-doped, semi-infinite substrate the correction factor C=1. With the current flowing vertically into the top contact as in Fig.6a , the contact resistance is [15]

$$R_c = \frac{\rho_c}{A} = \frac{\rho_c}{\pi r^2}$$

(2.15)

For small  $R_{cb}$ , Eq.(2.12) shows the contact resistance to be the difference between the total resistance and the spreading resistance. The spreading resistance cannot be measured independently and small errors in  $R_{sp}$  can lead to large errors in  $R_c$ . The two-terminal method, therefore works better when  $R_{sp} << R_c$ , approximated by using small radius contacts [15].

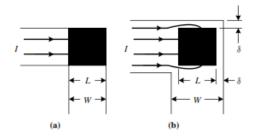

The two-terminal method is more commonly implemented with the lateral structure of Fig.7. This test structure differs from Fig.6b by confining the current to the n-island [15].

**Fig.(7):** A lateral two-terminal contact resistance structure in cross section and top view. The image is adapted from [15].

The test structure consists of two contacts separated by spacing d. To confine the current flow, the region on which the contact is located must be isolated from the remainder of the substrate, by either confining the implanted or diffused region (n-type on p-type or p-on-n). by planar techniques or by etching the region surrounding the island, leaving it as a mesa. The n-type island in this example has width W and

ideally the contacts should also be W wide. That is difficult to implement and the contact width Z generally differs slightly from W. The analysis becomes more complex due to lateral current flow, current crowding at the contacts, and sample geometry. For the geometry of Fig.7, the total resistance is [15]

$$R_T = R_{sh} \frac{d}{W} + R_d + R_w + 2R_c \quad (2.16)$$

where  $R_{sh}$  is the sheet resistance of the semiconductor layer,  $R_d$  the resistance due to current crowding under the contacts,  $R_w$  a contact width correction if Z<<W, and  $R_c$  the contact resistance assuming it is identical for the two contacts. Finally, for a contact string consisting of N islands and 2N contacts, with contacts separated from each other by spacing d and width W and neglecting the metal resistance, the total resistance is given by [15]

$$R_T = N \frac{R_{sh}}{W} d + 2NR_c \quad (2.17)$$

#### 2.6.2 Multiple - Contact Two-Terminal Methods

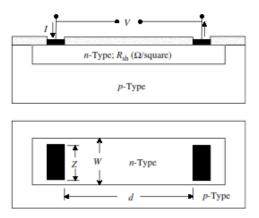

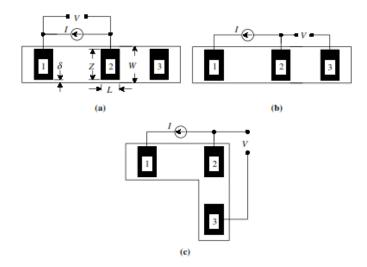

The multiple-contact, two-terminal contact resistance measurement technique, shown in Fig.8, was developed to overcome the deficiencies of the previous measurement technique [15].

**Fig.(8):** Multiple-contact, two-terminal contact resistance test structure. The contact width and length are Z and L and the diffusion width is W. The image is adapted from [16].

Three identical contacts are made to the semiconductor with contacts spacing d<sub>1</sub> and d<sub>2</sub>. Assuming identical contact resistances for each of three contacts allows the total resistance to be written as

$$R_{Ti} = \frac{R_{sh}d_i}{W} + 2R_c \ (2.18)$$

where i=1 or 2. Solving for Rc gives

$$R_c = \frac{(R_{T2}d_1 - R_{T1}d_2)}{2(d_1 - d_2)} \quad (2.19)$$

The test structure shown in the above figure, Fig.8, seems to overcome the ambiguities of the simpler two-terminal structure, due to the fact that neither the bulk resistance nor the layer sheet resistance need be known, but only the contact resistance and not the specific contact resistivity can be determined. Possible sources of inaccuracy in the determination of contact resistance should be the assumption that all the contacts have identical contact resistances, the fact that the contact resistance is obtained by taking the difference of two large numbers and finally the way that the lengths  $d_1$ ,  $d_2$  are determined. The last issue occasionally leads to negative contact resistances [15].

#### 2.6.3 Transfer length Method

Since with the above method the specific contact resistivity cannot be determined, this method (TLM) by taking the current crowding into account allows us to extract the specific contact resistivity, considering both the contact and sheet resistance [15].

As the current flowing from the semiconductor to the metal and vice versa, it chooses the path of least resistance, but always encounters the contact and sheet resistance. The potential distribution under the contact is described by the following mathematical formula

$$V(x) = \frac{I\sqrt{R_{sh}\rho_c}}{Z} \frac{\cosh\left[\frac{L-x}{L_T}\right]}{\sinh\left(\frac{L}{L_T}\right)} \quad (2.20)$$

where L is the contact length, Z the contact width,  $L_T$  the transfer length, and I the current flowing into the contact [15].

**Fig.(9):** Current transfer from semiconductor to metal represented by the arrows. The semiconductor/metal contact is represented by the  $\rho_c$ - $R_{sh}$  equivalent circuit with the current choosing the path of least resistance. The image is adapted from [15].

For x=0, near the contact edge, the voltage has its highest value and diminishes nearly exponentially with the distance x, as the current transfers far from the contact edge. The distance over which most of the current transfers from the semiconductor

$$L_T = \sqrt{\rho_c/R_{sh}} \quad (2.21)$$

to the metal and vice versa, it is called transfer length  $(L_T)$ . At this distance the voltage drops to the 1/e of its highest value [15].

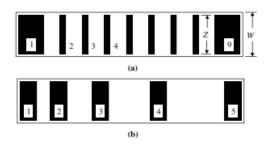

Let us consider the three contact configurations in Fig.10, with the current flowing from contact 1 to 2. In Fig.10a we have the contact front resistance ( $\equiv$ TLM structure) where both the voltage and current are measured between the same contacts. In fig.10b the contact end resistance test structure is illustrated, where the voltage is measured across the contacts 1 and 2. Finally, in Fig.10c we have the cross bridge Kelvin resistance test structure, in which the voltage is measured at right angles to the current [15].

When V measured between contacts 1 and 2 at x=0, Eq.(2.20) gives the contact front resistance as

$$R_{cf} = \frac{V}{I} = \frac{\rho_c}{L_T Z} \coth\left(\frac{L}{L_T}\right) \quad (2.22)$$

Provided Z=W. Eq.(2.22) is only an approximation when the sample is wider than Z, because this equation does not consider the current flow around the contacts [15].

**Fig.(10):** (a) Conventional contact resistance test structure, (b) contact end resistance test structure and (c) cross bridge Kelvin resistance test structure. The image is adapted from [15].

The expression  $R_{cf} \equiv R_c$  given by Eq.(2.22), could be simplified according to the following conditions:

For L $\leq$ 0.5 L<sub>T</sub>, coth(L/L<sub>T</sub>) $\sim$ L<sub>T</sub>/L

$$R_c \sim \frac{\rho_c}{LZ}$$

(2.23a)

For L $\geq$ 1.5 L<sub>T</sub>, coth(L/L<sub>T</sub>) $\sim$ 1

$$R_c \sim \frac{\rho_c}{L_T Z}$$

(2.23b)

The effective contact area is the actual contact area  $A_c$ =LZ for the first case. But in the second case the effective contact area is  $A_{c,eff}$ =L<sub>T</sub>Z. In other words, the effective contact area can be smaller than the actual contact area [15].

In the case of Fig.10b, where the voltage is measured across the contact 2 and 3, at x=L the equation 2.20 leads to the contact end resistance

$$R_{ce} = \frac{V}{I} = \frac{\rho_c}{L_T Z} \frac{1}{\sinh\left(\frac{L}{L_T}\right)} \quad (2.24)$$

The accuracy of the method is limited for short contacts where variations of contact length strongly affect the determination of the  $R_{ce}$ . For long contacts,  $R_{ce}$  becomes very small and the accuracy is limited by instrumentation, seen by looking at the ratio

$$\frac{R_{ce}}{R_{cf}} = \frac{1}{\cosh(L/L_T)}$$

(2.25)

which obviously becomes very small for L>>L<sub>T</sub> [15].

For the cross-bridge Kelvin resistance test structure in Fig.10c, the voltage contact 3 is located at the side of contact 2. The measured voltage is thus the linear average of the potential over the contact length L. Integrating Eq.(2.20)

$$V = \frac{1}{L} \int_{0}^{L} V(x) dx \quad (2.26)$$

gives the contact resistance as

$$R_c = \frac{V}{I} = \frac{\rho_c}{LZ} \quad (2.27)$$

In equation 2.24 the measured resistance obtained by assuming that the contact width Z to be identical to the sheet width W. in practice this assumption is not valid and Z<W. Under the last condition the measured contact end resistance leads to erroneously high  $\rho_c$ . The error is attributed to the potential difference between the front and the near edge of the contact allowing the current to flow around the contact edges. For large  $\delta$ , the measured resistance is proportional to the sheet resistance but independent on the contact resistance. The one-dimensional analysis is valid only if the following condition: L<<L<sub>T</sub>, Z>>L and  $\delta$ <<Z are met. However, accurate extraction of  $\rho_c$ , is possible by fitting numerical simulations to measured data [15].

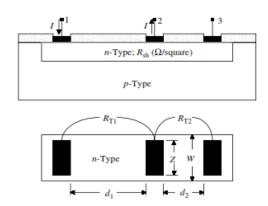

The difficulty of deciding where to measure the voltage in the configuration of Fig.10a.10b.10c has led to a test structure shown in Fig.11a and a measured technique known as the transfer length method originally proposed by Shockley. The TLM test structure consists of more than three contacts. The first and last contacts in the test structure served as entry and exit point for the current in the original ladder structure and the voltage was measured between one of the large contacts and each of the successive narrow contacts in Fig.11a. Later the test structure had unequal spacing between contacts as in Fig.11b, with the voltage measured between adjacent contacts [15].

Fig.(11): Transfer length method test structures. The image is adapted from [15].

The test structure illustrated in Fig.11b is more advantageous than that of illustrated in Fig.11a., because the effects of the contacts 2 and 3 may be eliminated, when the voltage is measured across the contacts 1 and 4. Concerning the contact length, L, and the transfer length,  $L_T$ , we can say that for L<<L $_T$ , the current does not penetrate essentially into the contact metal and thus the contact 2 and 3 have no effects on the measurement. But, in the opposite case where L>>L $_T$  the current flows into the contact metal and the contact can be thought of as two contacts, each of length  $L_T$  joined by the contact metal itself. It is for this reason that the structure in Fig.11b is preferred, because there is only bare semiconductor between any two contacts [15].

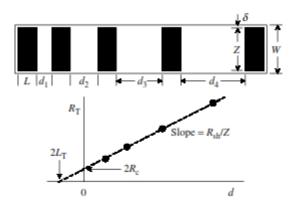

For contacts L $\geq$ 1.5 L<sub>T</sub> and for a front contact resistance measurement of the structure in Fig.11b, the total resistance between any two contacts is

$$R_T = \frac{R_{sh}d}{Z} + 2R_c \sim \frac{R_{sh}}{Z} (d + 2L_T)$$

(2.28)

The total resistance is measured for various contact spacings and plotted versus d as illustrated in Fig12. Three parameters can be extracted from such a plot. The slope  $\Delta(R_T)/\Delta(d)=R_{sh}/Z$  leads to the sheet resistance with the contact width Z independently measured. The intercept at d=0 is  $R_T=2R_c$  giving the contact resistance. The intercept at  $R_T=0$  gives  $-d=2L_T$ , which leads to the specific contact resistivity with  $R_{sh}$  known from the slope of the plot. The transfer length method gives a complete characterization of the contact by providing the sheet resistance, the contact resistance, and the specific contact resistivity [15].

Even though the transfer length method is commonly used to characterize the quality of contacts, it has its own problems. These problems arise from the assumptions we have made. First, the transfer length obtained from the intercept at  $R_T$ =0 is sometimes not very distinct, leading to incorrect  $\rho_c$  values. Second, equation 2.28 presupposes that the sheet resistance under the contact and between the metal contacts to be identical. But, in practice the latter is not valid, due to the effects of the contact formation between the contact metal and the semiconductor sheet. In this case we have a modification in the expression for front contact and total resistance [15].

$$R_{cf} = \frac{\rho_c}{L_{Tk}Z} \coth\left(\frac{L}{L_{Tk}}\right) \quad (2.29)$$

and

$$R_T = \frac{R_{sh}d}{Z} + 2R_c = \frac{R_{sh}}{Z} \left[d + 2\left(\frac{R_{sk}}{R_{sh}}\right) L_{Tk} \right]$$

(2.30)

where Rsk is the sheet resistance under the contact and  $L_{Tk}$ = $(\rho_c/R_{sk})^{1/2}$ . The slope of the  $R_T$  versus d plot still gives  $R_{sh}/Z$  and the intercept at d=0 gives  $2R_c$ . However, the intercept at  $R_T$ =0 now yields  $2L_{Tk}(R_{sk}/R_{sh})$  and it is no longer possible to determine  $\rho_C$  since  $R_{sk}$  is unknown. Nevertheless, by determining  $R_{cf}$  from the transfer length method and  $R_{ce}$  from the end resistance method, where

$$\frac{R_{ce}}{R_{cf}} = \frac{1}{\cosh(L/L_{Tk})}$$

(2.31)

one can determine  $L_{Tk}$  and  $\rho_c$ . In this way it is possible to find the contact resistance and the specific contact resistivity in addition to the sheet resistance between and under the contacts. Third, the TLM gives reliable results for samples that the electrical and geometrical characteristics are homogeneous and the specific contact resistivity does not scatter across the sample wafer. Fourth, another parameter that it has been reasonably ignored is the resistance of the contact metal itself, but in the case of metal aging the metal resistance increases and can no longer be neglected. Finally, the gap  $\delta$  is assumed to be zero, otherwise for non uniformed samples these factor must be taken into account and a modification of the contact resistance equation is necessary [15].

**Fig.(12):** A transfer length method test structure and a plot of total resistance as a function of contact spacing d. The image is adapted from [15].

## 2.6.4 Four-Terminal Contact Resistance Method

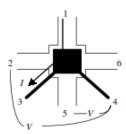

The four-terminal Kelvin test structure also known as the cross-bridge Kelvin resistance is the method that allows the extraction of the contact resistance or the specific contact resistivity without any requirement for the semiconductor bulk resistivity or the semiconductor sheet resistance to be known [15].

**Fig.(13):** A four-terminal or Kelvin contact resistance test structure. (a) Cross section through section A-A, (b) top view of the structure. This image is adapted from [15].

In the above figure, Fig.13, the principle of this method is illustrated. Contact pads 1 and 2 served as the entry and exit points where the current is forced, while the voltage is measured between the pads 3 and 4. Across the entry and exit points there are three voltage drops. The first occurs between pad 1 and the semiconductor layer, the second along the semiconductor sheet, and the third between the n-layer and the pad 2/3. The measured voltage  $V_{34}$ = $V_3$ - $V_4$  is ascribed to the voltage drop across the

contact metal-semiconductor interface. The existence of a high input resistance voltometer ensures a very low current flow between the pads 3 and 4 and hence the potential at the pad 4 is the same as the potential under the 2/3 pad [15].

The contact resistance is given by

$$R_c = \frac{V_{34}}{I}$$

(2.32)

And specific contact resistivity is defined as

$$\rho_c = R_c A_c \ (2.33)$$

where  $A_c$  is the contact area [15].

The specific contact resistivity calculated with equation (2.33) is an apparent specific contact resistivity differing from the true specific contact resistivity by lateral current crowding for contact windows smaller than the diffusion tap, shown as  $\delta>0$  in Fig.14. Contact window to diffused layer misalignment and lateral dopant diffusion account for  $\delta>0$ . In the ideal case,  $\delta=0$  as illustrated in Fig.14a. In an actual contact, some of the current, indicated by the arrows in Fig.14b, flows around the metal contact. In the ideal case with  $\delta=0$ , the voltage drop is  $V_{34}=IR_c$ . For  $\delta>0$ , the lateral current flow gives an additional voltage drop that is included in  $V_{34}$ , leading to a higher voltage. According to equation (2.33)  $\rho_c$  is higher if the actual contact area  $A_c$  is used. In any case, for larger  $\delta$  the obtained resistance is in error. The true resistance is obtained by extrapolating to  $\delta=0$  but it is difficult to fabricate test structures with  $\delta=0$  [15].

**Fig.(14):** Four-terminal contact resistance test structures. (a) Ideal with only lateral current flow, (b) showing current flowing into and around the contact. The black area is the contact area. The image is adapted from [15].

#### 2.6.5 Six-Terminal Contact Resistance Method

The six-terminal contact resistance structure is very similar to the four-terminal Kelvin structure with two more contacts. By implementing this test structure the contact resistance, the specific contact resistivity, the contact end resistance, the contact front resistance and the sheet resistance under the contact can be determined. The structure of this technique is illustrated in Fig.(15) [15].

**Fig.(15):** Six-terminal Kelvin structure for the determination of  $R_c R_{cf} R_{ef}$  and  $R_{sk}$ . The image is adapted from [15].

By using the conventional Kelvin test structure as illustrated in the Fig.(15) the contact resistance is given by

$$R_c = \frac{V_{24}}{I} \quad (2.34)$$

and the specific contact resistivity is

$$\rho_c = R_c A_c \ (2.35)$$

Where the voltage is measured across the contacts 2 and 4 and the current is forced between the contacts 1 and 3. All the two-dimensional complications, not reflected in Eq.(2.34) and Eq.(2.35), manifest themselves in the six-terminal structure also [15].

To measure the contact end resistance  $R_{ce}=V_{54}/I$ , current is forced between contacts 1 and 3 and the voltage is sensed across contacts 5 and 4. The contact resistance and the specific contact resistivity can be determined from the Kelvin part of this structure while the sheet resistance under the contact can be determined from the end resistance using Eq.(2.31) and the contact front resistance [15].

#### 2.7 Comparison of measurement techniques

Two-terminal methods:

The two-contact two-terminal method is the least detailed technique. Contact resistance is corrupted by either the semiconductor bulk or sheet resistance [15].

Two-terminal contact string is a technique which does not give detailed R<sub>c</sub> information nor can the specific contact resistivity be reliably extracted [15].

Multiple-contact, two-terminal is usually employed in its transfer length method implementation, where the effect of the semiconductor sheet resistance is separated from the contact resistance and both contact resistance and specific contact resistivity can be determined. Problems appear when the sheet resistance under the contacts differs from the sheet resistance in the channel region and when current flows laterally around the contacts [15].

#### Four-terminal:

The four-terminal or Kelvin structure is preferred over the two- and three-terminal because contact resistance is measured directly, without metal or semiconductor sheet resistance entering into the  $R_c$  determination. Nevertheless, lateral current flow obscures the interpretation [15].

#### Six terminal method:

The six-terminal method is very similar to the four-terminal technique. It incorporates the Kelvin structure, but additionally allows measurements of the front and end contact resistance as well as the contact sheet resistance [15].

#### 2.8 Carrier transport from metal into graphene

A high quality junction between metal and graphene is crucial in the creation of high performance graphene transistors. In the case of metal-graphene junctions, in contrast to conventional metal-semiconductor junctions, carriers transfer from a three dimensional metal to a two dimensional graphene sheet, which have very different density of states [17]. So it is obvious, in order to achieve the highest device performance an appropriate metal for contact electrodes must be chosen. The injection of charge carriers into graphene from the contact electrodes is necessary to establish a current in the device.

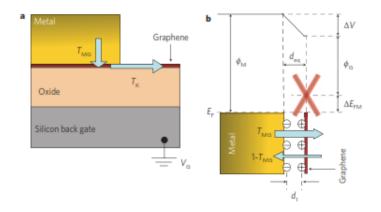

As the charge carriers transfer from the metal contact into graphene, they confront two types of barriers. The first type is referred to the electrostatic barrier that is formed as a dipole layer at the metal-graphene interface. The second type is referred to the electrostatic barrier that is formed at the region between the graphene under the electrode and the graphene in the channel region, due to charge transfer doping inhomogeneity and an effective p-n junction that may be formed there [17]. In the first case the transmission is related with a transmission coefficient  $T_{MG}$  and in the second with  $T_k$  respectively Fig.(16).

**Fig.(16):** Carrier transport processes at the palladium-graphene junction. (a) Schematic view of two cascaded carrier transport processes at the metal-graphene junction, with transmission efficiencies  $T_{MG}$  and  $T_K$ , respectively. (b) Schematic view of the band profile and dipole formation at the metal-graphene interface,  $\varphi_M$  is the palladium work function,  $\varphi_G$  is the work function of monolayer graphene.  $\Delta E_{FM}$  is the difference between the Dirac-point and Fermi-level energies in the metal-doped graphene (graphene channel),  $\Delta V$  is the total built in potential difference,  $d_{eq}$  is the equilibrium distance, and  $d_I$  is the effective distance between the charge sheets in the graphene and metal. The red cross represents the Dirac cone, and thick red lines are used to denote the broadening of electronic states [18].

Carriers in the graphene under the metal can move ballistically or diffusively. In the ballistic regime, the only scattering process is that induced by coupling to the metal, which can be described by an effective coupling length  $\lambda_m = \hbar v_F/\pi n$ . On the other hand in the diffusive regime, we introduce a scattering mean free path  $\lambda$  with the contacted graphene segment. Here, this mean free path is defined as  $\lambda = \pi v_F \tau/2$ , where  $\tau$ is the scattering time. When  $\lambda >> \lambda_m$  the contact acts ideally otherwise in the diffusive regime where  $\lambda << \lambda_m$  we would expect a much reduced transmission probability. The  $T_{MG} = \sqrt{\lambda/\lambda_m + \lambda}$ probability transmission is defined as [17]. The transmission through the p-n junction with a coefficient of T<sub>K</sub> is based on Klein tunneling. The efficiency of the tunneling depends on whether the barrier potential is sharp or smooth, and the angle of incidence of the particle to the potential barrier.

Perfect transmission exists when we have normal incidence  $\theta$ =0 and  $T(\theta)$ =1, otherwise the transmission coefficient has a  $\cos^2(\theta)$  angular dependence and  $T(\theta)$ < 1 [18].

#### 2.9 The origins of metal-graphene contact resistance

As we have mentioned above, the contact resistance between graphene and metal electrodes is of crucial importance for achieving high performance of graphene devices [19]. Taking into account that high values of contact resistance are observed because of dipole formation at the interface due to charge transfer, perturbation of the graphene beneath the metal and contamination of the metal-graphene interface, many efforts have been done in order to overcome these obstacles.

#### 2.10 Optimization of metal-graphene junctions

#### 2.10.1 Metal choice

In 2011 Fengnian Xia et al, they concluded that to approach an ideal contact with the maximum transmission coefficient, one may choose a higher quality graphene which means choosing graphene with higher mobility can lead to a larger mean free path and therefore better carrier injection efficiency from metal to graphene, even at room temperature. Also, other metal deposition methods can be used to improve the morphology of the metal, which may lead to a smaller metal-graphene coupling length. In their study, they found that the contact resistance in palladium-graphene junction was  $110\pm20~\Omega~\mu m$ , nevertheless other metals can be chosen, which can lead to a higher metal-induced doping concentration in the graphene under the metal [17].

Beginning with the effort of the most appropriate choice of metal, in 2012 Eiichiro Watanabe et al, [20], measured the contact resistance between various metals such as Ti, Ag, Co, Cr, Fe, Ni and Pd in contact with graphene. The metals were deposited through e-beam evaporation onto graphene obtained via micromechanical cleavage of Kish graphite. The  $R_c$  value as small as  $700\pm500~\Omega$   $\mu m$  for Ti contact was obtained.

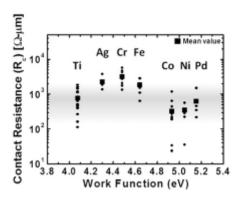

**Fig.(17):** Contact resistance as a function of metal work function. Circle marks depict the experimental data of the  $R_c$  at Dirac point for various contact metals (Ti, Ag, Co, Cr, Fe, Ni and Pd). Square marks depict mean values of the experimental data [20].

From their results they concluded that the contact resistance did not strongly depend on the metal work function but was significantly affected by the microstructure of the contact metals.

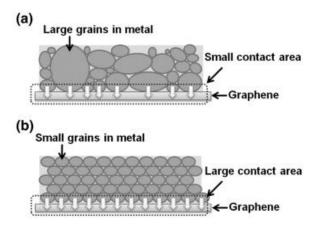

These results indicated that the fabrication process which provided the uniform metals with the small grains and the uniform interface is essential for obtaining the lower values of contact resistance.

**Fig.(18):** Schematic model of metal contact to graphene. (a) and (b) depict a schematic model of the metal/graphene junction for the large and small  $R_c$  values respectively. The model shows that  $R_c$  becomes smaller with increasing contact area between the metal grain and the graphene [20].

Remaining in the field of metal choice, in 2009 Ran et al., [21], and in 2013 X. Ji et al., [19], they investigated the physics of the metal-graphene contact based on the interaction that occurs between metals and graphene surface. X.Ji et al. in their report they performed density-functional theory (DFT) and non-equilibrium Green's function (NEGF) methods to study a series of metal/graphene complexes, including

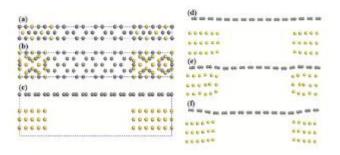

both single-side contacts (Al, Cu, Ag, Au, Pt, Pd, Ti/Gr) and double-side contacts (Pd/Gr/Pd). Their results indicate that the Rc is co-determined by vertical injection rate T<sub>B</sub> and lateral transport current I<sub>s</sub>. The tunneling barrier between metal and graphene vanishes for chemisorption metal/graphene interface of both single- and double-sided contacts. While the chemisortion metals would have advantages on T<sub>B</sub>, the physisorption metals have advantages on electron transport in graphene for preserving its conical electronic structure and high Fermi velocity. Considering both factors together, chemisorption metals would have smaller R<sub>c</sub> than physisorption metals, and double-sided contacts would lead to a significant reduction of R<sub>c</sub> for double-injecting electrons at high efficiency. For Pd which has the smallest R<sub>c</sub> of all sampled metals,  $R_c$  for double-side contact was 210  $\Omega$  µm and for single-side was 403  $\Omega$  µm respectively. Ran et al. in their study they found through first-principles calculation of contacts between graphene and 12 different metals that there exist two types of contacts depending on the strength of interaction between d-orbitals in metals and p<sub>z</sub>-orbitals in graphene. The carrier transport through these contacts is calculated using the extended Huckel theory-based non-equilibrium Green's function formalism. According to the Pd/graphene relaxed structure shown in Fig.18, the Pd/graphene distance increased from 2.3Å at the edges to 3.4Å at the center. This suggests that Pd/graphene contact is a combination of chemical and physical types of contacts. Pd atoms at the center are hard to form covalent bond since their fully filled 4d orbital are stable. However, Pd atoms at the edge suffer disorders to make an electron easier to be excited to the 5s orbital, then 4d orbital can interact with graphene's p<sub>z</sub>-orbital because the 4d orbital of graphene is barely below the Fermi level [19], [21].

**Fig.(19):** (a)-(c) calculated structure. (d)-(f) Contact structure after relaxation.(a) The x-y plane view of graphene contact with Cu, Co, and Ni. (b) The x-y plane view of graphene contact with Al, Ti, Au, Pd and Pt. (c) The x-z plane view of (b), (d), (e), and (f) are for Au/graphene, Ti/graphene, and Pd/graphene structure, respectively [21].

Except for the metal used for electrodes, the value of contact resistance depends on the synthesis method of graphene. To date the best reported  $R_c$  for lithographically defined contacts deposited onto exfoliated graphene flakes ranges from 200  $\Omega$   $\mu$ m to 500  $\Omega$   $\mu$ m. Contact resistance for contacts formed to epitaxial graphene on SiC has been reported to be less than 100  $\Omega$   $\mu$ m and with specific contact resistivity ( $\rho_c$ ) of order  $10^{-7}$   $\Omega$  cm<sup>2</sup>. Finally, the minimum values of contact resistance for chemical vapor deposition (CVD) graphene typically range from 500  $\Omega$   $\mu$ m to several thousand  $\Omega$   $\mu$ m [22].

#### 2.10.2 Cleaning methods

As was discussed earlier, residue contaminations come from graphene transfer onto a substrate (PMMA) or due to photolithography (photo-resist) and they increase the contact resistance. Many methods have been applied to eliminate these contaminations such as thermal annealing, O<sub>2</sub> plasma cleaning, CO<sub>2</sub> cluster and ultraviolet/ozone treatment. In the following sections we give a description of these methods.

## 2.10.2.1 Thermal annealing

Thermal annealing is process used for removing any residue contaminations from the surface of a material, for intrinsic stress liberation, structural improvement and surface roughness control [23]. Since in this thesis graphene is studied, we chose to focus on the influence of thermal annealing on graphene. As it is mentioned in Chapter 1, graphene may be fabricated by mechanical exfoliation from bulk graphite, SiC sublimation from bulk silicon carbide, and chemical vapor deposition (CVD) on catalytic metal films. To be promising for commercial or bulk production, graphene must be grown over large areas, for which CVD growth is most promising due to its high yield and quality. However, the large-area CVD graphene must be transferred from the catalyst growth metal to desired substrates such as SiO<sub>2</sub>. A common method for graphene transfer involves spin-coating a polymer, typically poly(methyl methacrylate) (PMMA) to support the graphene during etching of the catalyst metal and transfer to substrate. Once the graphene-PMMA stack is transferred, the polymer is removed either through solvent rinses, thermal annealing or a combination of two. The solvent rinses leave a layer of polymeric residue, and that can be partially removed by thermal annealing in gaseous atmospheres such as Ar, H<sub>2</sub>, H<sub>2</sub>/Ar, N<sub>2</sub>, forming gas (H<sub>2</sub>/N<sub>2</sub>) or in vacuum. Each of these gaseous atmospheres has different effects on graphene. For instance, it has been shown that ultra-high vacuum annealing can increase CVD graphene carrier mobility to approach what is measured in mechanically exfoliated graphene. Furthermore, the alternate annealing under hydrogen and oxygen atmospheres removes the majority of PMMA residues; however oxygen annealing introduces defects in the graphene lattice while annealing in H<sub>2</sub>/Ar atmosphere strongly dopes and strains graphene. In order to achieve the desirable effect of thermal annealing, an ideal combination of gas atmosphere and annealing temperature is required [23], [24].

## 2.10.2.2 Plasma Cleaning

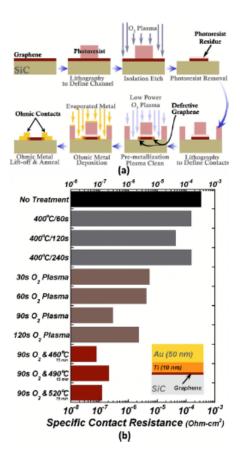

Plasma cleaning is suitable for removing organic contaminants, which remain after conventional cleaning [25]. It works primarily by bombarding the material surface with ions that dislodge surface impurities. Once liberated from the surface the impurities are drawn away under vacuum in a low pressure plasma system or ejected into the air through a pump [26]. Even though many gases can be used in this method of cleaning such as O<sub>2</sub>, H<sub>2</sub>, and Ar, it is essential to choose the correct plasma gas as gases react and work in different ways at removing contaminants [25]. For the scope of this thesis O<sub>2</sub> plasma is used prior to metal deposition because oxygen plasma cleaning prepares surface for subsequent processing by removing polymeric contaminants. Residue contaminants on the sample surface will be removed in two ways. First, the energy ions mechanically break up molecular bonds of the surface molecules and effectively blast the molecular particles off the sample surface. Second, atomic oxygen in the plasma readily reacts with the surface contaminants, breaking them up into smaller and more volatile pieces which easily evaporate off the surface. [27]. In 2011 Robinson et al. presented a method for forming high quality ohmic contacts to grahene, which improves the contact resistance by nearly 6000 times compared to untreated metal/graphene interfaces. In their report they evaluated the specific contact resistivity  $\rho_c$  using  $T_i(10nm)/Au(50nm)$  metal contacts on epitaxial graphene which were fabricated via standard UV lithography. The processing steps and treatments are illustrated in Fig.20. Specific contact resistivity continually decreases as the  $O_2$  plasma treatment time increases from 30 to 90s to  $4\times10^{-7} \Omega$  cm<sup>2</sup>. Upon reaching 120s,  $\rho_c$  begins increasing again suggesting the degradation of graphene. Post-processing heat treatments of contacts following a 90 s O2 plasma continues to improve  $\rho_c$ . Thermal treatments >450 °C are explored to remove the contaminations that may remain on the graphene layer following metal lift off. This combination of  $O_2$  plasma treatment and thermal annealing at 450 °C -475 °C for 15min resulted in optimum specific contact resistivity values of  $7.5 \times 10^{-8} \Omega$  cm<sup>2</sup> [28].

**Fig.(20):** (a) Process development (b) the specific contact resistance of a  $T_i$ Au contact is improved to  $4 \times 10^{-7} \Omega$  cm<sup>2</sup> when a "gentle"  $O_2$  plasma is employed and to  $7.5 \times 10^{-8} \Omega$  cm<sup>2</sup> when the  $O_2$  plasma treatment is combined with a 15 minutes furnace anneal in nitrogen forming gas [28].

#### 2.10.2.3 Ultraviolet/ozone treatment

UV/ozone treatment is another dry surface treatment technology which uses ultraviolet light and ozone to both clean and modify the surface of solids. Low-pressure UV lamps are used to generate a unique combination of wavelengths that both cleans the surface organic contaminants and improves the bond strength of the surface atomic layer [29]. UV rays cause organic compounds to be converted into volatile substances by decomposition and by strong oxidation during the formation and decomposition of O<sub>3</sub>. Organic compounds can be decomposed by irradiating them

with energy stronger than the bond energy. These excited contaminants, or the free radicals of the contaminants react with  $O_3$  to form simple molecules such as  $CO_2$ ,  $H_2O$ , N and  $O_2$  which are removed from the surface [30]. In 2013 Li et al. reported on the influence of ultraviolet/ozone on metal-graphene contact. They found that UV/ozone treatment removes resist residue prior to metallization and leads to a contact resistance between Ti(20nm)/Au(80nm) and CVD graphene of less than 200  $\Omega$   $\mu$ m [22].

## 2.10.2.4 CO2 cluster cleaning

This cleaning method uses a gas cluster as a physical removal medium of contaminants for cleaning CVD graphene. Since the freezing temperature of  $CO_2$  is relatively high at 194,5 K,  $CO_2$  clusters can be formed very effectively by adiabatic expansion through converging-diverging nozzle in a short time. The gas clusters are introduced to the surface of the contaminants, cooling and removing the contaminants without leaving secondary contaminants behind. This cooling or freezing of polymeric residues causes a difference in the thermal expansion coefficients between the contaminant and the substrate, and rapid volume shrinkage of the residues induces the contaminant to easily detach from the surface. In 2014 Gahng et al. applied this technique to improve the resistance between Cr(5nm)/Au(50nm) contact and CVD graphene. They found that the optimum value of the contact resistance was  $1.69 \text{ k}\Omega$   $\mu$ m at a flow rate of 201/min [31].

# 3. Dielectrics

#### 3.1 Introduction

Dielectrics are materials that are widely used in semiconductor devices, due to their high electrical resistance. In integrated circuits dielectric materials are used as insulating layers between conducting layers, diffusion and ion implantation masks, capping material for doped films to prevent loss of dopants, passivation layers to protect devices from impurities, moisture and starches, as interlayer films between the plates of a capacitor, and gate oxides [32].

#### 3.2 Definition of dielectrics

With the term 'dielectrics' we refer to these materials in which electrostatic fields could persist for a relatively long time without any charge flowing through them. [32]. When a dielectric material is placed in an external electric field, electric charges have an extremely different behavior compared to that in conductors. The external applied field causes the charges of dielectric materials to slightly shift from their equilibrium positions, and this shift causes the dielectric polarization. The positive charges follow the direction of the external applied field while the negative charges are displaced to the opposite direction. This orientation of the charged particles results in the generation of an internal electric field, smaller in magnitude compared to the external electric field, which partially counteracts the external electric field. The quantity that gives a measure of the dielectric polarizability is the relative permittivity or dielectric constant and is denoted as k [32], [33].

# 3.3 Parallel plate Capacitor

The capacitance of a flat capacitor with free space as an insulator between the two electrodes is given by the following equation, Eq.3.1,

$$C = \frac{\varepsilon_o A}{d} \quad (3.1)$$

where C is the capacitance,  $\varepsilon_0$  is the absolute permittivity, A is the plate area and d is the separation distance between the electrodes/plates. As we observe from the Eq.3.1, the capacitance density, which is equal to the capacitance given by Eq.3.1 divided by A, is directly proportional to the absolute permittivity and inversely proportional to the distance d [33].

Let us consider now the parallel plate capacitor as it is shown in the following figure, Fig.21.

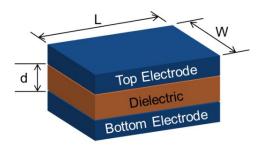

**Fig.21**: A basic parallel plate capacitor of length (L) and width (W) with spacing between the electrodes/plates (d). The image is adapted from [34].

In this case we can see that between the electrodes/plates there is a dielectric material and not air, therefore the capacitance density (the charge storage ability per unit voltage per unit area) increases by a factor k, where k is the dielectric constant of the medium that is placed between the electrodes/plates. So the equation Eq.3.1, is now transformed to equation, Eq.3.2 [33],

$$C = \frac{k \,\varepsilon_o A}{d} \quad (3.2)$$

From the last equation we can see that the higher dielectric constant k the higher the capacitance density is achieved. On the other hand the lower the separating distance between the electrodes/plates which corresponds to the thickness of the dielectric film the higher the capacitance density is achieved. This increase in

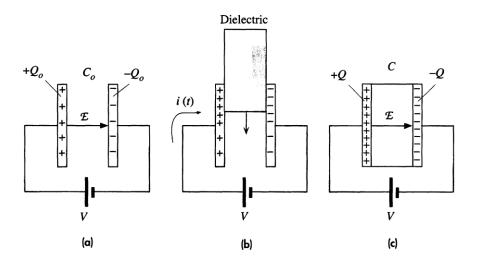

capacitance or capacitance density is due to the polarization of the dielectric material in which the negative and positive charges are displaced with respect to their equilibrium positions with the presence of an external electric field. More specifically, in the following figure, Fig.22a we see a parallel plate capacitor with vacuum as the dielectric material between the electrodes/plates. The plates are connected to constant voltage supply V. Let  $Q_0$  be the charge on the capacitor plates. For a given V and  $Q_0$  the capacitance  $C_0$  is given by the following equation, Eq.3.3 [33]

$$C_o = \frac{Q_o}{V} \quad (3.3)$$

The electric field between the plates can be calculated as follows

$$\mathbf{E} = -\frac{dV}{dx} = \frac{V}{d} \quad (3.4)$$

with a direction from high to low potential as it shown in Fig.22. When a dielectric film is placed between the plates while keeping the same voltage V, an additional charge is stored on the plates because of an external current flow. Thus, the charge on the plates increases from Q<sub>o</sub> to Q as shown in Fig22b,c. This charge increase results in a capacitance increase given by the following equation, Eq.3.5 [33]

$$C = \frac{Q}{V} \quad (3.5)$$

Using the fact that the dielectric constant k has been defined as the reflection of the capacitance increase or the charge storage ability by virtue of having a dielectric material we can define the dielectric constant as follows [47]

$$k = \frac{Q}{Q_0} = \frac{C}{C_0}$$

(3.6)

**Fig.22:** a) Parallel plate capacitor with free space between plates, b) as a slab of a dielectric material is inserted between the plates, there is an external current flow indicating that more charge is stored on the plates, c) the capacitance has been increased due to the insertion of the dielectric film. The image is adapted from [33].

As it is mentioned above this charge increase is due to the polarization which is caused by the external applied field. More specifically, when a dielectric material is placed in an external applied field their atoms and molecules are polarized and as a result positive and negative charges there are at the edges of the material while the total charge of the material remaining zero. These bound charges at the dielectric surfaces are called surface polarization charges. The polarization is denoted as **P** and is defined as follows [33]

$$P = \frac{1}{Volume} [p_1 + p_2 + \dots + p_N]$$

(3.7)

Where  $p_1, p_2, ..., p_N$  are the dipole moments induced at N molecules in the volume [47]. To calculate the polarization of the polarized dielectric we regard the dielectric as a system which has a dipole moment  $p_{total}$  that is directed from the negative to the positive surface polarization charges. The  $p_{total}$  is given by the following formula

$$p_{total} = Q_p d \ (3.8)$$

where  $Q_p$  represent the surface charges that are separated by distance d. Thus, the magnitude of the polarization that defined as the total dipole moment per volume (=Ad) is calculated as [33]

$$P = \frac{Q_p d}{Ad} = \sigma_p \ (3.9)$$

Where  $\sigma_p$  is the surface polarization charge density. The last equation gives only the magnitude of polarization. The charge per unit area that created on the surface of a polarized material is equal to the component of the polarization vector normal to this surface [47]. At this point it is necessary to define the relation between polarization and electric field using the quantity of the electrical susceptibility  $\chi_e$ , [33]

$$P = \chi_e \varepsilon_o E$$

(3.10)

As we can see the above equation, Eq.3.10, gives the dependence between the polarization and the electric field. So, the next step is to find a relation between the electric field (or polarization) and dielectric constant k. The electric field absence of the dielectric layer between the two electrodes/plates is [33]

$$E = \frac{V}{d} = \frac{Q_o}{C_o d} = \frac{\sigma_o}{\varepsilon_o} \quad (3.11)$$

where  $\sigma_o$  is the surface charge density of the free charges that are stored on the capacitor plates. Presence of the dielectric layer the electric field remains the same and is equal to  $V/_d$ . But as we discussed above due to the dielectric layer the charge increases from  $Q_o$  to Q, and the new charge is equal to  $Q = Q_o + Q_p$ . Using the definition of the free surface charge density and the definition of the surface polarization charge density, we can rewrite the expression for the new charge as follows [33]

$$\sigma = \varepsilon_o E + \sigma_p \ (3.12)$$

Now, we are ready to extract the expression for the dielectric constant. In the above equation, Eq.3.12, we constitute  $\sigma_p = P$  and  $P = \chi_e \varepsilon_o E$  and we obtain that [33]

$$k = \frac{Q}{Q_o} = \frac{\sigma}{\sigma_o} \quad (3.13)$$

The last equation, Eq.3.13, gives the relation between the dielectric constant and the surface charge density on the plates of capacitor, and now is completely

understood how high values of dielectric constant imply capacitance density increase [33].

# 3.4 Dielectric strength