## Chapter 1

# Introduction

Nowadays, even though the necessary bandwidth for the creation of Broadband Intergrated Services Network (BISDN) is provided by advanced fiber optic technology, this creation still remains a challenge. The major difficulty lies in the construction of switching circuitry that can cope with the bandwidth provided. The concept of Asynchronous Transfer Mode (ATM) – the switching technique selected for the realization of BISDN – is presented in chapter 1, followed by an overview of existing approaches for building ATM switches, and some notes on the organization of this thesis.

## 1.1 Broadband ISDN and Packet Switching

The rapid evolution of high speed telecommunication technologies has prompted the introduction of BISDN – an all-purpose digital network. It will support a wide variety of applications in an intergrated and unified fashion. There is an enormous difference in the requirements for bandwidth and quality of service between many of the applications supported by BISDN and those supported by today's digital networks. For example, High Definition Television (HDTV) will require over 100 Mbps bandwidth, with acceptable error probability up to five orders of magnitude smaller than that of today's digital telephony. In addition, a key requirement of BISDN is flexibility – the same network will be used for all services, including services whose characteristics have not yet been defined.

A key point for the realization of BISDN is the transfer mode (switching technique) that will be used. Early thoughts of researchers and study groups considered two approaches: circuit switching or Synchronous Transfer Mode (STM), and packet switching or Asynchronous Transfer Mode (ATM). Traditionally, circuit switching has been used for connection oriented

#### Introduction

applications such as telephony, and packet switching has been used for data transfers. Today it seems very difficult to achieve a multiservice (i.e. multibit rate) network by using circuit switching [Minz89]. This is because the bandwidth required by the various services depends both on the coding algorithm and the state of the art in technology. These parameters are evolving so fast that whatever the choice of the channel bit rate, it may prove inefficient in the near future. It was this inflexibility of STM, that led to the selection of ATM as the transfer mode of BISDN. In the following paragraph we will briefly describe the most important notions of the current ATM standard.

The concept of ATM, as defined by CCITT Study Group XVIII in [CCIT90], is simple and almost identical to that of the traditional packet switching. The usable bandwidth is divided into fixed-size information-bearing time slots, called cells. Each 53-byte cell consists of a 5-byte header (for routing and multiplexing purposes) and a 48-byte information field – the resemblance to the packets of traditional packet switched networks is obvious. The cells are multiplexed and routed by using Virtual Circuits (VCs). This implies that all services at the network layer are connection oriented. The switching and routing functions are performed by using the Virtual Circuit identifier (VC ID) field of the cell header. In addition, the current draft ATM standard defines the notion of Virtual Path (VP), which is an aggregation of many VCs that are being routed together in a segment of their itinerary in the network. Another important topic, addressed by [CCIT90], is the classification of various applications according to their quality of service requirements (end to end delay, error and loss rate etc.). Four classes of services have been defined for: circuit emulation, variable bitrate video, connection oriented data transfers, and emulation of connectionless services. This definition implies that a priority-based multiplexing mechanism must be implemented in the network layer of BISDN: it must differentiate among cells in different VCs according to information provided during connection establishment, and give preferential treatment to higher priority cells.

Some of the above functional requirements have more or less been implemented in traditional packet switching networks, so one may argue that the implementation of BISDN presents no difficulty with the available technology. However the main difference between traditional networks and BISDN is that in the latter the offered bandwidth is at least two orders of magnitude larger. Thus, it is evident that there is almost no chance of implementing the network layer functions in software, as done in traditional packet switching networks [Toba90] – instead all of them must be implemented in hardware. So, the main challenge is to built fast packet switches being able to handle rates in the order of 100,000 to 1,000,000 packets<sup>‡</sup> per second per input line, and implementing the described functionality in hardware. Additionally, these switches must be able to cope with the peculiarities present in the traffic characteristics of each service. The next section

<sup>†</sup> In this work the terms packet and cell will be used indistinguishably

describes the functionality that an ATM switch must have and briefly reviews the existing architectures that have been considered for implementing ATM switches.

#### **1.2** Overview of Fast Packet Switch Architectures

An  $N \times N$  packet switch is a box with N inputs and N outputs which routes packets arriving on its inputs on the appropriate outputs. Usually all input and output lines have the same transmission capacity and all packets are of the same size. There is no constraint on the destination port of the packets arriving at a given time on the inputs of the switch, so more than one packets may be required to be forwarded to the same output port simultaneously. Such an event is referred as an *output conflict*. Due to output conflicts, buffering of packets within the switch must be provided.

Besides the basic routing and buffering functions performed by a switch some other functions may be required. The first is *multicast* operation, required by some applications such as video-conferencing and commercial TV-channel distribution. A switch capable of multicasting must be able to replicate a packet at several of its output ports on demand. Second there is the *priority* function. As explained in the previous section, a switch implementing a priority function must be able to differentiate high priority packets and prefer to serve them (i.e. forward them to their destination port) before other packets of lower priority. Another function that may substantially improve the overall network performance is *virtual cut-through*. The term has been originally introduced in [KeK179]. It represents the ability of the switch to start the transmission of a packet over an output port, as soon as its destination port has been determined, without having to wait for the complete packet to arrive into the switch. The last function is *flow control*. The need for flow control is imposed by the fact that the buffer space within a switch is limited. As a result, the bursty nature of traffic may lead to unacceptable packet loss rates, when a switch in the network transmits packets without having any information on the buffer occupancy of the switch that receives them.

Several architectures for implementing fast packet switches have emerged in recent years. In [Toba90] they are classified into three main categories; namely: *shared memory, shared medium,* and *space division.* The rest of this section is devoted to a brief description of these three types.

#### **1.2.1 Shared Memory Switches**

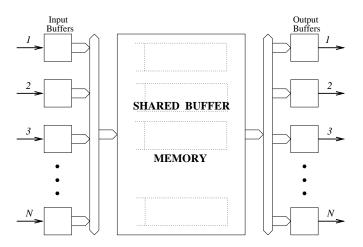

An abstract model of the shared memory switch architecture is depicted in figure 1.1. Its basic component is a "virtually" dual-ported memory shared by all input and output lines. Packets arriving on input lines are stored to the common memory. Internally to the memory, the cells are organized into separate queues, one for each output line. Packets are simultaneously retrieved from the output queues and transmitted over the output lines. The two main constraints of the

Figure 1.1: Basic structure of a shared memory switch architecture

shared memory architecture as identified in [Toba90] are that: (*i*) the time consumed by the routing decision must be sufficiently small to keep up with the flow of incoming cells, and (*ii*) the memory bandwidth should be sufficiently large to simultaneously accommodate all input and output traffic. If N is the number of ports and B the port bandwidth, the shared memory bandwidth must  $2 \times N \times B$ . However, as can be seen in [DeCS88] and [KEOK89] these two constraints do not impose any insurmountable design obstacles. Additionally, shared memory switches present a great conceptual resemblance to traditional packet switches. Thus, the expertise gained by the construction of these networks may be transferred to BISD networks, if elegant ways can be found to implement old algorithms, while conforming with the new high speed requirements.

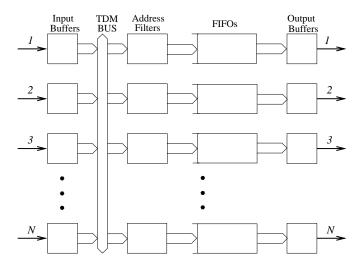

Figure 1.2: Basic structure of a shared medium switch architecture

#### 1.2.2 Shared Medium Switches

The shared medium approach presents great similarity to Time Division Multiplexing (TDM) switches : All packets arriving on the input ports are synchronously multiplexed onto a common bus (figure 1.2). Each output line is connected to the bus via an address filter and an output FIFO. The address filter of a particular output port, based on the VC ID of a packet, determines whether or not the packet on the bus has to be written into the port's FIFO. The main constraint of the shared bus architecture is that the common bus must operate at  $N \times B$  speed and each output FIFO at  $(N+1)\times B$  speed. Some shared bus architectures that can cope with this constraint have been presented [SNSTI90]. Nevertheless, an inherent disadvantage of the shared medium architecture is the partitioning of the available storage to N distinct portions. Thus, in cases of "hot spot" traffic [PfNo85] much of the available storage will be wasted.

#### 1.2.3 Space Division Switches

In space division switches, multiple concurrent paths are established from the inputs to the outputs. Thus there is no need for any buffering component in the switch, to have bandwidth more than  $2 \times B$ . The major problem of space division based fabrics is *internal blocking*, i.e. the state in which it is impossible for the internal fabric to set up concurrently all the required paths. The space division switches are classified into three main categories: (*i*) *crossbar fabrics*, (*ii*) *banyan based fabrics*, and (*iii*) *fabrics with*  $N^2$  *disjoint paths*.

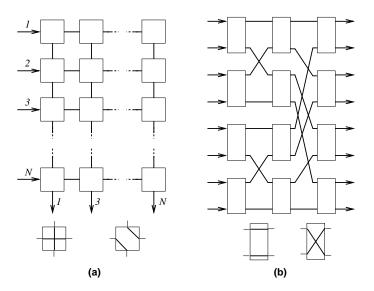

Figure 1.3: Crossbar (a), and Banyan (b) switches and switching elements

The *crossbar fabric* consists of a square array of  $N^2$  crosspoint switches each one corresponding to one input output pair – see figure 1.3(a). If there is no output conflict all incoming packets can reach their destinations. In case of an output conflict only one packet can be

#### Introduction

routed to the desired output; those remaining either have to be dropped or buffered somewhere. Several designs utilizing the crossbar architecture have been presented. Some of them have their buffers placed in the inputs [FrTa88], and others in the crosspoints of the switch. The main drawback of crossbar fabrics remains their limited scalability, due to the  $N^2$  cost of the crossbar circuit.

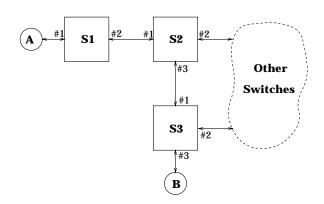

The *banyan switching fabrics* are based on a class of multistage interconnection networks that consists of  $\log_2 N$  stages, each one comprising N/2 binary switching elements. The interconnection lines between the elements are placed in such a way as to allow the formation of a unique path from each input to each output – see figure 1.3(b). The establishment of such a path is accomplished by using a self routing procedure: the switching element reached by a packet at *stage<sub>i</sub>*, is set to the appropriate cross or bar state according to the *i*<sub>th</sub> bit of the packet's destination number. The major problem of banyan based switches is *internal blocking*. It occurs whenever two packets arrive simultaneously at a switching element and request the same output link. The existence of such conflicts – which may occur even in the absence of output conflict – introduces severe performance limitations. Several alternate architectures have been proposed to circumvent this performance degradation. Examples are buffered banyan switches [Turn88], sorting banyan switches (usually referred to as Batcher/banyan) [GiLS90], and multiple banyan switches (such as Tandem Banyan or parallel Banyan investigated in [KwT091] and [ChAT91]).

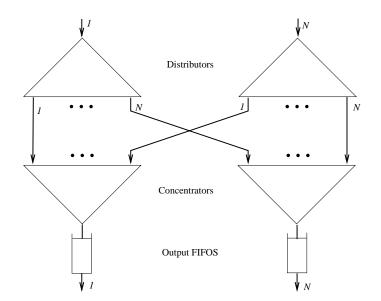

Figure 1.4: An abstract model of the  $N^2$  disjoint paths switch architecture

The final class of space division switches is the *fabrics with*  $N^2$  *disjoint paths*. This class of switches avoid blocking by providing as many concurrent paths as needed, to handle all possible packet arrival patterns. They distribute the packets arriving at each input port to N bins, one for

each output, and the packets destined to each output are multiplexed into a single queue (see figure 1.4). The main drawback here is the limited scalability, as with crossbar switches. Several approaches have been presented to overcome this drawback. Some of them (e.g. [YeHA87]) are based on the observation that under some typical traffic patterns, the number of packets destined to a given output is small compared to N, and thus there is a value L such that if every output port receives up to L packets, the desired cell loss rate is achieved. Others (e.g. [WaT091]) based on the same observation, try to limit the number of disjoint paths, by organizing the switch as a binary tree, in which each branch constitutes a group of paths that is shared by all the packets destined to a subset of output ports. Although these revised versions manage to limit the cost of this type of switching fabric, their complexity still remains high. Additionally they suffer from the inability to guarantee zero packet loss rate for a specific class of service, unless they incorporate additional input buffering and a flow control mechanism (which will further increase their complexity).

## **1.3** Overview of this work

As can be inferred by the presentation of the previous section, researchers throughout the world have studied extensively the issue of fast packet switching for ATM. However Coudrese, et *al.*, in [CoST88], note that there is a lack of efficient buffer and bandwidth management techniques in Broadband Packet Communications. In addition, they note that *"computationally efficient algorithms to decide how to combine traffic flows are needed to allow rapid route selection in an operational switch"*. Furthermore, the concept of quality of service does not explicitly appear in most of the existing architectures, with the exception of the ring local area network switches of Columbia's MAGNET (see [LaTG90a] and [LaTG90b]). The present work – an extension of [Kate87] and [KaSC91] – attempts to focus exactly on these issues. It defines a switch architecture, that provides the network manager with powerful mechanisms for buffer and bandwidth management. In addition, it is suitable for single chip VLSI implementation; the resulting chip can be used as a building block for constructing distributed or concentrated switches.

Chapter 2 of this thesis discusses our view of the overall Broadband Network architecture as the context in which the studied switch chip will operate. Chapter 3 deals with the architecture of the switch chip; it mainly discusses the major architectural decisions and presents some alternatives. Chapter 4 discusses the implementation issues and describes in detail the circuit design, layout, and simulations performed, in order to prove that the proposed architecture is feasible, in the contemporary CMOS VLSI technology. Finally, Chapter 5 provides some conclusions and briefly presents the future extensions of the present work

# Chapter 2

# An Approach to the Broadband Network Architecture

Given the flexibility provided by packet switches, we still need efficient ways to fully utilize the resources of a network. That is, the design of a switch has to focus not only on efficient routing and minimal packet loss due to output conflicts, but also on the achievement of maximum utilization of network resources. The methodology that leads to better bandwidth utilization is presented in § 2.1, followed by a preliminary investigation of possible allocation policies for various types of traffic (§ 2.2). The chapter concludes by presenting how a broadband network can be constructed by connecting together many copies of a small switch component that implements the proposed techniques (§ 2.3).

## 2.1 A Possible Use of Congestion in Broadband Networks

The term "congestion" in conventional networks is used to signify the situation where "*perfor-mance degrades due to too much offered load*" [Tane81, p. 216]. However in [Kate87], it was observed that offering to the network more traffic than its carrying capacity, is a prerequisite for achieving continuous and full utilization of all its bandwidth. That proposal has been the cornerstone of the present work, so we will briefly review it here.

It is obvious that in order to fully utilize a certain resource, the requests for using that resource must be equal to or exceed the capacity of the resource – otherwise, if there is a lack of sufficient requests, the resource would necessarily remain underutilized. But why would one choose to fully utilize the bandwidth of the links of a network rather than some other network resource? The main observation that justifies Katevenis' approach is that buffer memory is no

longer a scarce resource in Broadband Networks – instead bandwidth is a more precious resource. This follows from a rough relationship that the two have, "(*buffer space*) = (*throughput*) × (*round-trip delay*)", which when converted to numbers, amounts to about 1 Kilo-Byte per kilometer and Giga-bit/second. Even when this refers to buffer space per virtual circuit or virtual path, the cost of the total buffer space implemented using a few DRAM chips is still much less than the cost of e.g. the long optical fiber that they correspond to [Kate87]. Two conclusions follow.

The first conclusion is that it is better to buffer packets than to drop them and later retransmit them. For this reason a hop-by-hop flow control mechanism must be implemented throughout the net. The basis of this mechanism can be a sliding window protocol which utilizes backward transmitted "permits". Every switching or terminal node in the network sends a "permit" (token) to its upstream neighbor whenever room for more packets is available in a local buffer. This guarantees that buffers will never overflow, and packets will never have to be dropped, if they encounter a congested area somewhere in the network. On the other hand the flow of packets must be able to proceed at its maximum rate whenever there is nothing to stop it. For this reason the window size (buffer space) must be roughly at least as large as the desired peak throughput times the "round-trip delay"; the latter is the total time for a flow-control token to travel back, for the upstream neighbor to respond to it, and for the data packets to travel forward from that neighbor to the local node.

The second conclusion is that it is better to fully utilize the available link throughput than to economize on buffer space. In traditional networks, minimization of the required buffer space is achieved (*i*) by sharing that space among all VCs, and (*ii*) by guaranteeing that the traffic load offered to each link is below the link capacity by a certain safety margin. If the network fails to satisfy property (*ii*) on some link, a "chain-reaction" phenomenon takes place. The packets of the VCs which encounter heavy traffic on the congested link get concentrated and stay in the (shared) buffers of the nodes upstream from this link, taking up buffer space which thus becomes unavailable for other VCs. These other VCs then get slowed down, even though their own path may not pass through heavy-traffic areas. This is the phenomenon of high traffic load (*congestion*) in a part of the network causing the dramatic decrease of the network capacity in a much wider area. In order to avoid such a situation a different approach to buffer allocation can be adopted: for those classes of traffic and those VCs for which it is not feasible or desirable to guarantee property (*ii*) above, *dedicated* buffer space to each VC can be provided.

This buffer preallocation policy solves the problem of undesirable interactions between VCs [Tane81] and the store and forward deadlock [MaZa90], since it makes VCs independent of each other. In this way, congestion has no negative effects and it even becomes desirable, since it is needed for achieving full utilization of the network throughput. In the absence of congestion, the network does not have to make any bandwidth (throughput) allocation decision; since the offered traffic is less than the network's capacity, all the packets that are sent will eventually get-

through. When congestion exists, it is the network itself that has to make the bandwidth allocation decisions, i.e. it has to arbitrate among all the VCs that try to use more throughput than there is of it. In that case, the cell multiplexing method (which cell to forward next along an outgoing link) is the primary means of making these decisions. Priority classes obviously control this allocation, but in a very crude manner. If within a congested priority class (hopefully, that will be the *lowest-priority* class) all the cells of all the VCs are placed on a single queue and serviced in a FCFS (FIFO) order, then an "unfair" allocation of the available throughput is made: those VCs that "merge into" a path at later stages get more service than the ones which merged earlier. If each VC has a queue of its own, instead, and these queues are served in a round-robin fashion, then a "fair" allocation is made. Round-robin scheduling means circularly scanning all the VCs (of a given priority) and transmitting one cell from each of them that is found to be "ready"; a VC is ready if its buffer on the local node contains at least one packet and its buffer on the destination node is known to have empty space for at least one packet. The round-robin scheduling of cells (i) equally distributes all the available link throughput to all the virtual circuits that can use it, and (ii) if some virtual circuits do not need to or cannot use all of their share of throughput, then they get allocated as much of it as they need, and the remaining portion is equally distributed to all the other VCs that can use it. Round-robin scheduling was initially proposed in [BCHW72], used in TYMNET [Tyme81], and was also proposed in [Morg89] and studied in [DeKS89]. An extension that gives more power to the basic round robin cell multiplexing is to use weighted round robin scheduling – certain VCs are visited more than once during each scanning cycle, in proportion to a prescribed "frequency of service weight", and thus they receive a proportionately higher share of bandwidth.

The satisfactory function of the discussed scheme depends on whether the kind of traffic presented to the network requires minimal loss probability, and on whether it is statistically expected to try to overload the network. Not all kinds of traffic have the above two characteristics – e.g. digital telephony requires a constant bandwidth of 64 Kbps and may tolerate a reasonable rate of packet loss. Therefore, providing individual buffers to each VC in the network may not always be the most reasonable choice. The next section discusses the characteristics of various kinds of traffic, and presents appropriate buffer allocation schemes for each of them.

#### 2.2 Quality of Service and Network Resource Allocation

How should network resources be allocated to a specific service call, to achieve better service performance? Answering this question requires knowledge of the diverse characteristics and requirements of various types of service. A classification of services according to some of their characteristics has been proposed in [CCIT90]. This classification – based on: isochronality, bandwidth stability, and connection mode (see table 2.1) – may be sufficient for determining

various protocol functions, but is incomplete when one tries to answer the above question. The characteristics that must be used in such case are whether the service is: (*i*) loss sensitive – i.e. its performance decreases by packet loss, and (*ii*) delay sensitive – i.e. its performance is affected by end-to-end or cell-to-cell delay [OhON88]. In this section we will attempt to identify which resource allocation scheme can be used for the various services, when the multiplexing mechanism used is the weighted round robin method explained in previous section, in combination with a priority mechanism – i.e. the scheduling is done with respect to priority classes, and within a class the bandwidth is allocated in proportion to prescribed weights.

| Table 2.1 : CCITT Service Classes        |                     |                |             |                |  |

|------------------------------------------|---------------------|----------------|-------------|----------------|--|

|                                          | Class 1             | Class 2        | Class 3     | Class 4        |  |

| Timing between source<br>and destination | Related             |                | Not Related |                |  |

| Bitrate                                  | Constant            | stant Variable |             |                |  |

| Connection mode                          | Connection Oriented |                |             | Connectionless |  |

The definition of the first class above, relates to Quasi-STM services – using [OhON88] terminology. Digital telephony may be considered as a typical representative of this class. Although voice traffic may have a bursty nature when silence suppression is used, the most commonly used PCM or ADPCM coding results in a constant rate of 64 or 32 Kbits/s respectively. The principal requirement of voice services is bounded delay. Voice packets that are not delivered to their destination within some period have to be discarded. Although the exact length of the maximum tolerable period is subject to debate, it is generally accepted to be in the range of 100-600 ms. In addition a packet loss rate up to 5% is considered as acceptable by most quality standards. The above requirements call for high priority voice VCs in our scheme. This implies that in most switching nodes in the network, voice VCs will not be congested, because they will be serviced as soon as possible when they arrive at a node, and hence they will not need dedicated buffers or even flow control.

The second class of services has been created mainly for classifying Variable Bitrate Video (VBV). VBV requires bandwidth in the range of 2-150 Mbits/s, depending on the frame resolution. The end-to-end delay requirements for video services depend on the type of the service: for one way television applications such as transmission TV, delay is irrelevant compared to that of two way applications like video-conferencing. On the other hand video as an information carrier is complementary to sound, and must stay synchronized with it. The acceptable cell loss rate varies, depending on both the coding algorithm, and the amount of motion in the scene. Taking into account the above requirements, we may infer that a similar policy to telephony can be

applied for VBV. The video traffic VCs must have high priority –in fact the same with that of their corresponding sound VCs. In addition, shared buffer space can be provided to them in most cases. The bursty nature of video traffic does not seem to impose any particular problem since, when many video sources are combined – e.g. in one virtual path – the total rate exhibits less burstiness [KaVe89]. Thus, in case the total bandwidth of the aggregated VCs is guaranteed to be smaller than the link's capacity shared buffers can be assigned to the video carrying virtual paths.

Typical examples of the third class of services are interactive communications and massive data transfers. Interactive data traffic is highly bursty and has moderate end-to-end delay requirements. In addition, although packet loss may be tolerable it is better to be avoided. These requirements show that interactive data VCs can have moderate priority and that it is better to use flow control; dedicated buffers must be assigned to them if the bandwidth they require is not guaranteed to be less than the link's capacity (e.g. graphics terminals). A higher priority can be used, in case the transaction the VCs correspond to requires bounded end-to-end delay (e.g. critical military or government transactions). On the other hand, massive data transfer traffic is the perfect candidate for becoming the low priority (congested) class in our system. It is loss sensitive – a lost packet must be retransmitted – and no time critical. Hence, the data carrying VCs must use dedicated buffers and flow control, and their frequency of service weight must be set to a value according to the agreed cost of call.

Class 4 corresponds to connectionless data services: the type of services similar to these of user datagrams in conventional packet switched networks. Since BISDN is by definition a connection oriented network, this type of service will be emulated by the means of a connectionless server. A user that requires such a service will be connected to the server, which subsequently will route the cells to their destination via a semi-permanent virtual path [CCIT90]. Connectionless services are expected to generate highly bursty traffic with no guaranteed maximum bandwidth. Therefore the most reasonable choice would be to treat the connectionless service VCs similar to massive data transfer VCs, i.e. assign them low priority, provide them dedicated buffers, and use flow control to increase their reliability.

Although no special class has been defined for supporting information transfer for network management and control, we cannot ignore the stringent requirements of this type of traffic. Network management traffic requires minimum delay – e.g. cells carrying flow control information must reach their destination as soon as possible in order to minimize round trip delay. In addition, it is loss sensitive – e.g. VC setup packet loss is not tolerable. These requirements clearly show that network management VCs must be assigned top priority in our system and use hop-by-hop flow control to ensure that their cells will not be lost.

The above discussion did not attempt to define a set of general rules, that solve all the problems that can occur in a real integrated network. An establishment of such an overall policy is not a simple matter and is beyond the scope of this study. Nevertheless, we can easily see that adding an option for shared buffering to the dedicated buffering scheme described in the previous section, leads to better buffer utilization while it still maintains maximum bandwidth utilization. Additionally, it can be seen that four levels of priority are enough for supporting: (*i*) network management traffic, (*ii*) critical interactive communications (e.g. police, ambulance, government or military communication channels), (*iii*) real time voice, video, and data, and (*iv*) massive data transfers. This priority-based mechanism along with the weighted round robin scheduling, gives the network manager a powerful tool for allocating the available bandwidth fairly, while in combination with some other policies (e.g. call admission, bandwidth quota etc.) contributes to satisfying the quality of service requirements of the provided services.

#### 2.3 Hierarchical Organization of Broadband Networks

A large system can be constructed by replicating a small number of building block modules. This approach, which offers greater flexibility, modularity, and incremental expandability, can be adopted for the construction of the Broadband ISDN networks as well. For this purpose, it is sufficient to develop a number of building block components that plug together with each other implementing the appropriate functions.

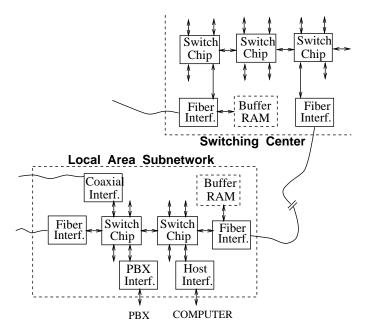

Figure 2.1: Envisioned network architecture

Figure 2.1 shows our view of the broadband network architecture. The network can have arbitrary size and topology, but is constructed using a small number of different VLSI

components. It consists of parts that are separated by considerable physical distance from each other via links such as coaxial cables, optical fibers, microwave links, etc. One part of the network, that resides at one physical location, may be constructed with a few chips on a small printed circuit board (PCB), constituting a small scale subnetwork. Other parts of the network – e.g. large centralized switches - may incorporate thousands of chips on several boards. An entire such subsystem, or appropriate parts of it, will be concentrated enough for its core to operate synchronously and for its chips to communicate via bit parallel links (e.g. the lower left part of figure 2.1). Any such subsystem can be built using a few different types of chips. The switching fabric can be made of chips of a single type; various service equipment can be connected to it via special interface chips. The external links will be connected to the switching kernel by using special link interface chips for each particular type of external link. By using this approach the goals of network flexibility and incremental expandability are met in a straightforward way - new subsystems with particular configurations can be constructed easily by plugging together the appropriate building block chips on a board, and adding it to the existing system. Furthermore, a large switching systems may be made out by smaller ones, following any topology that the network designer will choose depending on the expected pattern of traffic and the tolerable amount of internal blocking.

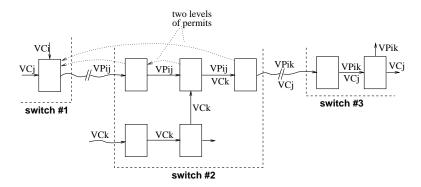

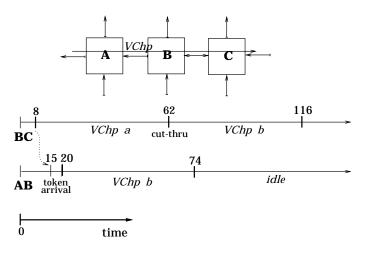

Figure 2.2: Routing and flow control of VCs and VP's

The network architecture just described has a hierarchical nature. The higher levels of this hierarchy – i.e. the large composite switches and local area subsystems at the end points of long links – will be able to serve thousands of end user VCs. As already described, these large systems will be constructed "hierarchically", by connecting together multiple, smaller switches, which will constitute the lower levels of the hierarchy. The traffic seen by these lower level switches will contain fewer but composite virtual circuits – "virtual paths" (VP's) using the terminology of CCITT – which will be derived by grouping together multiple end user VCs over a common portion of their path in the network. This is illustrated in figure 2.2 :  $VC_i$  and  $VC_j$  are merged at the fiber interface of the composite switch #1 and follow the same path through the

component switches of the composite switch #2. Subsequently, at the exit point of switch #2 they are separated, and  $VC_i$  is merged with  $VC_k$ , while  $VC_j$  follows a different path through the component switches of switch #3.

The flow control policy described in § 2.1 can be applied in the case of composite VCs as well [Kate87]. Two levels of permits are needed in this case, as illustrated in figure 2.2. The lower level corresponds to the merged  $VP_{ij}$  and is transmitted from each switch chip lying on the path of the VP to its upstream neighbor. The higher level refers to the individual VCs and is transmitted from the interface chip in which the two VCs are separated, to the interface chip in which they are merged. We must mention however, that such an aggregation of VCs cannot always be applied using as only criterion whether or not two or more VCs follow the same path within a composite switch. For example, it is not practical to merge a VC carrying voice traffic with one carrying non interactive data, due to their different priority and the different buffer allocation policies that must be applied to each of them. Nevertheless, we anticipate that in a large composite switch a substantial number of end user VCs will be aggregated, thus leading to reduced buffer and routing table storage requirements in the switch chips.

In order for the bandwidth allocation to be fair, the multiplexing of multiple VCs into composite ones must be performed by using a round robin mechanism. This means that the link interface chips, besides the considerable amount of buffer storage, will also need to incorporate special hardware for implementing the round robin multiplexing. This may be a severe limitation for the single chip implementation of these building blocks, especially in cases in which they reside at the end point of a long high speed link (recall that each VC needs approximately 1 Kbyte of storage per kilometer and Gbit/sec). However, in such cases, it is acceptable to connect external RAM chips to the link interface chips without significantly increasing the overall cost of the system, since the cost of memory chips will be only a small fraction of the cost of the corresponding link. The cycle time of this external RAM modules will not impose any problem, since the data path for accessing them can be made wide enough to match the link bandwidth. The number of additional pins needed for this purpose will be reasonably small, e.g. 32 data pins will be needed for a 400 Mbits/s link interface connected to a RAM module with 40 ns cycle time.

Having defined the environment in which the switch chips will operate, it is easy to see that their required functionality allows a single chip implementation. This study discusses the architecture and implementation of such a single chip switching building block. Our current design is for a 4×4 switch with a throughput of 400 Mbits/s in each direction of its 4 links. The parallel link interface of the chip allows it to be directly connected as described above to other switch chips or to interface chips. Each link is capable of routing 256 composite VCs, 128 of which have a dedicated buffer space of one cell; the remaining 128 of all links (totally 512) share a common buffer pool of 64 cells. The stored cells are selected for transmission by using the priority class of their corresponding VC and according to a weighted round robin policy implemented in

hardware. The flow control mechanism is straightforward, given the buffer space that can be occupied by each VC and the small round trip delay – every time a cell is selected for transmission a permit is send backwards indicating that there is room in the local buffer for receiving one more cell. Another feature that is essential for the performance of the composite switches composed by using this building block chip, is that the chip implements a "virtual cut-through" mechanism, thus dramatically reducing the latency of the non-congested VCs in a large composite switch. These features of the switch chip are described in the next chapter, together with the trade-offs that led us to choose them.

# Chapter 3

# **The Switch Chip Architecture**

In this chapter we present the hardware architecture of the building block switch chip, and discuss the principal alternatives that were considered. The presentation of the high level architecture is intermixed with micro-architectural discussions, since many of the decisions were affected by implementation issues.

We present first the overall block diagram and operation of the chip, then we discuss the organization of its storage parts (routing and buffer memories). Subsequently, we describe the weighted round robin multiplexing mechanism and the way we augmented it with priority classes. After a calculation of the round trip delay, the chapter concludes with a discussion about the initialization of the switch chips in a composite switch.

## **3.1 Block Diagram and Operation of the Chip**

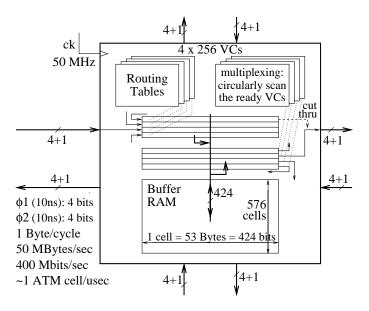

Figure 3.1 presents the overall block diagram of the current switch chip design. As mentioned earlier, this design is for a 4×4 switch chip, with a throughput of 400 Mbits/s on each one of its four links in each direction, but the architecture can be extended with a more advanced fabrication process and packaging technology up to a dozen of multi Gb/s links. The current chip design can route and multiplex 256 virtual paths<sup>†</sup> on each of its links. The format of the packets recognized by our architecture is simple: 53-byte long cells with 2-byte header (one byte for VC ID and one byte for control, as described in § 3.9). This format is not compatible with the

<sup>&</sup>lt;sup>†</sup> from now on we will refer to the terms virtual circuit and virtual path indistinguishably, since our chip cannot signify the difference between the two of them.

standard cell format described in [CCIT90], but this incompatibility is not a problem: our system will perfectly cooperate with systems following the CCITT standard if a simple header translation is implemented in the (fiber and media) interface chips.

The main parts of the chip, illustrated in figure 3.1, are : four input buffers, four routing table memories, the centralized buffer memory, four outgoing link multiplex controllers, and four output buffers. The bytes belonging to a packet that arrives through an incoming link are successively stored into that link's input buffer. The routing table memory associated with that link is accessed when the header (i.e. the VC ID) of that cell has arrived into the switch. This access provides the destination outgoing link (VC routing), and the new VC ID for this cell (VC translation).

Figure 3.1: Block diagram and capacity of the switch chip

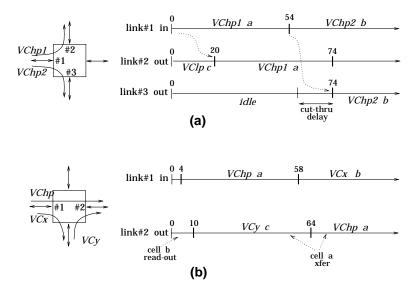

The packet will be stored into the buffer memory as soon as all of its bytes has been arrived and assembled into an entire ATM cell; all the bits of the cell are written in parallel into a row of the buffer memory. Under appropriate conditions (e.g. high priority VC, idle outgoing link), the cell will start being forwarded over its destination outgoing link, right away, without first being written into the buffer memory and then read into the output buffer. This is called "virtual cut-through" and is done through a special cross-bar switch circuit. The buffer memory is internally partitioned into five segments. Four of them have size 128 cells and each of their cells is dedicated to one of the 128 VCs of an outgoing link. The fifth segment is shared among the remaining 512 VCs of all the four links and has a size of 64 cells. A cell multiplexing circuit is associated with each outgoing link. It consists of a special "cycle counter", a finite state machine, and a scanning memory that keeps track of all the cells waiting to get forwarded over the particular

outgoing link. Under the control of these circuits, a VC is selected for service (i.e. transmission), according to the weighted round robin multiplexing policy and its priority class; the cell belonging to this VC is read out of the buffer memory, placed into the appropriate output buffer, from where it gets forwarded out of the switch, one byte at a time, over the corresponding outgoing link. Whenever a cell belonging to a particular VC is selected for transmission, a permit is send to the upstream chip, indicating that there is room in the local switch buffers for receiving one more cell of this VC. This back-pressure flow control policy ensures that the cells belonging to the VCs that have assigned dedicated buffers will never be lost due to contention for buffer space.

Conceptually, the switch architecture described here resembles more to the shared memory model described in chapter 1. However, the input buffering and virtual cut-through mechanisms it implements resemble to cross-bar space division switches, while the static way that part of the memory is partioned could be an argument for classifying it to the shared medium architectures. Additionally, this architecture does not have a restriction that most of the switch architectures described in chapter 1 have: It does not require the arrival of cells in the input lines to be time-synchronized. Furthermore, its unconventional buffer management, flow control, and cell multiplexing mechanisms distinguish it from the other approaches – these features constitute a set of efficient primitives for supporting quality of service in hardware, while most of the other approaches rely on end to end software protocols for this purpose.

#### **3.2** The Switch Chip Interface

The described architecture is independent of the pin level interface of its chip implementation. This implementation, however, is simplified by adopting a synchronous clocking discipline and a bit parallel interface between neighboring switches. In this way, no synchronizers, clock generators, or elastic buffers are needed, and the transfer delay is minimized. For the current version of the switch we have adopted this approach – a group of neighbor switch chips operate under a single external clock and communicate through bit-parallel links. We anticipate that such synchronous operation of several switches and interface chips on a board will not be impossible, provided that each chip will communicate only with close neighbors and the clock will be distributed through transmission lines with carefully equalized delays.

Each of the (bidirectional) links among switches consists of two sets of unidirectional wires (see figure 3.1). We prefer unidirectional pins, rather than tri-state ones, to avoid arbitration overhead and turn-around delays. In the current design, each unidirectional path consists of 5 wires; more wires per path can be used if a higher link throughput is desired. Thus the chips of the current configuration can be packaged in 48-pin packages (40 pins for the link interface, 4 power/ground pins, and 4 pins for clocking and miscellaneous functions like reset, test mode e.t.c). The 5 wires in each link direction carry 10 bits of information per clock cycle – 5 bits

during the positive half-cycle of the clock and 5 more bits during the negative half. In this way, the signaling rate on the clock pin does not have to be twice the desired signaling rate on the data pins. Assuming that each output pin cycles a 20 pF capacitance through a 5 Volt swing 50 million times per second (50 MHz clock, 100 Mb/s signaling rate), the maximum power consumption of each pin driver is 12.5 mW. Thus, driving the 4 links in our current design takes 0.25 Watts of power, which is comfortably low; an 8×8 switch chip with 9 wires per link direction (800 Mb/s data rate per link) would need 1 Watt to drive all of its links.

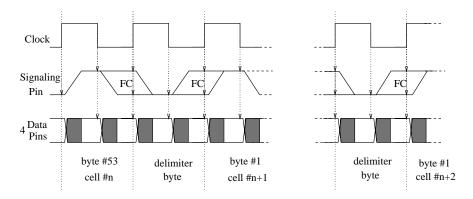

Figure 3.2: Synchronous operation and cell delineation on the chip interface

Chip to chip communication is obviously not error free; a noise spike in e.g. the clock signal may lead to a byte loss and consequently to a cell corruption. A single cell corruption is acceptable in our system; end to end retransmission protocols will be used to handle such cases. What is not acceptable however is the cell framing loss that may be caused by such a transient error. Therefore, a mechanism must be present in the switch to ensure that a single byte loss will not lead to overall synchronization loss. Our mechanism is illustrated in figure 3.2. The ten bits of information that are transferred in each link direction during each clock cycle contain one 8-bit data byte, one signaling bit, and one flow-control bit. The current chip design operates under a 50 MHz clock, giving a link throughput of 50 MBytes/s (400 Mbits/s) of data in each link direction. The signaling bit differentiates between a normal data byte in an ATM cell and the special celldelimiter control byte. A new 53-byte ATM cell can be transmitted through a link every 54 clock cycles -53 for data and 1 for the delimiter. When a link is idle, consecutive cell-delimiters are transmitted. By using this framing mechanism, an error during a cell transmission will not affect the framing of subsequent cells. Of course the cell that has been affected by the transient error, will arrive to its destination corrupted (or even to a wrong destination) – the current version of the chip does not implement any error recovery mechanism for this. However, we anticipate that such errors will rarely happen in a carefully designed switch PCB, and thus the overall error rate will be acceptably low.

It is evident that the synchronous operation of the chip interface is not part of the switch chip architecture; future extension of this architecture to higher link speeds will not be feasible to operate synchronously with their neighbors. In such cases one can adopt "messochronous" operation: neighboring switches operate under different clocks that are derived from a common system clock, and therefore have the same average frequency, while their clock phase difference is bounded. Such a messochronous operation is possible, regardless of how high the clock frequency is. A timing recovery circuit and an elastic FIFO can then be used to compensate for the difference in clock phases [Mess90].

## **3.3 Buffer and Routing Table Memories**

Perhaps the most critical decision in the design of a switch is the buffering scheme that will be used. Buffering may be done by independent buffers at each incoming link, centralized buffer(s), or independent buffers at each outgoing link. As already explained in chapter 1, in the case of centralized buffers and output buffers switching is done by time-division multiplexing on the buffer bus, while in the case of independent input buffers switching is performed by an  $N \times N$ space division switch. Our decision was to use buffer memory shared among all the links (figure 3.1, bottom). A shared buffer memory is certainly preferable over separate link-dedicated memories, if one can manage the high throughput requirements that sharing places upon it, and solve the buffer "hogging" problem [Fuji83]. The internal static partitioning of the shared buffer that we use solves the buffer "hogging" problem in a brute-force manner. The advantages of a shared buffer memory include better utilization of buffer space, simpler routing of the busses to and from the links (the shared memory bus replaces the space division switch), and less overhead owing to having less memories to manage [Toba90]. If we used input buffering, we would have to manage N distinct memory modules, and the implementation of the round robin multiplexing mechanism would be more complicated: the selection of a cell from an input buffer, would have to take into account the selections from the other input buffers. Output buffering does not suffer from the latter problem, but still has the overhead of managing N distinct memory modules, and does not relax the throughput requirements on each output buffer (see §§ 1.1.1, 1.1.2).

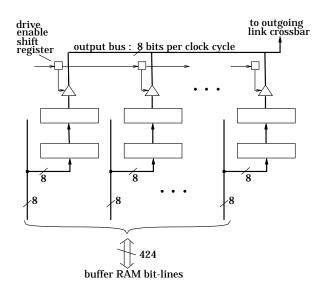

The problem of the shared buffer and output buffer architectures, that lead the majority of the designers to adopt input buffering scheme, is the high throughput requirements of the buffer RAM. However, the on-chip throughput of a modern RAM can be made very high by providing parallel access to all the bits in a row. A RAM of a few hundred Kbits is internally organized as several hundred rows of several hundred bits each; every single access to this array internally reads and/or writes (can write) an entire row. We can take advantage of this RAM organization and of the fact that our accesses only need to be at the granularity of entire ATM cells, to get very

high throughput out of a memory in which each row contains one ATM cell, i.e. 53 Bytes = 424 bits. For example, the memory of our current chip version, with its cycle time of 40 ns (§ 4.2), has a throughput of 25 Mega-accesses/s × 424 bits = 106 Gbits/s. A shared buffer RAM for an  $L \times L$  switch needs a throughput of 2L times the link throughput, to be able to receive L cells and transmit L other cells per link cell time. Table 3.1 lists the cycle time that a 424-bit wide RAM should have in order to be able to support the above throughput requirement, for various numbers L of links and various link speeds.

| Table 3.1: Shared buffer RAM requirements(RAM row size = 424 bits = 1 ATM cell) |            |              |  |  |

|---------------------------------------------------------------------------------|------------|--------------|--|--|

| number of                                                                       | link       | required RAM |  |  |

| links                                                                           | throughput | cycle time   |  |  |

| L                                                                               | Gbits/s    | ns           |  |  |

| 4                                                                               | 0.4        | 132          |  |  |

| 4                                                                               | 1.0        | 53           |  |  |

| 4                                                                               | 5.3        | 10           |  |  |

| 8                                                                               | 1.0        | 26           |  |  |

| 8                                                                               | 2.6        | 10           |  |  |

| 16                                                                              | 1.0        | 13           |  |  |

| 16                                                                              | 4.0        | 3.3          |  |  |

The first line of this table reflects our current design; a cycle time of 130ns can be trivially achieved in the current CMOS technology (our cycle time is 40 ns). Cycle times of a few tens of nanoseconds are also common today, while the shorter cycle times, in the range of a few nanoseconds, are achievable in BiCMOS or ECL technology. For example, a 4 Mbit SRAM chip with a 7 ns access time has already been demonstrated [OSKY91]; if the technology and the capacity of that chip were available to us, the memories in our chip could be three to four times larger as well as significantly faster, thus yielding switch chips with 12 to 16 links of 1 or more Gbits/s each, and with the same number of VCs *per link*. It follows that the shared buffer architecture will not run out of steam for some more years to come.

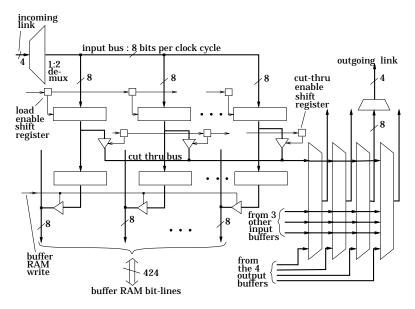

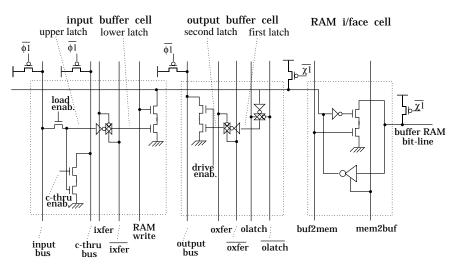

In order to access the shared buffer RAM at the ATM cell granularity, the data from the incoming links are first "shifted into" special *input buffers*, until an entire cell has been assembled, and then all the bits of the latter are written *in parallel* into the buffer RAM. Similarly, to feed the outgoing links, entire cells are read from the buffer RAM into special *output buffers* and then shifted out to the links. There are 4 double input buffers and 4 double output buffers in a 4×4 switch chip. Double-buffering is required, on the input side, to ensure that no incoming data are lost from the time a cell gets assembled to the time the (shared) buffer RAM becomes available to accept that cell; on the output side, double-buffering ensures that cells can be sent out "back-to-back". An important part of the input buffers are the *cut-through* busses, which are required in order to immediately forward a cell if its outgoing link becomes available while the

cell gets assembled in its input buffer [KeKl79]. The input and output buffers and the implementation of the cut-through mechanism are further described in § 4.3.

As explained in § 3.1, the VC translation and routing in our switch are implemented by accessing the routing table memories (upper left of figure 3.1). Each routing table memory in the current version of the switch chip has a size of 256 words times 11 bits per word – 8 bits for storing the new VC ID, 2 bits for specifying the destination outgoing link and 1 bit to signify if the VC is currently open. Normally, the routing memories would also contain the service class (priority) of the VCs, their service frequency weights, and their flow-control states (stopped or not), but we maintain all this information in the output-multiplexing memory to be described in the next section.

Effectively our architecture supports 1024 VCs over all its links, so a straightforward implementation would be to provide a 1024-word routing table memory for all the input links. However, providing separate routing table memories for each incoming link has certain advantages. First, a shared routing table memory would introduce additional delay in the critical (for the round trip delay) path of VC lookup due to the access conflicts of the cells from the four links. A solution be to make the shared routing table quad-ported, but this would overly increase its size (and delay). The second advantage of partitioning the routing table is that less bits can be used for identifying a given number of VCs. This economizes about 16 % of total routing table area – the 13,312 bits of storage are reduced to 11264 and four 8-to-256 decoders are used instead of one 10-to-1024. Also, the size of the flow control token is decreased so that more tokens can be sent to an upstream chip during a cell transmission time (6 rather than 4.9 on the average). An argument in favor of the shared routing table memory might be that it allows more than 256 VCs to be routed in one (input or output link) and hence it supports better the "hot-spot" [PfNo85] patterns of traffic. However, in the envisioned network architecture, we anticipate that traffic will be uniformly distributed in most cases. Furthermore, if the network designer expects some kind of "hot-spot" traffic in a particular network, he can appropriately configure the topology of the composite switch for supporting the expected pattern of traffic. It follows that the partitioning of the routing table is a better choice for the purposes of this switch architecture.

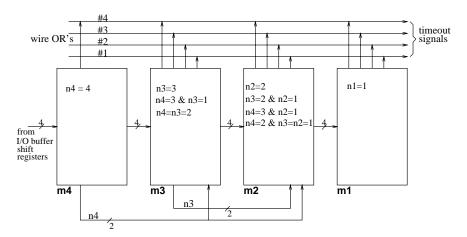

As soon as the outgoing link and the new VC ID of an incoming cell have been determined, the responsibility for keeping track of the cell is passed to the control circuit of its outgoing link. The main part of each such controller is a memory that records all administrative information related to the VCs and the cells destined to go on the corresponding outgoing link. A finite-state machine (FSM) continuously scans that memory, trying to decide which cell should be forwarded next – we refer to that memory as the *scanning-memory*. During the design of our chip we considered several alternatives for the organization of the buffer and the scanning memories, which we review now.

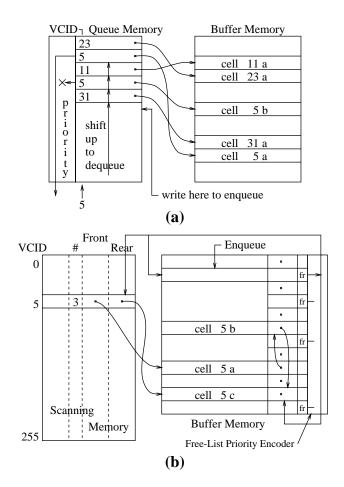

First we looked at how we might implement in hardware the management of traditional queues of cells (see e.g. [Fuji83] and [FrTa88]), in a buffer memory that is shared among the VCs, as a measure against which to compare our own eventual scheme. Since we would want to implement round-robin scheduling, rather than FCFS, we would need a separate queue of cells for each VC. Figure 3.3 shows two alternatives, the second of which seems better. In (**a**), a special queue-memory, with the same number of words as the buffer memory, is used to hold pairs of VC ID's and buffer-addresses for the cells that are currently buffered, *in the order* in which these cells have arrived; effectively, this memory maintains all the queues for all the VCs. To support the dequeueing of the oldest cell of a given VC – say VC#5 – this memory has to be content-addressable (CAM) and the corresponding priority encoder has to select the top-most matching entry. This memory also has to be organized as partial-shift-up registers, so that an entry is dequeued by shifting all entries below it up by one position. These two requirements, CAM and shift, make it an expensive memory. In addition to this queue memory we would still need the scanning memory, to hold the various administrative information for each open VC; thus, solution (a) is not very attractive.

The organization shown in part (b) of figure 3.3 is better. It augments the buffer memory with a pointer field in every word (and with an additional address-decoder for that field, as we'll see); this pointer is used to link together all the cells in the queue of a particular VC. The scanning-memory, which contains one entry for every VC, is also augmented with two pointer fields per entry, used as front and rear queue pointers. No third memory, analogous to the queue memory in (a), is needed in this scheme. Dequeueing a cell is relatively easy: using the front pointer, we read a single word from the buffer RAM; this provides us both with the cell and with the new value for the front pointer. To be able to enqueue a cell in a single buffer-RAM cycle time, we need a pointer to a free word and two address decoders. Using the free word pointer and the first address decoder, the cell is written into the data part of the buffer RAM. Using the rear pointer and the second address decoder, the value of the (ex-)free pointer is written into the pointer part of the buffer RAM. The free-word list of the buffer memory can be implemented as another linked list, using the pointer field of that RAM. During cell dequeueing, this necessitates a read-modify-write access to the pointer field of the buffer RAM, so that the dequeued word is simultaneously enqueued into the free list; during cell enqueueing, it necessitates a pointer-read from the (ex-)free word, simultaneously with the pointer-write into the (ex-)rear word. Alternatively, the free list can be implemented using a flag bit in each buffer-RAM word and a priority encoder that selects one of the true bits. In addition, a two stage pipeline increases the maximum rate of cell enqueueing. During the first stage, the free list priority encoder operates, while during the second stage we equeue the cell; during cell dequeueing, the free flag bit is written concurrently with data read, thus eliminating the need for the read-modify-write access. Note that

Figure 3.3: Traditional cell queues in a shared buffer organization

this implementation of the free list would also have to be used in solution (a). The scanning memory in (b) also contains a count of the number of buffered cells per VC, in order for flow-control decisions to be made.

A third alternative is to statically partition the buffer RAM space between VCs, allowing each cell belonging to a particular VC to occupy some predetermined buffer RAM rows. The number of rows dedicated to each VC must be equal to the round-trip delay of tokens and cells *counted in cell-times*. In our chip design, where this delay is 2 cell times on the average (§ 3.8), dedicating two rows of the buffer RAM to each VC would be a reasonable choice – i.e. store cells belonging to VC *i* either to row  $2\times i$  or to row  $2\times i+1$ . The advantages of this scheme are obvious. First, it completely eliminates the VC and free list management overheads. Second, it reduces the size of the scanning memory by eliminating the need of storing front and rear pointers for each VC queue. For example scheme (b) above would require  $18\times256$  bits of memory for storing the *front* and *rear* pointers, in a chip with a total of 256 supported VCs and 512 cells of buffer memory. Instead, the new scheme requires only  $3 \times 256$  bits of storage, since three bits per VC are enough for designating how many cells are stored in the two cells buffer space for the VC, and which of the two cells is the "head" of this VCs list.

The organization of the buffer memory described above, statically allocates all of the buffer memory space, which as discussed in chapter 2 is not the best buffer allocation scheme for all the kinds of expected traffic. On the other hand, a shared buffer memory has the advantage that less total buffer space is required, but also the disadvantage that overload conditions yield loss of cells and/or underutilization of the throughput. Our switch chip manages part of its buffer memory as shared, and part of it as dedicated, while it also radically simplifies queue management. We will present and briefly justify this organization here. A deeper analysis of it appears in [KaSC91]. Virtual circuits 0 through 127 on each outgoing link are intended for traffic that is allowed to – or even expected to – try to overload the network, and thus they each have a buffer dedicated to itself. Virtual circuits 128 through 255, on the other hand, can only be used by traffic for which the management of the network can guarantee that it will never exceed a certain portion of the network capacity, and thus all these VCs of *all* outgoing links share a common buffer pool of 64 cells.

An important decision, that significantly simplifies the hardware of our switch chip, is to allow a *maximum of one buffered cell per VC*. For the VCs that have dedicated buffer space, this significantly reduces the required buffer RAM size. For the VCs that share the 64-cell buffer pool, this greatly simplifies (actually eliminates) queue management. Also, for all VCs, this decision simplifies flow-control. The negative effect of this decision, which however is negligible, is the following: as discussed in § 3.8, the round-trip delay of a flow-control command to the next upstream switch chip and of its effect on the downstream traffic is about *two cell times*, on the average. Thus, limiting the buffer space per VC to one cell, limits the peak instantaneous throughput *per VC* to one half the link throughput – not a very important restriction, since more than one system VCs can be used if the network manager wishes to allow one end-user VC to momentarily use all of the link throughput.

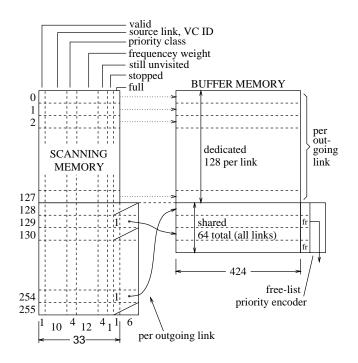

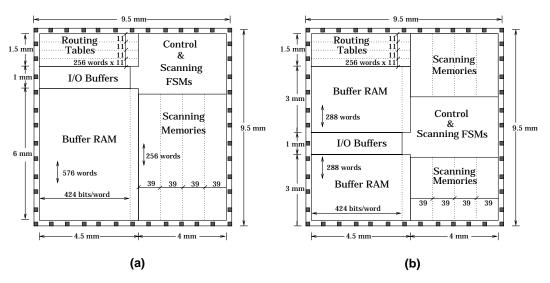

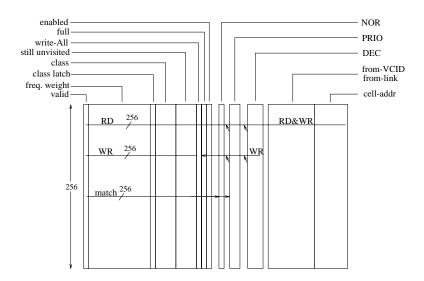

Figure 3.4 illustrates our buffer and scanning memory organization. The entire buffer RAM has a capacity of  $576 = 4 \times 128 + 64$  cells. Each of the 4 outgoing links has 128 of these cells dedicated, one-to-one, to its 128 first VCs. Thus, the first 128 entries of each scanning-memory do not need a buffer pointer. The other 128 entries of the scanning memories need a 6-bit pointer to indicate the position of their buffered cell, if it exists, in the 64-cell shared buffer pool. The 64-word shared part of the buffer RAM has one additional bit per word, used as an empty/full flag, and a priority encoder, to implement the "free list". Relative to the scheme of figure 3.3(b), this solution has 35 % less bits in the scanning memory, and a few less bits per word and one less decoder in the buffer memory. Relative to the third alternative (two buffered cells per VC) this scheme quadruples the total number of VCs supported by the switch chip at the expense of a 10

Figure 3.4: Buffer memory and scanning memory organization

% increase on the silicon area. The scanning memory has the following fields:

Valid (1 bit), indicating whether this VC is currently open;

- Source link and VC ID (10 bits), needed in order to know where to send flow-control commands to;

- *Priority* class of this VC (4 bits, in decoded format), needed in choosing the next VC to serve see § 3.6;

Weight of service frequency (12 bits) – see § 3.5;

Still-unvisited flag (4 bits) - see §§ 3.5, 3.6;

Stopped flag (1 bit), indicating whether the flow of this VC is currently stopped because the next downstream switch chip has a full buffer;

Full flag (1 bit), indicating whether this VC currently has a buffered cell.

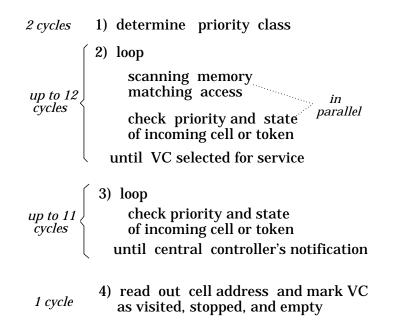

A finite state machine uses the above fields of the scanning memory (the memory is organized as content addressable) to determine which VC to serve next, according to the prioritized weighted round-robin scheduling. The implementation of this scheduling described in detail in next section, while FSM that searches the scanning memory is described in § 3.6.

## 3.5 Weighted Round Robin Multiplexing in Hardware

This section<sup>†</sup> presents the weighted round-robin scheduling algorithm and discusses the hardware requirements of its implementation. The idea of round-robin scheduling, in general, is that a server process circularly and repeatedly "visits" a number of clients and performs one job for each of them that has such a need at the time of the visit. In the case of multiplexing ATM cells for an outgoing link of the switch chip, visiting the VCs in a round-robin fashion and forwarding one cell from each ready VC upon each visit is in principle fairer than FIFO (FCFS) multiplexing, as it was discussed in chapter 2. However, to be really fair, this mechanism should not treat all VCs as exactly equal, but rather as equal within a given weight factor: when the throughput requirements of two VCs cannot be met, the available throughput should be distributed to them in proportion to their weight factors  $W_1$  and  $W_2$ . This can be achieved with the *weighted round-robin* algorithm illustrated below.

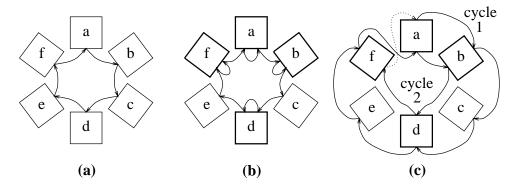

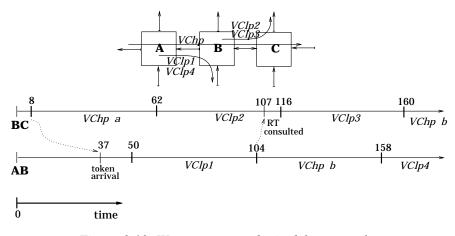

Figure 3.5: Round-robin (a) and weighted round-robin (b), (c) visits

Figure 3.5(a) illustrates the classic round-robin algorithm: during every cycle of the server process, all clients are visited exactly once each. Part (b) of this figure is a first approach to the weighted round-robin scheduling. Clients a, b, d, and f receive twice more frequent service than clients c and e, since the former are visited twice while the latter only once in every 10 visits. In part (c) of the figure, the frequencies of visits are maintained the same, but the visits to the "frequent" clients are spread more evenly in time. For example, two successive visits to a are separated by either zero or eight visits to other clients in schedule (b), while in schedule (c) they are separated by either three or five other visits. We will adopt the scheduling style of figure 4.1(c): the successive visiting cycles will be labeled  $1, 2, \dots, N-1, N, 1, 2, \dots$  and each VC will have a certain frequency weight that entitles it to receiving one unit of service during every cycle whose label belongs to a specified subset of the numbers  $1, 2, \dots, N$ .

<sup>†</sup> written by M. Katevenis, as § 4 of [KaSC91], and reproduced here.

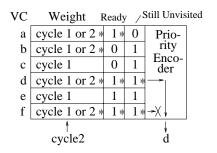

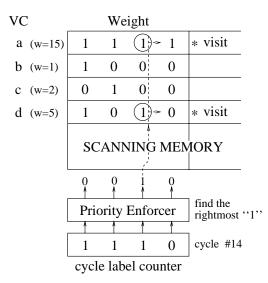

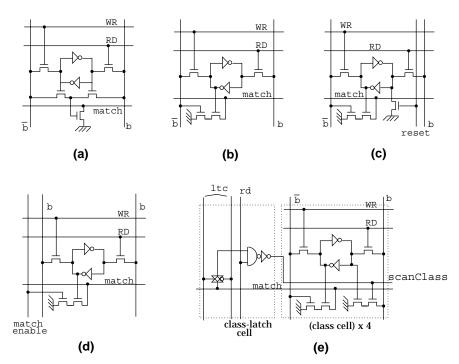

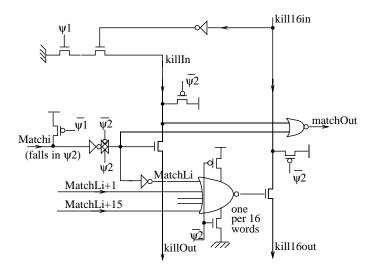

Figure 3.6: The VC scanning memory

Figure 3.6 shows the main idea of how we implement the weighted round-robin visits in hardware. All the relevant weight and state information of all the VCs is kept in a memory, the scanning memory, which is organized similarly to a content-addressable memory (CAM). The "ready" bit of each word represents the flow-control and cell availability information: it is true whenever the buffer RAM contains at least one cell of the corresponding VC, and that VC is not stopped due to back-pressure (flow-control) from the destination switch. The "still unvisited" bits are all set to 1 before each visiting (scanning) cycle begins; during the cycle, after a certain VC is visited, its *still-unvisited* bit is cleared. In the situation illustrated in figure 4.2, we are in the process of performing a scan cycle labeled "2"; only the VCs a, b, d, and f are entitled to a visit during this cycle, as illustrated by the asterisk that appears in their weight entry. Out of these four VCs, only a, d, and f remain candidate for a visit after the ready bit is taken into consideration (see the three asterisks in that column). Further on, VC a was just visited during the last access to the scanning memory, thus leaving only d and f as the eventual candidates for the rest of this scanning cycle. The priority encoder selects d as the VC to be served now: an ATM cell of d will be transmitted, and the *still-unvisited* bit of d will be cleared. During the next query to the scanning memory, the *still-unvisited* flags will only let VC f get through to the priority encoder, and thus it will be served in its turn. The query after that will yield no result, thus signaling that a new scanning cycle must be initiated by setting all *still-unvisited* flags and advancing the cycle label to "1".

The next issue to resolve is how the weight entry of each VC should specify the exact cycle labels during which that VC is entitled to a visit. If the scanning cycles are labeled 1 through N, a VC that is visited during w of these N cycles receives a throughput (service) share of relative size w/N. The minimum service rate is obviously 1/N and the maximum is N/N. Which ones of the cycles  $1, 2, \dots, N$  should a w/N-rate VC get visited in? One solution might be to visit it during the cycles  $1, 2, \dots, w$ , but that would result in an uneven spreading of the visits on the time axis. A much better spreading would result by serving this VC during the cycles  $N/w, 2N/w, \dots, wN/w = N$  (or anyway some integer approximations to these values). However, computing these cycle labels in hardware or storing their precomputed values would be unrealisticly expensive. We use a different choice of w labels out of N, that is very easy to generate in hardware, and whose spreading in the time axis does not differ much from the above even spreading. More precisely, in the above even spreading, two successive visits to the VC occur approximately N/w cycles apart. In our method, they occur a maximum of  $(N+1)/w_1$  and a minimum of  $(N+1)/2w_1$  cycles apart, where  $w_1$  is the largest power of 2 that is less than or equal to w (N must be a power of 2 minus one) (when w is a power of 2, the maximum is (N+1)/w and the minimum is ((N+1)/w)-1).

Figure 3.7: Cycle identification and binary frequency components

Figure 3.7 will help us explain our method of choosing *w* labels "relatively evenly" among the *N* cycle labels, where N is a power of 2 minus one  $(N=2^n-1)$ . Our method is based on writing the cycle labels, 1 through *N*, as binary numbers and identifying the rightmost (least significant) "1" digit in this notation. There are (N+1)/2 labels in which that rightmost-1 is in the least significant bit-position (position 0), (N+1)/4 labels where it is in position 1, (N+1)/8labels where it is in position 2, etc. These  $\log_2(N+1)$  sets of labels contain decreasing powers of 2 of labels each, they are *distinct* (their intersection is null), and they are spread "quite evenly" in the time axis (vertically in figure 3.7). We choose *w* labels out of these *N* as follows: write *w* as a binary number, that is as a sum of powers of two; choose all the labels from all the above sets whose cardinalities are those same powers of two. For example, in figure 3.7, if *w*=5, i.e. if we wish to serve a particular VC at a relative rate of 5/15 = (4/15)+(1/15), we will visit that VC once

during every scanning cycle whose label has its rightmost-1 at bit positions 1 or 3.

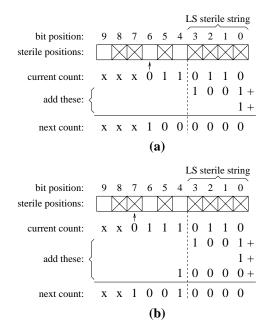

*Figure 3.8: Cycle matching* – visit those VCs whose weights, stored in *reverse* bit order, have a "1" at the position of the rightmost "1" of the cycle counter.

Figure 3.8 shows the details of the cycle-matching part of the scanning memory (left part of figure 3.6). A counter contains the current cycle label. A priority enforcer drives a bus through the weight part of the scanning memory with a single "1" at the position of the rightmost "1" of the cycle counter. The scanning memory contains the weight of every VC, in binary notation, stored in *reverse* bit order. This reversal occurs because the leftmost positions are the ones where the priority enforcer sends a "1" less frequently, and thus they are the least-significant weight positions. Those VCs whose weight has a "1" at the position where the priority enforcer sends as candidates to be visited during the current scanning cycle.

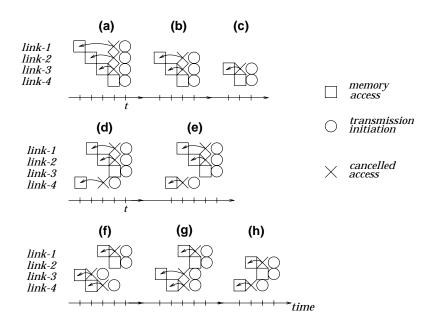

There is one more practical problem to be solved in the above hardware set-up; it has to do with how fast we can search for the next VC to serve (next VC to forward a cell from). In order not to waste any link throughput, the search for the next VC must be performed during the time when the current cell is being transmitted over the outgoing link. In our current design, this time is 53 Bytes  $\times 20$  ns = 1.06  $\mu$ s, i.e. it is enough for about two dozens of accesses to the scanning memory. This is a comfortable limit if lots of VCs are ready for transmission, but things are different if only the VCs with the smallest weights are ready. Consider, in the example of figure 3.8, the case where only VC *b* is ready. Doing one access to the scanning-memory we discover that there is no VC to be served during the current cycle #14, since VCs *a* and *d* are not ready. Consequently, the cycle counter is advanced to cycle #15 and a new access is performed to the scanning this cycle and that VC is not ready. It will take seven more incrementations of the cycle counter,

and seven more sterile accesses to the scanning-memory, before the counter reaches cycle #8 when VC b is entitled to a visit and thus the next cell to be transmitted is determined. This is clearly impractical when the cycle counter has many bits (N is large). We can see that during the above multiple sterile accesses, similar searches are uselessly repeated. During all of cycles 15, 1, 3, 5, and 7, the priority enforcer of figure 3.8 asserts its rightmost output wire. Since the search of cycle #15 yields no ready VC, it is useless to perform the exact same search for cycles 1, 3, 5, and 7. Similarly, the searches of cycles 2 and 6 are useless, given that the similar search of cycle #14 found no ready VC with a binary component of 4/15 in its weight (see figure 3.7). What is needed then, is a cycle counter that can *"jump"* over those counts whose rightmost-1 is at bit-positions already determined to be sterile.

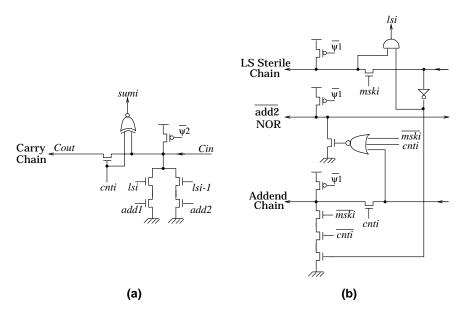

Figure 3.9: Incrementing the cycle counter so as to jump over sterile bit positions

Figure 3.9 shows the idea of how to design such a counter. In this figure, the boxes at the top that are crossed out represent bit-positions known to be sterile; positions 0, 2, 3, 5, 7, and 8 were known to be sterile from beforehand, while in the current cycle, whose rightmost-1 is at position 1, we just determined that this position 1 is also sterile. Jumping over the sterile counts (and just them) means to add to the current count the *smallest* number that will generate a next count with a rightmost-1 in a non-sterile bit-position. Of key importance is the *LS sterile string* – the rightmost string of *consecutive* sterile positions – in this case positions 0 through 3. Adding to the current count anything less than or equal to 1001 - the 1's-complement of the current-count bits that fall inside the LS sterile string – is obviously not enough, since any such addend would leave a rightmost-1 in the LS sterile area after the addition; thus, we have to add at