## Operating System Mechanisms for Remote Resource Utilization in ARM Microservers

John Velegrakis

Thesis submitted in partial fulfillment of the requirements for the

Master of Science degree in Computer Science

University of Crete School of Sciences and Engineering Computer Science Department Voutes Campus, Heraklion, GR-70013 Greece

Thesis Advisor: Prof. Manolis Katevenis

This work was performed in the Computer Architecture and VLSI Systems (CARV) Laboratory of the Institute of Computer Science (ICS) of the Foundation for Research and Technology – Hellas (FORTH), and was financially supported by a FORTH-ICS scholarship, including funding by the European Union 7th Framework Programme under the EuroServer (FP7-ICT-610456) project.

UNIVERSITY OF CRETE COMPUTER SCIENCE DEPARTMENT

#### Operating System Mechanisms for Remote Resource Utilization in ARM Microservers

Thesis submitted by John Velegrakis in partial fulfillment of the requirements for the Masters' of Science degree in Computer Science

THESIS APPROVAL

Author:

John Velegrakis

Committee approvals:

Manolis GH Katevenis Professor, Thesis Supervisor

Angelos Bilas Professor, Committee Member

Dionisios N. Pnevmatikatos Professor, Committee Member

Departmental approval:

Antonios Argyros Professor, Director of Graduate Studies

Heraklion, March 2015

#### Abstract

Recent efforts towards performance and power optimization in large-scale Data Centers have brought the use of Microservers in the forefront. Compared to traditional architectures, Microservers consist of smaller, less power-hungry Compute Units (CUs) compared to traditional architectures. The key concept is that by integrating such smaller CUs in high numbers, the resulting many-core system can achieve high multi-threaded performance, while maintaining a low power profile. In such an environment, expensive resources must be shared among CUs, since it is costly and impractical to dedicate one to each CU. However, the management of these resources requires to implement sharing mechanisms in the Operating System (OS) and the software stack.

In this work, we investigated and implemented OS and user space software mechanisms that are necessary for the deployment of ARM-based CUs in such large-scale systems. We address the sharing of remote resources by fully exploiting the underlying hardware features, such as Remote Direct Memory Access (DMA) and Remote Load/Store. In particular, we have implemented software mechanisms to (1) enable access to remote memory and (2) allow usage of a shared virtualized 10 Gbps Network Interface Card (NIC) by several CUs simultaneously.

Remote memory access is implemented in three different ways: (1) As an extension of the local DRAM of the CUs, (2) As a remote Swap Device, and (3) as an I/O character device accessed directly from user space. We demonstrate that remote memory can be used effectively without performance penalty in a system running a full OS.

The sharing of a virtualized 10Gbps NIC is achieved by a kernel network driver, that we have implemented, which enables utilization of the customized hardware as a standard Ethernet Device. This allows legacy applications that use Berkeley Sockets to run unmodified. The network driver makes use of scatter-gather DMA for fast zero-copy packet transmission and reception and operates in Full-Duplex mode by using two independent DMA channels. Additionally, it supports Interrupt Coalescing and management of the MAC and PHY hardware blocks using the Management Data Input/Output (MDIO) interface.

In conclusion, this work shows that we can indeed utilize a system built upon ARM-based CUs that were not originally designed to operate in such an environment, by the sharing of remote and shared resources by the Linux OS and its user space environment. We expect this work to become even more relevant with upcoming 64-bit ARM-based platforms, targeting large-scale servers for Data Centers.

#### Περίληψη

Οι πρόσφατες προσπάθειες για βελτιστοποίηση της απόδοσης αλλά και της κατανάλωσης ισχύος των μεγάλης κλίμακας Δατα Έντερς έφερε τους λεγόμενους Μιςροσερερς στο προσκήνιο, οι οποίοι αποτελούνται από μικρότερης κατανάλωσης Υπολογιστικές Μονάδες (ΥΜ) συγκρινόμενοι με τις παραδοσιακές αρχιτεκτονικές. Η κεντρική ιδέα είναι ότι χρησιμοποιώντας μεγάλο αριθμό από τέτοιες ΥΜ μπορούμε να κατασκευάσουμε μία πολυπύρηνη μηχανή που θα έχει υψηλή απόδοση στις πολυνηματικές εφαρμογές και παράλληλα θα έχει χαμηλή ε νεργειακή κατανάλωση. Σε τέτοιες μηχανές, οι ακριβοί πόροι αναγκαστικά διαμοιράζονται μεταξύ των ΥΜ, καθώς δεν γίνεται να αποδοθούν πόροι για κάθε ΥΜ ξεχωριστά. Ωστόσο, η διαμοίραση των πόρων αυτών απαιτεί την υλοποίηση κατάλληλων μηχανισμών στο Λειτουργικό Σύστημα (ΛΣ) και γενικότερα στο επίπεδο του λογισμικού.

Σε αυτήν την εργασία, ερευνήσαμε και υλοποιήσαμε μηχανισμούς στο ΛΣ και στο επίπεδο διεργασιών, οι οποίοι είναι απαραίτητοι για την χρησιμοποίηση ΥΜ βασισμένων σε αρχιτεκτονικές ARM σε μεγάλης κλίμακας συστήματα. Υλοποιήσαμε την διαμοίραση πόρων δύο ειδών, χρησιμοποιώντας τους διαθέσιμους μηχανισμούς του υλικού, όπως η Remote Load/Store και Remote Load/Store. Συγκεκριμένα, υλοποιήσαμε μηχανισμούς για την απομακρυσμένη προσπέλαση μνήμης και την χρησιμοποίηση μιας κοινής και virtualized 10 Gbps διεπαφής δικτύου η οποία μπορεί να χρησιμοποιείται από πολλές ΨΜ ταυτόχρονα.

Η χρησιμοποίηση της απομακρυσμένη μνήμης υλοποιήθηκε με τους εξής ακόλουθους τρόπους: (1) Σαν επέκταση της τοπικής DRAM μίας ΥΜ, (2) Σαν απομακρυσμένη συσκευή για Swap, και (3) Σαν απομακρυσμένη συσκευή χαρακτήρων που χρησιμοποιείται απευθείας από τις διεργασίες. Δείχνουμε ότι η χρήση της απομακρυσμένης μνήμης σε ένα σύστημα με ΛΣ δεν επιφέρει μείωση της απόδοσης.

Η από κοινού χρήση της διεπαφής δικτύου 10 Gbps επιτυγχάνεται με ένα οδηγό στο ΛΣ, τον οποίο υλοποιήσαμε και ο οποίος επιτρέπει στο ΛΣ να βλέπει την διεπαφή αυτή σαν κλασσική διεπαφή Ethernet. Αυτό είναι απαραίτητο για να μπορούν να τρέξουν διεργασίες που χρησιμοποιούν τα Berkeley Sockets, χωρίς να χρειάζεται να τροποποιηθούν. Ο οδηγός χρησιμοποιεί Scatter/Gather DMA για γρήγορη και zerocopy μετάδοση και παραλαβή πακέτων και λειτουργεί σε Full-Duplex χρησιμοποιώντας δύο ξεχωριστά κανάλια της DMA μηχανής. Επιπλέον, υποστηρίζει μηχανισμούς Interrupt Coalescing και μπορεί να διαχειριστεί τα MAC και PHY μέρη του υλικού μέσω του πρωτοκόλλου Management Data Input/Output (MDIO).

Η εργασία αυτή δείχνει ότι πράγματι μπορούμε να φτιάξουμε ένα σύστημα βασισμένο σε ΥΜ αρχιτεκτονικής ARM, οι οποίες δεν είναι σχεδιασμένες να λειτουργούν σε ένα τέτοιο σύστημα. Πιστεύουμε ότι αυτή η εργασία θα γίνει ακόμα πιο σημαντική στο μέλλον, καθώς νέες 64-μπιτες πλατφόρμες ARM εμφανίζονται, οι οποίες στοχεύουν να χρησιμοποιηθούν σε μεγάλης κλίμακας Data Centers.

#### Acknowledgements

This work was performed in the Computer Architecture and VLSI Systems (CARV) Laboratory of the Institute of Computer Science (ICS) of the Foundation for Research and Technology – Hellas (FORTH), and was financially supported by a FORTH-ICS scholarship, including funding by the European Union 7th Framework Programme under the EuroServer (FP7-ICT-610456) project.

I would like to thank the Institute of Computer Science at FORTH for support my research, by providing access to equipment and financial support.

Furthermore, I would also like to thank the Computer Architecture and VLSI Laboratory hardware team and my advisor Prof. Manolis Katevainis. Special thanks to Dr. Manolis Marazakis and Mr. Giorgos Kalokairinos for their support in my work.

John Velegrakis, Staff Sergeant, Hellenic Army Reserve

# Contents

| 1        | $\mathbf{Intr}$ | oduction                                               | 3         |  |  |  |  |

|----------|-----------------|--------------------------------------------------------|-----------|--|--|--|--|

|          | 1.1             | Contributions                                          | 5         |  |  |  |  |

| <b>2</b> | Related Work    |                                                        |           |  |  |  |  |

|          | 2.1             | Remote Memory                                          | 9         |  |  |  |  |

|          | 2.2             | Shared Network Interface                               | 10        |  |  |  |  |

| 3        | Disc            | crete Prototype                                        | 13        |  |  |  |  |

|          | 3.1             | Discrete Prototype Generation 1                        | 13        |  |  |  |  |

|          |                 | 3.1.1 Physical Address Translation                     | 17        |  |  |  |  |

|          | 3.2             | Discrete Prototype Generation 2                        | 18        |  |  |  |  |

|          | 3.3             | Hardware Virtualization                                | 20        |  |  |  |  |

| 4        | Ren             | note Memory                                            | <b>23</b> |  |  |  |  |

|          | 4.1             | Page Borrowing & Caching Policy                        | 23        |  |  |  |  |

|          | 4.2             | Remote Memory and the Operating System                 | 25        |  |  |  |  |

|          | 4.3             | Remote Memory as Main Memory Extension                 | 27        |  |  |  |  |

|          |                 | 4.3.1 Defining Remote Memory                           | 28        |  |  |  |  |

|          |                 | 4.3.2 Accessing Remote Memory from User Space          | 30        |  |  |  |  |

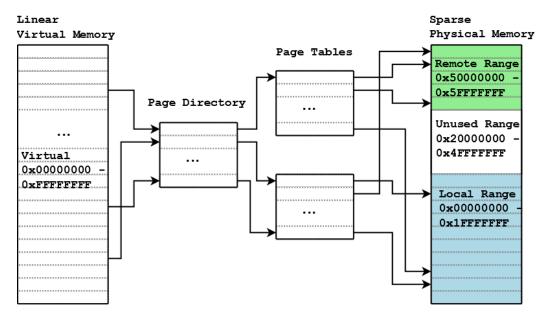

|          |                 | 4.3.3 Sparse Memory Model                              | 31        |  |  |  |  |

|          | 4.4             | Remote Memory as Swap Device                           | 32        |  |  |  |  |

|          |                 | 4.4.1 Ramdisk Driver                                   | 33        |  |  |  |  |

|          |                 | 4.4.2 Driver with DMA                                  | 35        |  |  |  |  |

|          | 4.5             | User Space and Swap                                    | 35        |  |  |  |  |

|          | 4.6             | Explicit Access of Remote Memory                       | 35        |  |  |  |  |

|          | 4.7             | Explicit Remote DMA Operations                         | 36        |  |  |  |  |

|          | 4.8             | Remote Memory as I/O Device                            | 37        |  |  |  |  |

|          | 4.9             | Operating System with Non-Uniform Memory Access (NUMA) | 37        |  |  |  |  |

|          | 4.10            | Deadlock Scenario                                      | 39        |  |  |  |  |

| 5        | Ren             | note Memory Evaluation                                 | 41        |  |  |  |  |

|          | 5.1             | Bare Metal Evaluation                                  | 41        |  |  |  |  |

|          |                 | 5.1.1 Latency                                          | 41        |  |  |  |  |

|          |                 | 5.1.2 Data Transfer Throughput                         | 45        |  |  |  |  |

|      | 5.1.3                                                   | DMA Throughput                                                                                                                                                                                                                                                                                                                                                                                    | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2  | Linux                                                   | Microbenchmarks                                                                                                                                                                                                                                                                                                                                                                                   | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 5.2.1                                                   | Latency                                                                                                                                                                                                                                                                                                                                                                                           | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 5.2.2                                                   | Data Transfer Throughput                                                                                                                                                                                                                                                                                                                                                                          | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 5.2.3                                                   | Local Memory Throughput                                                                                                                                                                                                                                                                                                                                                                           | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 5.2.4                                                   | DMA Throughput                                                                                                                                                                                                                                                                                                                                                                                    | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 5.2.5                                                   | DMA Throughput vs. Data Size                                                                                                                                                                                                                                                                                                                                                                      | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 5.2.6                                                   | Remote Swap I/O Throughput $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                            | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 5.2.7                                                   | Remote Swap I/O Throughput with DMA $\ldots$                                                                                                                                                                                                                                                                                                                                                      | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 5.2.8                                                   | Swap Devices Comparison                                                                                                                                                                                                                                                                                                                                                                           | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Sha  | red Ne                                                  | etwork Interface                                                                                                                                                                                                                                                                                                                                                                                  | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6.1  | Netwo                                                   | rk Driver                                                                                                                                                                                                                                                                                                                                                                                         | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 6.1.1                                                   | Simple Operation                                                                                                                                                                                                                                                                                                                                                                                  | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 6.1.2                                                   | Scatter-Gather & Ring Descriptors                                                                                                                                                                                                                                                                                                                                                                 | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 6.1.3                                                   | Set Up                                                                                                                                                                                                                                                                                                                                                                                            | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 6.1.4                                                   | Transmitting a Frame                                                                                                                                                                                                                                                                                                                                                                              | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 6.1.5                                                   |                                                                                                                                                                                                                                                                                                                                                                                                   | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 6.1.6                                                   |                                                                                                                                                                                                                                                                                                                                                                                                   | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 6.1.7                                                   | Interrupt Coalesce                                                                                                                                                                                                                                                                                                                                                                                | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 6.1.8                                                   | ethtool Interface                                                                                                                                                                                                                                                                                                                                                                                 | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 6.1.9                                                   | MAC Configuration                                                                                                                                                                                                                                                                                                                                                                                 | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 6.1.10                                                  | Management Data Input/Output (MDIO) & XGMII                                                                                                                                                                                                                                                                                                                                                       | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 6.1.11                                                  | Network Statistics                                                                                                                                                                                                                                                                                                                                                                                | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 6.1.12                                                  | Device Tree                                                                                                                                                                                                                                                                                                                                                                                       | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 6.1.13                                                  | Zero Copy Anecdotes                                                                                                                                                                                                                                                                                                                                                                               | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6.2  |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                   | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 6.2.1                                                   | Bare-Metal Throughput                                                                                                                                                                                                                                                                                                                                                                             | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 6.2.2                                                   | TCP Throughput                                                                                                                                                                                                                                                                                                                                                                                    | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 6.2.3                                                   | Raw Ethernet Throughput                                                                                                                                                                                                                                                                                                                                                                           | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Con  | clusio                                                  | ns and Future Work                                                                                                                                                                                                                                                                                                                                                                                | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.1  | Conch                                                   | usions                                                                                                                                                                                                                                                                                                                                                                                            | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.2  | Future                                                  | e Work                                                                                                                                                                                                                                                                                                                                                                                            | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| open | dices                                                   |                                                                                                                                                                                                                                                                                                                                                                                                   | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Ren  | note N                                                  | Iemory Device Tree                                                                                                                                                                                                                                                                                                                                                                                | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

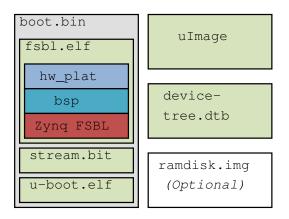

| Boo  | table [                                                 | Media                                                                                                                                                                                                                                                                                                                                                                                             | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | Sha:<br>6.1<br>6.2<br>Con<br>7.1<br>7.2<br>open-<br>Ren | 5.2 Linux<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br><b>Shared No</b><br>6.1 Network<br>6.1 Network<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>6.1.9<br>6.1.10<br>6.1.11<br>6.1.12<br>6.1.13<br>6.2 Evalua<br>6.2.1<br>6.2.2<br>6.2.3<br><b>Conclusion</b><br>7.1 Conclusion<br>7.2 Future<br><b>pendices</b><br><b>Remote No</b> | 5.2       Linux Microbenchmarks         5.2.1       Latency         5.2.2       Data Transfer Throughput         5.2.3       Local Memory Throughput         5.2.4       DMA Throughput         5.2.5       DMA Throughput vs. Data Size         5.2.6       Remote Swap I/O Throughput         5.2.7       Remote Swap I/O Throughput with DMA         5.2.8       Swap Devices Comparison         Shared Network Interface         6.1       Network Driver         6.1.4       Stater-Gather & Ring Descriptors         6.1.5       Receiving a Frame         6.1.6       Checksum Offloading         6.1.7       Interrupt Coalesce         6.1.8       ethtool Interface         6.1.9       MAC Configuration         6.1.10       Management Data Input/Output (MDIO) & XGMII         6.1.11       Network Statistics         6.1.2       Device Tree         6.1.3       Zero Copy Anecdotes         6.2       Evaluation         6.2.1       Bare-Metal Throughput         6.2.2       TCP Throughput         6.2.3       Raw Ethernet Throughput         6.2.3       Raw Ethernet Throughput         6.2.3       Raw Ethernet Throughpu |

# List of Figures

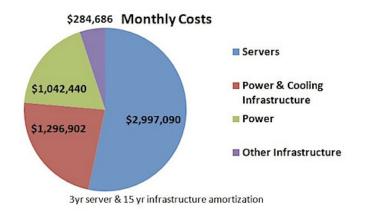

| 1.1 | Data Center costs breakdown. Source: James Hamilton, Amazon<br>Web Services                                                                                                                                                                                              | 6   |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

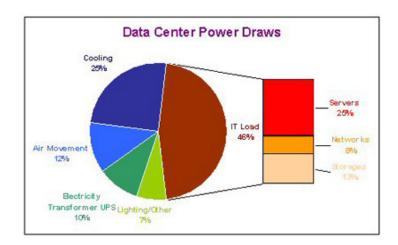

| 1.2 | Data Center power draws. Source: IMEX Research                                                                                                                                                                                                                           | 7   |

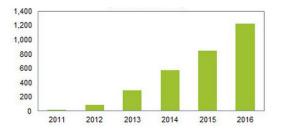

| 1.3 | Worldwide microserver shipment forecast (Thousands of Units). Source                                                                                                                                                                                                     |     |

| 1.0 | IHS iSuppli Research, February 2013                                                                                                                                                                                                                                      | . 7 |

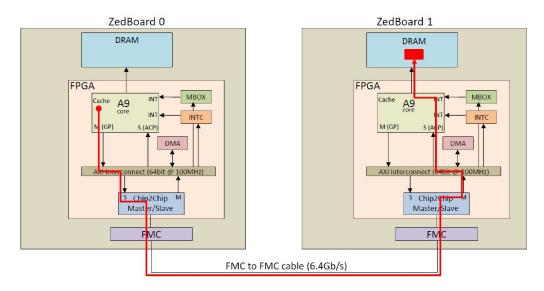

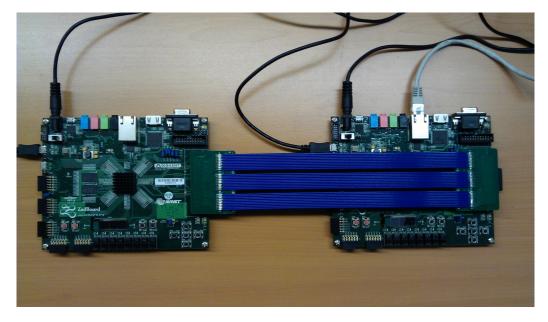

| 3.1 | Generation 1 Prototype using two Zedboards                                                                                                                                                                                                                               | 14  |

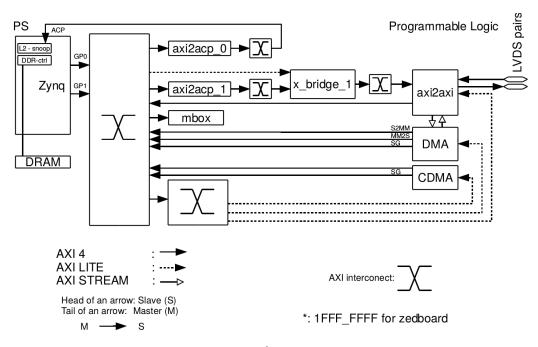

| 3.2 | Physical View of the Gen.1 Prototype                                                                                                                                                                                                                                     | 15  |

| 3.3 | Detailed Hardware Blocks & Protocols Diagram of Gen.1 Prototype                                                                                                                                                                                                          | 15  |

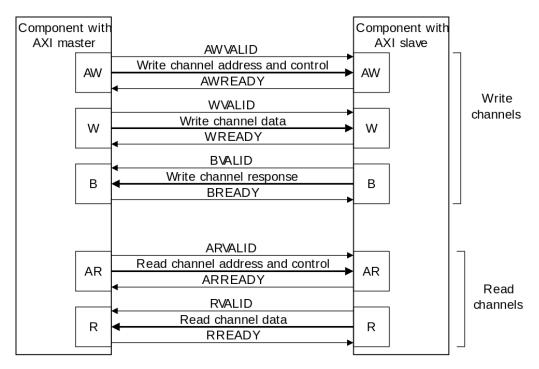

| 3.4 | The AXI Protocol. Source: ARM RealView ESL API v2.0 Devel-                                                                                                                                                                                                               |     |

|     | $oper's \ Guide$                                                                                                                                                                                                                                                         | 16  |

| 3.5 | Physical address translation                                                                                                                                                                                                                                             | 18  |

| 3.6 | Gen.2 Prototype Hardware Block Diagram                                                                                                                                                                                                                                   | 19  |

| 3.7 | Physical View of the Gen.2 Prototype                                                                                                                                                                                                                                     | 20  |

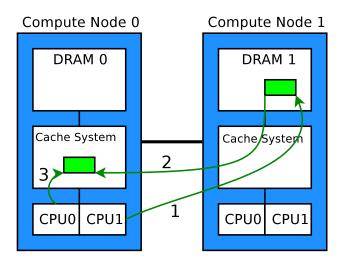

| 4.1 | User Cached Page Borrowing                                                                                                                                                                                                                                               | 24  |

| 4.2 | Owner Cached Page Borrowing                                                                                                                                                                                                                                              | 24  |

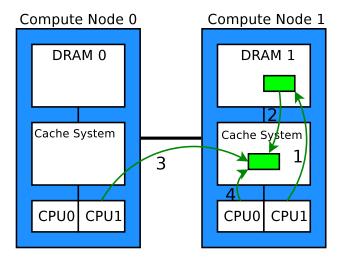

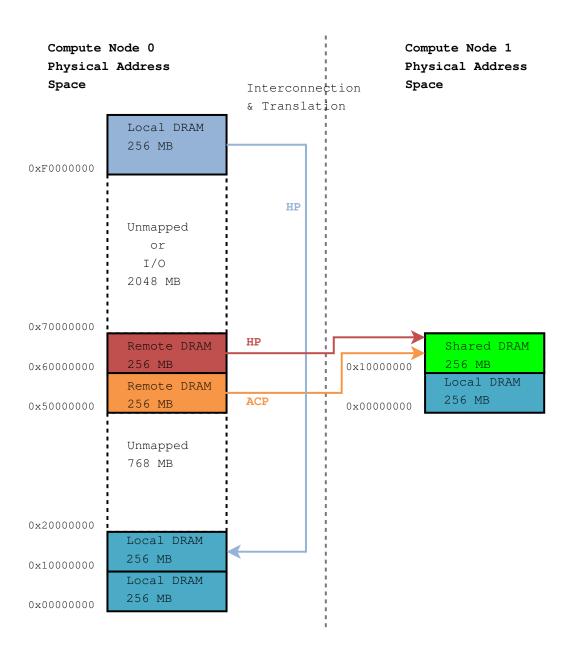

| 4.3 | Memory Mappings in a Sparse Memory Model, as it is used in our<br>system. Physical address space of Compute Node 0 at the left and<br>Node 1's at the right. The arrows show the memory mapping and the<br>port used (ACP or HP). HEX numbers at the left of each memory |     |

|     | space show the start address of each segment. (Note: Mappings for                                                                                                                                                                                                        |     |

|     | I/O peripherals is not shown.)                                                                                                                                                                                                                                           | 26  |

| 4.4 | Remote Memory as Main Memory Extension                                                                                                                                                                                                                                   | 28  |

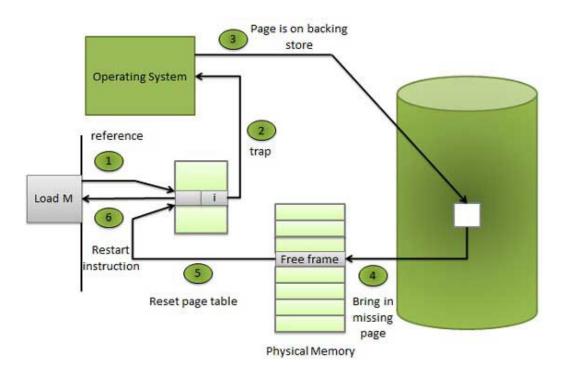

| 4.5 | Page fault and physical frame recovery                                                                                                                                                                                                                                   | 32  |

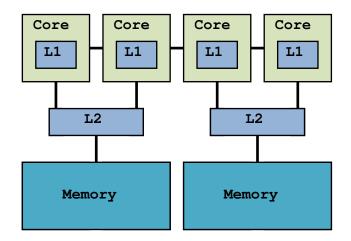

| 4.6 | A simple NUMA platform                                                                                                                                                                                                                                                   | 38  |

| 5.1 | AXI Read Request latency in Logic Analyzer                                                                                                                                                                                                                               | 43  |

| 5.2 | AXI Write Request latency in Logic Analyzer                                                                                                                                                                                                                              | 44  |

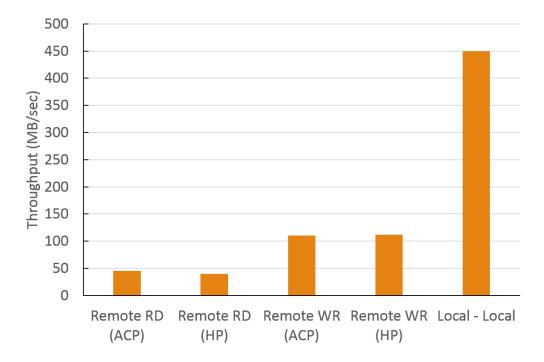

| 5.3 | Data transfer throughput using Load/Store instructions                                                                                                                                                                                                                   | 48  |

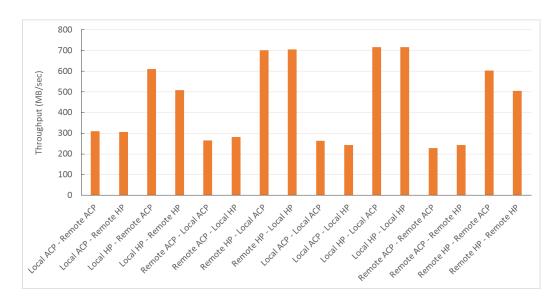

| 5.4 | DMA data transfer throughput                                                                                                                                                                                                                                             | 50  |

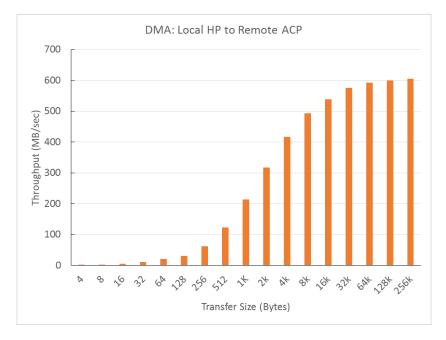

| 5.5 | DMA data transfer throughput vs. data size (Local to Remote) $\ .$ .                                                                                                                                                                                                     | 52  |

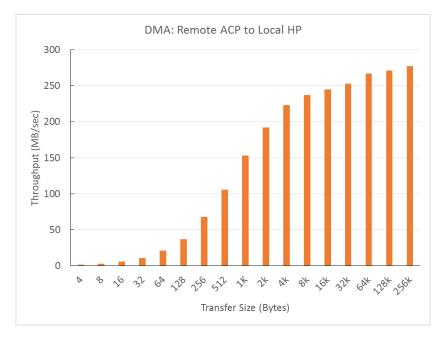

| 5.6 | DMA data transfer throughput vs data size (Remote to Local) $\cdot$ .                                                                                                                                                                                                    | 52  |

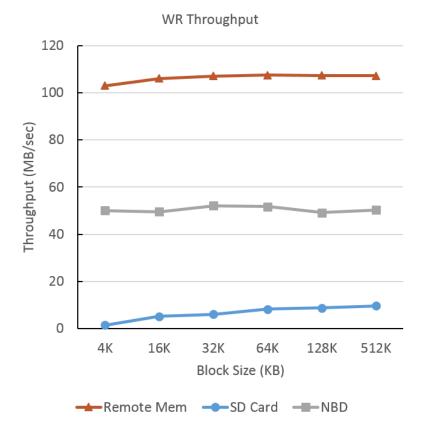

| 5.7 | Swap write I/O throughput $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                 | 54  |

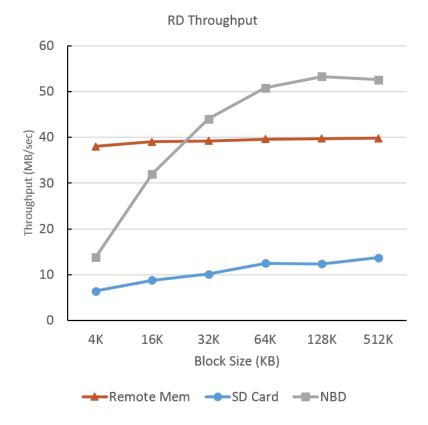

| 5.8  | Swap read I/O throughput                          |

|------|---------------------------------------------------|

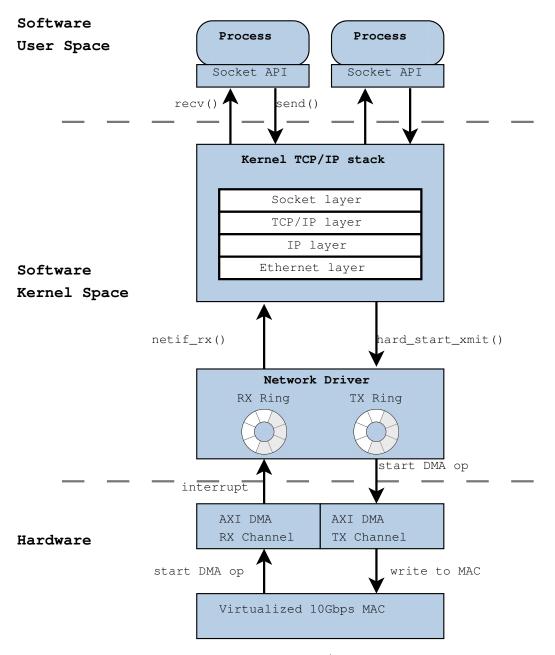

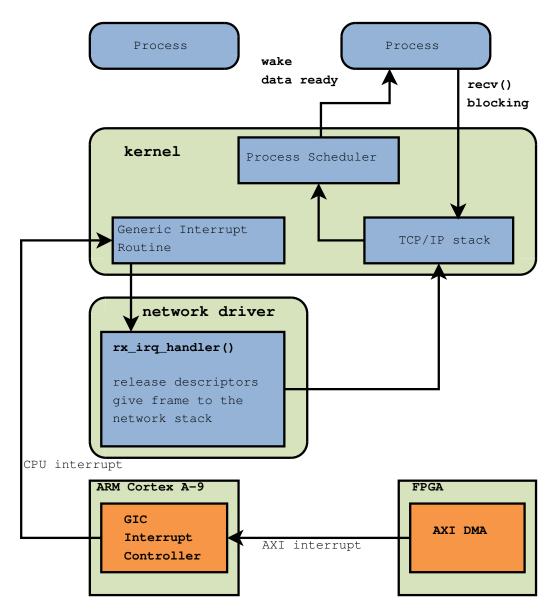

| 6.1  | Network traffic send/recv flow chart              |

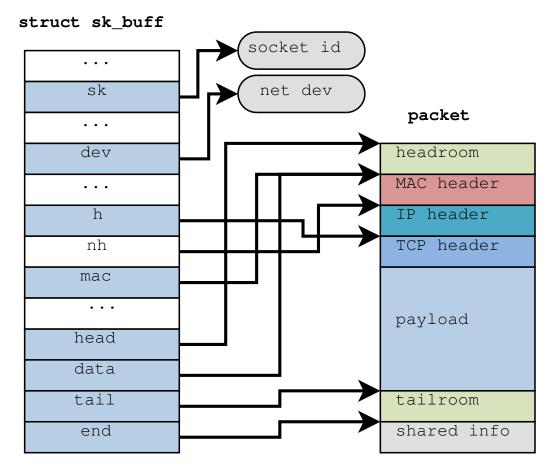

| 6.2  | sk_buff structure                                 |

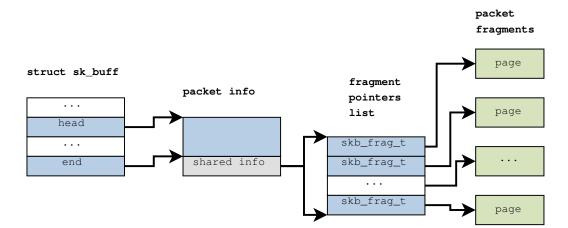

| 6.3  | sk_buff structure describing fragmented packet 61 |

| 6.4  | AXI DMA descriptor                                |

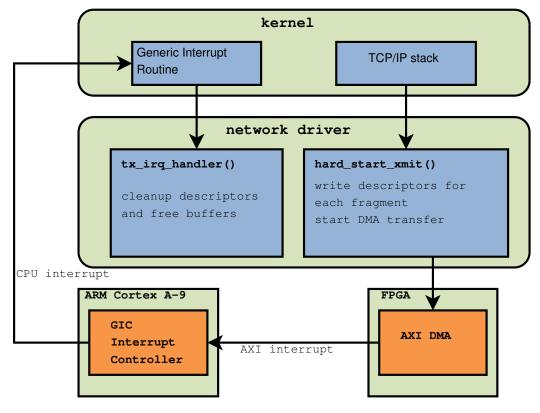

| 6.5  | TX flow chart                                     |

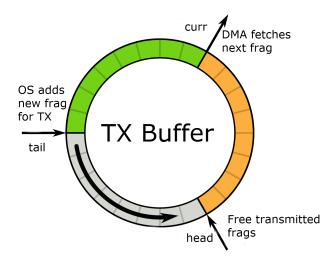

| 6.6  | TX descriptors ring                               |

| 6.7  | RX flow chart                                     |

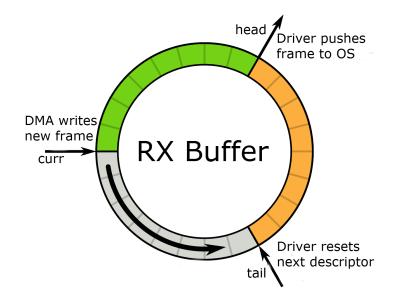

| 6.8  | RX descriptors ring                               |

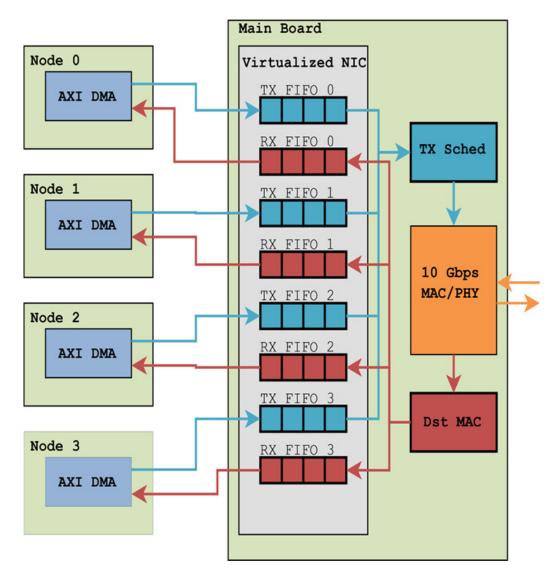

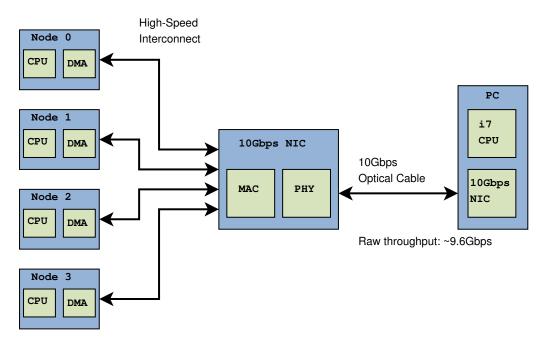

| 6.9  | Shared NIC evaluation setup                       |

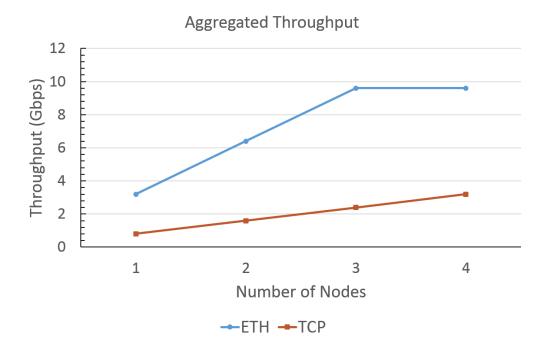

| 6.10 | Throughput for TCP and Raw Eth                    |

| B.1  | Boot Parition of the SD card                      |

# List of Tables

| 4.1 | Physical Memory Mapping and Translation                           | 27 |

|-----|-------------------------------------------------------------------|----|

| 5.1 | Data transfer throughput (for bare-metal application).            | 45 |

| 5.2 | DMA data transfer throughput (for bare-metal application)         | 46 |

| 5.3 | Data transfer throughput using Load/Store instructions            | 47 |

| 5.4 | Data transfer throughput using Load/Store instructions (for Local |    |

|     | DRAM)                                                             | 49 |

| 5.5 | DMA data transfer throughput                                      | 50 |

| 6.1 | Implemented functions of the <i>ethtool</i> interface             | 69 |

| 6.2 | 10Gbps MAC Configuration Registers                                | 70 |

## Chapter 1

# Introduction