### UNIVERSITY OF CRETE DEPARTMENT OF COMPUTER SCIENCE

### Techniques for Enhancing Parallelism in Mechanisms that Automatically Execute Sequential Code in Concurrent Environments

Dissertation Submitted by

### Eleftherios Kosmas

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

Heraklion, February 2015

### University of Crete Department of Computer Science

# Techniques for Enhancing Parallelism in Mechanisms that Automatically Execute Sequential Code in Concurrent Environments

Dissertation submitted by

### **Eleftherios Kosmas**

in partial fulfillment of the requirements for the Doctor of Philosophy degree in Computer Science

| Author:                | Eleftherios Kosmas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Examination Committee: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                        | Panagiota Fatourou, Assistant Professor, University of Crete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                        | to the state of th |

|                        | Angelos Bilas, Professor, University of Crete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                        | Lejaley (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        | Dimitrios S. Nikolopoulos, Professor, Queen's University of Belfast                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                        | Polyros Patikakis, Tesearcher, Foundation for Research and Technolog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                        | Valsilios V. Dimikopoulos, Associate Professor, University of Ioannina                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | Faith Ellen, Professor, University of Toronto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                        | Poel Ram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        | Paolo Romano, Assistant Professor, University of Lisbon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Departmental approval: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| •                      | Antonis A. Argyros, Professor, University of Crete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Heraklion, February 2015

Co-financed by Greece and the European Union

### Acknowledgements

This work is a result of the continuous support provided by my supervisor Panagiota Fatourou.

I would like to thank the co-authors of my results, Faith Ellen, Alessia Milani, Corentin Travers, Shlomi Dolev, Hillel Avni, Mykhailo Iaremko, Eleni Kanellou, and M. Forhad Rabbi. I am grateful for meeting and working with them, not only because our discussions inspired most of the work in this thesis, but most importantly because they significantly helped me enjoy this long journey.

Also, I would like to thank the members of my advisory committee Angelo Bila and Dimitrio S. Nikolopoulo for their helpful suggestions, and the rest members of my examination committee Polyvio Pratikaki, Vassilio D. Dimakopoulo, Faith Ellen, and Paolo Romano for carefully reading my thesis and providing useful comments.

This work was supported by the project "IRAKLITOS II - University of Crete" of the Operational Programme for Education and Lifelong Learning 2007 - 2013 (E.P.E.D.V.M.) of the NSRF (2007 - 2013), which is co-funded by the European Union (European Social Fund) and National Resources. Moreover, I would like to acknowledge the support of the Institute of Computer Science of the Foundation of Research and Technology (FORTH-ICS) and especially the DCS and CARV research laboratories.

### **Abstract**

Two well-known mechanisms for automatically executing sequential code segments in a concurrent environment are universal constructions and software transactional memory. They both have the same goal of simplifying the task of parallel programming. A *universal construction* is a mechanism which takes as input the sequential code and executes it in a concurrent environment. *Software transactional memory* (STM) employs *transactions* to avoid conflicting accesses to common data (known as *data items* or *transactional variables*). A transaction may either *commit*, in which case it appears as if it has been executed at a single point in time, or *abort*, in which case it appears as if it is never executed. Notice that if a transaction commits, then its updates to data items become visible, otherwise, if it aborts, all its changes are discarded.

In this thesis, we study how to achieve increased concurrency while designing such mechanisms, without sacrificing correctness and progress. One well-studied technique for enhancing concurrency is ensuring a property called disjoint-access parallelism. Roughly speaking, *disjoint-access parallelism* guarantees that processes operating on different parts of an implemented object do not interfere with each other. Thus, disjoint-access parallel implementations allow for increased parallelism.

*Wait-freedom* is a well-known progress property which ensures that each process completes its execution, even when other processes run at arbitrary speeds or crash. Wait-freedom is highly desirable because implementations ensuring this property are highly fault-tolerant and usually ensure bounds on the number of steps executed before an implemented operation responds.

In this thesis, we prove that it is not possible for a universal construction to achieve both disjoint-access parallelism and wait-freedom; this impossibility result holds for STM as well. Specifically, we identify a natural property of universal constructions and prove that there is no universal construction (with this property) that ensures both disjoint-access parallelism and wait-freedom. Our impossibility proof is obtained by considering a dynamic data structure that can grow arbitrarily large during an execution. This impossibility result can be beaten if we focus on data structures that have a bound on the number of pieces of data accessed by each operation they support. For this setting, we present a universal construction that ensures both wait-freedom and disjoint-access parallelism.

We further introduce and study weaker versions of disjoint-access parallelism, which still however allow for increased parallelism. Motivated be the way current STM algorithm work, we introduce *timestamp-ignoring disjoint-access parallelism*, which allows operations operating on different parts of an implemented data structure to proceed in parallel, except for accesses to a timestamp object. A *timestamp object* allows a process to know the "time" at which it accesses the object, relative to accesses by other processes (on the same timestamp object); specifically, a process is able to determine whether it accessed the object before or after some other process accessed it. We present a universal construction that ensures wait-freedom and timestamp-ignoring disjoint-access parallelism, for certain classes of data structures.

We next concentrate on important issues in achieving enhanced parallelism in STM computing. Most STM algorithms employ an *optimistic* approach, where transactions are executed speculatively, as if they will never read inconsistent data. When a conflict occurs, STM algorithms usually abort one of the transactions to ensure correctness; two concurrent transactions *conflict* if they both access the same data item and at least one of them attempts to modify it. The work performed by a transaction that aborts is discarded and it is later re-executed as a new transaction; this incurs a performance penalty. Moreover, for read-intensive workloads, it is really important to ensure that transactions that never update a data item (which are called *read-only* transactions) never abort and are *wait-free*; i.e. they always commit within a finite number of steps. For these reasons, the literature also contains *pessimistic* STM algorithms, which never abort transactions and support wait-freedom for read-only transactions. However, most of them achieve this by "pessimistically" requiring transactions that update data items (called *update* transactions) to be executed sequentially. This significantly restricts parallelism in many cases and therefore it also leads to performance degradation.

As a first step towards achieving enhanced parallelism, we introduce WFR-TM, an STM algorithm which attempts to combine some of the advantages of pessimistic and optimistic STM. In WFR-TM, as in pessimistic STMs, read-only transactions never abort and are

wait-free. WFR-TM additionally ensures that read-only transactions never execute expensive synchronization instructions. In contrast to pessimistic STMs, these properties are achieved without sacrificing all parallelism between update transactions. More specifically, update transactions use a pessimistic approach to synchronize with concurrently executed read-only transactions: they wait for read-only transactions to complete. However, they use an optimistic approach to synchronize with each other: they are executed concurrently in a speculative way, and they commit if they have not encountered any conflict with other update transactions during their execution. Thus, WFR-TM achieves more parallelism than pessimistic STMs.

Finally, we introduce SemanticTM, an STM algorithm in which parallelism is achieved at the level of transactional instructions; i.e. not only the transactions themselves but also the instructions of each transaction may be executed concurrently. With compiler support, SemanticTM guarantees that simple transactions are wait-free, by ensuring that no transactions conflict. We remark that STM algorithms that never abort transactions are highly desirable since they additionally support transactions that perform irrevocable operations, e.g. I/O operations.

**keywords**: Asynchronous System, Shared-Memory, Concurrent Programming, Universal Construction, Software Transactional Memory (STM), Optimistic STM, Pessimistic STM, Disjoint-Access Parallelism, Wait-Freedom, Impossibility, Timestamps, Read-only Transactions, Abort-Free Transactions, Fine-Grained Parallelism

# Περίληψη

Μέχρι πρόσφατα, η αύξηση της συχνότητας του επεξεργαστή αποτελούσε την χυρίαρχη τεχνιχή για τη βελτίωση της απόδοσής του. Ωστόσο, τα τελευταία χρόνια, φυσιχοί περιορισμοί μιχροηλεχτρονιχής φύσης δεν επιτρέπουν την περαιτέρω αύξηση της συχνότητας του επεξεργαστή. Η συνεχόμενη ανάγχη των σύγχρονων εφαρμογών για αυξημένη επεξεργαστιχή ισχύ οδήγησε τους μεγαλύτερους χατασχευαστές επεξεργαστών στη σχεδίαση πολυπύρηνων αρχιτεκτονικών, όπου πολλαπλές επεξεργαστιχές μονάδες ή πυρήνες εμπεριέχονται στον ίδιο επεξεργαστή.

Σε επίπεδο λογισμικού, χρησιμοποιούμε τον όρο διεργασία για να αναφερθούμε στη συνάρτηση που εκτελείται σε κάποιο πυρήνα και αναλαμβάνει να εκτελέσει την ακολουθία εντολών που καταφθάνουν σε αυτόν τον πυρήνα. Οι διεργασίες αυτές μοιράζονται μία κοινή ή διαμοιραζόμενη μνήμη, στην οποία διατηρούνται τα δεδομένα της εκάστοτε εφαρμογής. Επίσης, οι διεργασίες ενδέχεται να σφάλλουν, δηλαδή να σταματήσουν να λειτουργούν οποιαδήποτε χρονική στιγμή.

Οι εφαρμογές μπορούν να ευεργετηθούν από τις πολυπύρηνες αρχιτεκτονικές εάν ο κώδικας τους γραφτεί με τέτοιο τρόπο ώστε τμήματά τους να εκτελούνται παράλληλα από διαφορετικές διεργασίες. Ιδανικά η αύξηση της απόδοσης της εφαρμογής θα ήταν γραμμική ως προς το πλήθος των πυρήνων. Ωστόσο, αυτή η αύξηση επιτυγχάνεται μόνο σε εξαιρετικές περιπτώσεις εφαρμογών. Συνήθως τα διαφορετικά τμήματα μιας εφαρμογής αλληλοεξαρτώνται, επιβάλλοντας έτσι την ανάγκη επίτευξης συγχρονισμού μεταξύ των διεργασιών κατά την προσπέλαση διαμοιραζόμενων δεδομένων. Όμως είναι κοινά αποδεκτό ότι η ανάπτυξη παράλληλων προγραμμάτων επιτυγχάνοντας ταυτόχρονα συγχρονισμό και υψηλή απόδοση, είναι μια δύσκολη διαδικασία, η οποία γίνεται κυρίως από έμπειρους προγραμματιστές.

Έχοντας ως κύριο στόχο την απλοποίηση της διαδικασίας παράλληλου προγραμματισμού, στην παρούσα διατριβή μελετούμε δύο γενικούς μηχανισμούς που αυτοματοποιο-

ύν τη διαδικασία ανάπτυξης παράλληλων προγραμμάτων, υποστηρίζοντας την εκτέλεση οποιουδήποτε σειριακού κώδικα σε ένα πολυπύρηνο επεξεργαστή. Συγκεκριμένα μελετούμε τα καθολικά αντικείμενα (universal constructions ή UC) και την τεχνική συγχρονισμού διεργασιών μέσω δοσοληψιών (software transactional memory ή STM).

Ένα UC σύστημα αναλαμβάνει να εφαρμόσει ατομικά έναν σειριακό κώδικα στα δεδομένα της εφαρμογής που διατηρούνται στη διαμοιραζόμενη μνήμη. Από την άλλη, ένα STM σύστημα επιχειρεί να εκτελέσει ατομικά έναν σειριακό κώδικα ως μία δοσοληψία, η οποία μπορεί να καταλήξει είτε ως επιτυχής, καθιστώντας όλες τις αλλαγές που εφάρμοσε στη διαμοιραζόμενη μνήμη ορατές στις υπόλοιπες δοσοληψίες, είτε ως μη-επιτυχής, οπότε οι αλλαγές της αγνοούνται. Αυτή είναι και η βασική διαφορά των δύο αυτών τεχνικών.

Μια εξαιρετικά επιθυμητή ιδιότητα για τη βελτίωση του παραλληλισμού είναι η παραλληλία αποσπασματικής προσπέλασης (disjoint access parallelism, ή DAP). Διαισθητικά, η ιδιότητα DAP απαιτεί από διαφορετικές διεργασίες που προσπελάζουν διαφορετικά τμήματα της διαμοιραζόμενης μνήμης να μην προκαλούν παρεμβολές η μία στην άλλη, έτσι ώστε να μπορούν να εκτελεστούν ταυτόχρονα. Μία ακόμη εξαιρετικά επιθυμητή ιδιότητα είναι η ιδιότητα προόδου ελευθερία-αναμονής, καθώς παρέχει πεπερασμένη χρονική πολυπλοκότητα και μέγιστη ανοχή σφαλμάτων. Συγκεκριμένα κάθε διεργασία εφαρμόζει τον σειριακό κώδικα που εκτελεί σε πεπερασμένο χρονικό διάστημα, ανεξάρτητα από τις αποτυχίες ή την ταχύτητα των υπόλοιπων διεργασιών.

Ωστόσο, αποδειχνύουμε με αυστηρό τρόπο ότι είναι αδύνατο να σχεδιασθεί ένας UC ή STM αλγόριθμος που ιχανοποιεί ταυτόχρονα τις ιδιότητες ελευθερία-αναμονής και DAP για οποιαδήποτε εφαρμογή. Η απόδειξή μας βασίζεται σε μία δομή δεδομένων το πλήθος των στοιχείων της οποίας μπορεί να μεγαλώσει αυθαίρετα χατά τη διάρχεια μιας εχτέλεσης. Σε αντίθεση, παρουσιάζουμε έναν UC αλγόριθμο που ιχανοποιεί τις ιδιότητες ελευθερία-αναμονής χαι DAP για εφαρμογές που έχουν χάποιο άνω όριο στο πλήθος των δεδομένων που χάθε σειριαχός χώδιχάς τους μπορεί να προσπελάσει, σε οποιαδήποτε εχτέλεση.

Για να ξεπεράσουμε αυτό το αρνητικό αποτέλεσμα, προτείνουμε μία ασθενέστερη έκδοση της ιδιότητας DAP, η οποία επιτρέπει σε δύο διεργασίες να προσπελάζουν το ίδιο αντικείμενο απόδοσης χρονοσφραγίδων, ακόμη και εάν προσπελάζουν διαφορετικά τμήματα της διαμοιραζόμενης μνήμης. Επομένως, ενώ καταστρατηγεί μερικώς την ιδιότητα DAP, και η έκδοση αυτή βελτιώνει τον παραλληλισμό. Στη συνέχεια, παρου-

σιάζουμε έναν UC αλγόριθμο που ικανοποιεί αυτή την έκδοση της ιδιότητας DAP και την ιδιότητα ελευθερία-αναμονής.

Ακόμη, για την επίτευξη προόδου και τη βελτίωση του παραλληλισμού οι περισσότεροι αλγόριθμοι STM ακολουθούν μία αισιόδοξη τεχνική, όπου οι δοσοληψίες εκτελούνται χρησιμοποιώντας τιμές διαμοιραζόμενων δεδομένων που δεν είναι απαραίτητα συνεπής. Σε περιπτώσεις συνωστισμού κατά την προσπέλαση συγκεκριμένων τμημάτων της διαμοιραζόμενης μνήμης, ενδέχεται κάποιες ή και όλες οι δοσοληψίςε να αποτυγχάνουν, μειώνοντας έτσι την απόδοση της εφαρμογής. Από την άλλη, σε έναν απαισιόδοξο STM αλγόριθμο όλες οι δοσοληψίες εκτελούνται επιτυχώς. Ωστόσο, οι δοσοληψίες που τροποποιούν δεδομένα της διαμοιραζόμενης μνήμης, ή αλλιώς δοσοληψίες ενημέρωσης, εκτελούνται σειριακά η μία μετά την άλλη. Αυτό μειώνει σημαντικά τον παραλληλισμό σε πολλές περιπτώσεις και οδηγεί σε μείωση της απόδοσης.

$\Omega$ ς πρώτο βήμα για την επίτευξη τόσο προόδου όσο και παραλληλισμού στην τεχνική STM, προτείνουμε τον STM αλγόριθμο WFR-TM ο οποίος συνδυάζει πλεονεκτήματα τόσο από τους αισιόδοξους όσο και από τους απαισιόδοξους STM αλγορίθμους. Ο αλγόριθμος WFR-TM εγγυάται την ιδιότητα προόδου ελευθερίας-αναμονής για όσες δοσοληψίες δεν τροποποιούν δεδομένα της διαμοιραζόμενης μνήμης, ή αλλιώς δοσοληψίες ανάγνωσης, αποφεύγοντας τη σειριαχή εκτέλεση των δοσοληψιών ενημέρωσης. Οι δοσοληψίες ενημέρωσης χρησιμοποιούν μία απαισιόδοξη τεχνική για να συγχρονιστούν με τις δοσοληψίες ανάγνωσης. Συγκεκριμένα, περιμένουν τις δοσοληψίες ανάγνωσης να ολοχληρωθούν. Επίσης, οι δοσοληψίες ενημέρωσης χρησιμοποιούν μία αισιόδοξη τεχνική για να συγχρονιστούν μεταξύ τους. Συγκεκριμένα, εκτελούνται ταυτόχρονα και μία δοσοληψία ενημέρωσης ολοκληρώνεται επιτυχώς μόνο εάν καμία άλλη δοσοληψία ενημέρωσης δεν προσπελάζει ταυτόχρονα το τμήμα της διαμοιραζόμενης μνήμης στο οποίο εργάζεται. Αξίζει να σημειωθεί ότι ο αλγόριθμος WFR-TM εγγυάται ότι κάθε δοσοληψία ενημέρωσης περιμένει ένα πεπερασμένο πλήθος από δοσοληψίες ανάγνωσης. Επίσης, με δεδομένο πως καμία διεργασία δε σφάλει, ο αλγόριθμος WFR-TM εγγυάται ότι σε κάθε σημείο της εκτέλεσης υπάρχει μία δοσοληψία ενημέρωσης που μπορεί να εκτελεστεί επιτυχώς σε πεπερασμένο χρονικό διάστημα.

Τέλος, προτείνουμε τον STM αλγόριθμο Semantic-TM ο οποίος εγγυάται πως όλες οι δοσοληψίες υποστηρίζουν την ιδιότητα προόδου ελευθερία-αναμονής. Ο αλγόριθμος Semantic-TM επιτυγχάνει 'λεπτόχοχχο' παραλληλισμό στο επίπεδο των εντολών των δοσοληψιών, το οποίο επιτρέπει τόσο την ταυτόχρονη εχτέλεση δοσοληψιών όσο χαι την

ταυτόχρονη εκτέλεση ανεξάρτητων μεταξύ τους εντολών της ίδιας δοσοληψίας.

**Λέξεις κλειδιά**: Ασύγχρονο Σύστημα, Διαμοιραζόμενη Μνήμη, Παράλληλος Προγραμματισμός, Καθολικά Αντικείμενα, Συγχρονισμός Διεργασιών Μέσω Δοσοληψιών, Παραλληλία Αποσπασματικής Προσπέλασης, Ελευθερία-Αναμονής, Αρνητικό Αποτέλεσμα, Αντικείμενο Χρονο-Σφραγίδων, Αισιόδοξος, Απαισιόδοξος Συγχρονισμός Διεργασιών Μέσω Δοσοληψιών, Δοσοληψίες-Ανάγνωσης, Δοσοληψίες Ελεύθερες Αποτυχιών, Λεπτόκοκκος Παραλληλισμός

## **Contents**

| A  | cknow   | vieagements                                                               | 1    |

|----|---------|---------------------------------------------------------------------------|------|

| A  | bstrac  | rt                                                                        | iii  |

| E  | xtendo  | ed Abstract in Greek                                                      | vii  |

| Ta | able of | f Contents                                                                | xi   |

| Li | st of l | Figures                                                                   | XV   |

| Li | st of T | Tables                                                                    | xvii |

| 1  | Intr    | oduction                                                                  | 1    |

|    | 1.1     | Motivation                                                                | 2    |

|    | 1.2     | Focus                                                                     | 3    |

|    | 1.3     | Contribution                                                              | 5    |

|    |         | 1.3.1 Disjoint-Access Parallelism in Shared-Memory Computing              | 5    |

|    |         | 1.3.2 New Software Transactional Memory Algorithms                        | 7    |

|    | 1.4     | Roadmap                                                                   | 9    |

| 2  | Mod     | lel                                                                       | 11   |

|    | 2.1     | Abstract Data Types                                                       | 12   |

|    | 2.2     | Sequential Data Structures                                                | 12   |

|    | 2.3     | Model of Computation                                                      | 14   |

|    | 2.4     | Concurrent Data Structures                                                | 15   |

|    | 2.5     | Transforming a Sequential Data Structure to a Concurrent Data Structure . | 16   |

|    |         | 2.5.1 Universal Constructions                                             | 16   |

|    |         | 2.5.2 Software Transactional Memory                                       | 16   |

|    |         | 2.5.3 Common Definitions                                                  | 18   |

|    | 2.6     | Correctness                                                               | 18   |

|    | 2.7     | Progress                                                                  | 20   |

|    | 2.8     | Data Set of an Operation                                                  | 22   |

#### **Contents**

|   | 2.9  | Disjoint-Access Parallelism                                                | 22 |

|---|------|----------------------------------------------------------------------------|----|

| 3 | Rela | ated Work                                                                  | 25 |

|   | 3.1  | Disjoint-Access Parallelism Definitions                                    | 26 |

|   | 3.2  | Impossibilities for Disjoint-Access Parallelism in Shared-Memory Computing | 27 |

|   | 3.3  |                                                                            | 29 |

|   | 3.4  | 3                                                                          | 31 |

|   | 3.5  | •                                                                          | 32 |

|   | 3.6  |                                                                            | 34 |

| 4 | Disi | oint-Access Parallelism in Shared-Memory Computing                         | 37 |

| - | 4.1  | v i e                                                                      | 38 |

|   | 4.2  |                                                                            | 38 |

|   | 4.3  |                                                                            | 43 |

|   | 4.4  |                                                                            | 48 |

|   | 7.7  |                                                                            | 48 |

|   |      |                                                                            | 49 |

|   |      | <b>y</b>                                                                   | 64 |

|   |      |                                                                            | 68 |

|   | 15   | 3                                                                          |    |

|   | 4.5  | The TI-DAP-UC Universal Construction                                       | 75 |

| 5 |      | • 0                                                                        | 81 |

|   | 5.1  |                                                                            | 82 |

|   | 5.2  |                                                                            | 82 |

|   | 5.3  |                                                                            | 84 |

|   | 5.4  | e                                                                          | 86 |

|   | 5.5  | Proof of the WFR-TM Algorithm                                              | 91 |

|   |      | 5.5.1 Preliminaries                                                        | 91 |

|   |      | 5.5.2 Correctness                                                          | 99 |

|   |      | 5.5.3 Progress                                                             | 02 |

| 6 | The  | SemanticTM Software Transactional Memory Algorithm 1                       | 07 |

|   | 6.1  | General                                                                    | 80 |

|   | 6.2  | Main Ideas                                                                 | 80 |

|   |      | 6.2.1 Dependencies                                                         | 09 |

|   |      | •                                                                          | 11 |

|   |      |                                                                            | 12 |

|   |      | 1                                                                          | 14 |

|   |      | $\mathcal{E}$                                                              | 15 |

|   | 6.3  |                                                                            | 16 |

|   | 0.5  |                                                                            | 16 |

|   |      | 6.3.2 The Code of the SemanticTM Algorithm                                 |    |

|   |      | 0.5.2 The Code of the beniantie in Algorithm                               | ~  |

xii Contents

| 0- |   | 4 - |    | 4 - |

|----|---|-----|----|-----|

| Co | n | T£  | 'n | IIS |

|    |       | 6.4.2<br>6.4.3 | Preliminaries                     |             |

|----|-------|----------------|-----------------------------------|-------------|

|    | 6.5   | Experi         | imental Evaluation                | . 163       |

|    |       | 6.5.1          | The system                        | . 163       |

|    |       | 6.5.2          | Tested Workload                   | . 163       |

|    |       | 6.5.3          | Results                           | . 170       |

| 7  | Con   | clusion        | and Future Research               | <b>17</b> 1 |

|    | 7.1   | Synop          | osis of Contribution              | . 172       |

|    | 7.2   | Direct         | ions for Future Work and Research | . 173       |

| Au | thor' | 's Publi       | cations                           | 175         |

| Bi | bliog | raphy          |                                   | 179         |

Contents xiii

# **List of Figures**

| 2.1  | SEARCH                                                                             | 13  |

|------|------------------------------------------------------------------------------------|-----|

| 3.1  | A Comparison of Different Definitions of Disjoint Access Parallelism               | 27  |

| 4.1  | The Execution $\alpha$ with Solo Executions of Search( $L,0$ ) Starting from Var-  |     |

|      | ious Configurations                                                                | 39  |

| 4.2  | An Infinite Execution $\alpha'$ with a Non-terminating SEARCH Operation            | 40  |

| 4.3  | The Execution Obtained from $\alpha$ by Replacing Append $(L,i)$ by Append $(L,0)$ | 41  |

| 4.4  | Type Definitions of DAP-UC                                                         | 43  |

| 4.5  | The Code of Perform of DAP-UC                                                      | 44  |

| 4.6  | The Code of HELP of DAP-UC                                                         | 45  |

| 4.7  | The Code of Announce and ConcurrentAccesses of DAP-UC                              | 46  |

| 4.8  | Type Definitions and the Code of PERFORM of TI-DAP-UC                              | 77  |

| 4.9  | The Code of HELP of TI-DAP-UC                                                      | 78  |

| 4.10 | The Code of Announce and ConcurrentAccesses of TI-DAP-UC                           | 79  |

| 5.1  | Data structures of WFR-TM                                                          | 85  |

| 5.2  | Pseudocode for BEGINTX, CHECKIFPERFORMED, CREATEDI, READDI, and VALIDATE of WFR-TM | 87  |

| 5.3  | Pseudocode for WRITEDI, COMMITTX, LOCKDATASET, and WAITREADERS of WFR-TM           | 88  |

| 6.1  | Main Components of SemanticTM. Extraction of Transactional Instruc-                |     |

|      | tions and Their Placement Into di-lists                                            | 109 |

| 6.2  | Transactions                                                                       | 110 |

| 6.3  | Type Definitions of SemanticTM                                                     | 117 |

| 6.4  | • 4                                                                                | 120 |

| 6.5  |                                                                                    | 121 |

| 6.6  | The Code of ParticipatesInLoop, ReadIterations, UpdateLoop-                        |     |

|      |                                                                                    | 122 |

| 6.7  | The Code of CHECKDD and EXECUTEINS of SemanticTM                                   | 123 |

### **List of Figures**

| 6.8  | The Code of UPDATEDI, RESOLVEDD, INITIALIZEDEPENDENTCONDS,                                  |     |

|------|---------------------------------------------------------------------------------------------|-----|

|      | and RESOLVECDINVALID of SemanticTM                                                          | 124 |

| 6.9  | Control Dependencies in SemanticTM                                                          | 131 |

| 6.10 | Type Definitions, and the Code of APPLYINSTRUCTIONS and RETURND-                            |     |

|      | DVALUES of the Simplified Version of SemanticTM                                             | 164 |

| 6.11 | The Code of Transaction $T_i$ , $1 \le i \le 4$ , Executed by process $k$ , $1 \le k \le N$ | 165 |

| 6.12 | Transactions With Long and Short Wait Time, to Demonstrate the Impact of                    |     |

|      | Different Amounts of Local Work, for $T_1 \ldots \ldots \ldots \ldots$                      | 166 |

| 6.13 | Transactions With Long and Short Wait Time, to Demonstrate the Impact of                    |     |

|      | Different Amounts of Local Work, for $T_2$                                                  | 167 |

| 6.14 | Transactions With Long and Short Wait Time, to Demonstrate the Impact of                    |     |

|      | Different Amounts of Local Work, for $T_3$                                                  | 168 |

| 6.15 | Transactions With Long and Short Wait Time, to Demonstrate the Impact of                    |     |

|      | Different Amounts of Local Work, for $T_A$                                                  | 169 |

xvi List of Figures

# **List of Tables**

| 5.1 | Useful Notation for the Proof of Correctness         | 93  |

|-----|------------------------------------------------------|-----|

| 6.1 | Data Dependencies Between Transactional Instructions | 112 |

# **Chapter 1**

# Introduction

### 1.1 Motivation

Up until recently, increasing CPU speed was the dominant approach for improving computer performance. However, the last few years, due to physical constraints the size of electronic circuits cannot become smaller; so CPU speed is no longer rising. The continuous demand for more efficient computing has led hardware designers to move towards *multi-core architectures*.

To take advantage of the increased computational power of multi-core machines, *concurrency* should be employed. Introducing as much concurrency as possible into software applications has become urgent. Remarkably, most of the current applications are sequential. To execute such an application concurrently its code segments that can be executed in parallel should first be identified. Then, concurrent algorithms should be provided to allow each processes to execute any of these segments concurrently with (and ideally, independently of) the other processes.

Ideally, the speed-up from parallelization would be linear in the number of cores. However, this speed-up is rarely achieved due to dependencies that exist and synchronization that is needed between the different code segments. Because of these complications, it is commonly accepted that writing concurrent programs is extremely hard work, currently undertaken only by experts. The difficulty is inherent in achieving communication and synchronization between processes that run concurrently. Despite the difficulty of concurrent programming, all modern applications must employ concurrency in order to achieve high performance.

To simplify concurrent programming we need mechanisms to automatically execute sequential code segments in a concurrent environment. Two well-established such mechanisms are universal constructions and software transactional memory. They both have the same goal of simplifying concurrent programming by providing mechanisms to efficiently execute sequential code in a concurrent environment.

A universal construction [1, 2] provides a concurrent implementation of any sequential data structure. Pieces of sequential code can be thought of as operations of a data structure. Thus, universal constructions can be used to execute any piece of sequential code (which may require synchronization) in a concurrent environment. Software transactional memory (STM) [3, 4] is a mechanism that allows a programmer of a sequential program to identify as transactions those pieces of the sequential code that require synchronization. Thus, a

transaction includes a sequence of instructions on pieces of the simulated state, known as *data items*. When the transaction is being executed in a concurrent environment, data items can be accessed by several processes simultaneously. Thus, synchronization is needed when accessing data items. If the transaction *commits*, all its changes take effect as if they all are applied sequentially at a given point in time during the execution of the transaction. Otherwise, the transaction *aborts* and none of its changes take effect.

In STM, when a transaction is aborted, the STM algorithm can choose whether or not to re-execute the transaction. A call to a universal construction returns only when the simulated code has been successfully applied to the simulated data structure. This is the main difference between these two paradigms.

A universal construction or STM system is implemented by an expert programmer who addresses all problems encountered when concurrency is employed. The resulting algorithms are guaranteed to be correct, and have specific progress and performance properties. The naive programmer simply provides sequential code and it is the universal construction or the STM system that undertakes the task to execute it concurrently. Thus, if universal constructions or STMs achieve enhanced parallelism, and therefore gain performance, they do so at no cost to the naive programmer.

#### 1.2 Focus

In this thesis, we study universal constructions and STMs from the perspective of achieving increased concurrency, without sacrificing correctness and progress. Specifically, the correctness property we consider for universal constructions is *linearizability* [5] and for STM systems it is *opacity* [6]. Roughly speaking, linearizability says that every completed operation (and some of the non-completed ones) appears as if it has been executed sequentially at some point within its execution interval. In addition to guaranteeing this condition for committed (and some *commit-pending*) transactions, opacity ensures that even transactions that do not commit see "consistent" simulated states.

To ensure fault-tolerance, we study implementations that ensure strong progress guarantees, namely wait-freedom and local progress. A universal construction implementation is *wait-free* if, in every execution, each (non-faulty) process completes its operation within a finite number of steps, even if other processes may fail (by crashing) or are very slow. We remark that it is common behavior of an STM algorithm to restart an aborted transaction

until it eventually commits. A meaningful progress condition [7, 8] in STM requires that the number of times each transaction aborts is finite. This property, known as *local progress* [7], is similar to wait-freedom.

We focus on established techniques to enhance parallelism; i.e. techniques that have received attention in previous research. One such technique is to ensure that an algorithm satisfies a property known as disjoint-access parallelism. Roughly speaking, *disjoint-access parallelism* guarantees that if two processes operate on disjoint parts of the simulated state, they do not access any common shared objects, so they do not interfere with one another. Therefore, disjoint-access parallelism allows unrelated operations to progress in parallel. This property has been extensively studied in the literature in the context of both universal constructions [9, 10] and STM [7, 11, 12, 13, 14, 15, 16, 17, 18].

Speculation is the main technique for achieving enhanced concurrency in the STM context. Specifically, processes *optimistically* execute instructions, using values that are not guaranteed to be consistent and taking corrective actions whenever they discover that these values are inconsistent. In cases where such corrective actions are rarely needed, e.g. under low contention, such a strategy may offer significant performance gains. The potential disadvantage of having processes perform unnecessary tasks is usually greatly outweighed by the enhanced concurrency it allows.

Most STM algorithms are optimistic: they execute transactions speculatively and they may proactively abort transactions if they "suspect" that their execution may jeopardize correctness. Specifically, when a conflict between two transactions occurs, STM algorithms usually abort one of the transactions to ensure consistency. Two concurrent transactions *conflict* if they both access the same data item and at least one of them attempts to modify it. Unfortunately, this proactive behavior often leads to a big number of *spurious* aborts, i.e. transactions are aborted even in cases where they could commit without violating consistency. Research on STM has given special attention to this issue [12, 19, 20, 21, 22, 23], as it degrades performance. The work performed by a transaction that aborts is discarded and it is later re-executed as a new transaction; this incurs a performance penalty. So, the nature of STM is optimistic: if transactions never abort then no work is ever discarded.

It is highly desirable that all transactions eventually commit. However, this property is not ensured by the currently available STM systems, which in their majority lead to many transaction aborts. STM algorithms that never abort transactions are highly desirable since they additionally support transactions that perform irrevocable operations, e.g. I/O

operations. Ideally, we would like to have STM systems in which all transactions terminate successfully within a finite number of steps, i.e. ensure local progress. However, Bushkov *et al.* [7] proved that no opaque STM algorithm can achieve this property.

In terms of achieving good performance, the system should additionally guarantee that parallelism is achieved. So, transactions should not be executed sequentially. A pessimistic STM algorithm [24, 25] never aborts any transaction. However, the way most existing pessimistic STM algorithms achieve this is by "pessimistically" imposing a sequential order in the execution of all *update transactions*, i.e. all those transactions that update data items. This significantly restricts parallelism in many cases and therefore it leads to performance degradation.

### 1.3 Contribution

In this thesis, we prove a collection of results about disjoint-access parallel universal constructions, including two new definitions for disjoint-access parallelism, an impossibility result, and two algorithms. We also present two new STM algorithms, namely WFR-TM and SemanticTM, with the goal of improving concurrency, while not sacrificing correctness and progress.

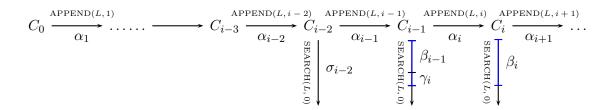

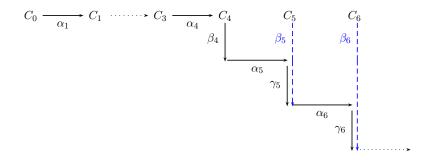

#### 1.3.1 Disjoint-Access Parallelism in Shared-Memory Computing

We prove a collection of positive and negative results. On the negative side, we prove that linearizable universal constructions which ensure both disjoint access parallelism and wait-freedom are not possible; this impossibility result applies to STM algorithms that satisfy local progress. We prove this impossibility result by considering a dynamic data structure that can grow arbitrarily large during an execution. The proof considers a singly-linked unsorted list of integers which supports an operation that appends an element to the end of the list and an operation that searches the list starting from its beginning. It shows that, in any disjoint-access parallel implementation resulting from the application of a universal construction to this data structure, there is an execution of a search that never terminates. For the proof of the impossibility result, we introduce *feeble disjoint-access parallelism*, which is weaker than all existing disjoint-access parallelism definitions. Thus, the impossibility result still holds if we replace the disjoint-access parallelism definition with any existing definition of disjoint-access parallelism. This result relies on a natural assumption about

universal construction, which roughly says that the operations of a concurrent implementation resulting from applying a universal construction to a sequential data structure should simulate its operations.

For data structures of bounded size we present a universal construction, called DAP-UC, that achieves both disjoint-access parallelism and wait-freedom. Specifically, the universal construction is the first that provably ensures both wait-freedom and disjoint-access parallelism for dynamic data structures in which each operation accesses a bounded number of data items. For other dynamic data structures, the universal construction still ensures linearizability and disjoint-access parallelism, but a weaker progress property, know as *lock-freedom*. Lock-freedom guarantees that, in an infinite execution, some (non-faulty) process completes infinitely many operations, even if other processes may fail (by crashing) or are very slow.

Disjoint-access parallelism [27] and the variants of it [11, 9, 26] presented in the literature were originally formalized in the context of fixed size data structures, or when the data items that each operation accesses are known when the operation starts its execution. Dealing with these cases is much simpler than considering an arbitrary dynamic data structure where the set of data items accessed by an operation may depend on the operations that have been previously executed and on the operations that are performed concurrently.

In this thesis, we also study reasonable relaxations of the definition of disjoint-access parallelism. Specifically, we define a variant of disjoint-access parallelism, called timestamp-ignoring disjoint-access parallelism, which is similar to classical disjoint-access parallelism [11] but allows multiple operations to access a timestamp object, even though they operate on disjoint parts of the simulated state. A wait-free timestamp object can be easily implemented with a fetch&increment object or a shared global clock. If the getTimestamp() operation never attempts to modify the timestamp object, for example, when it is implemented from a shared global clock that increments automatically, then timestamp-ignoring disjoint-access parallelism is (in many cases, depending on the formal definition of disjoint-access parallelism) the same as disjoint-access parallelism.

Several examples of algorithms that ensure timestamp-ignoring disjoint-access parallelism can be found in the literature. For instance, several well-known STM algorithms [29, 30, 31] assign timestamps to transactions. Each transaction may then use its timestamp (as well as the timestamps of other transactions) to resolve conflicts and/or determine whether the data items it has read are consistent. If the access to the global timestamp

object is not taken into consideration, some of these algorithms are disjoint access parallel (e.g. [29], [30] and [32]). However, none of these algorithms are wait-free. The definition of timestamp-ignoring disjoint-access parallelism can be motivated by the existence of these algorithms. This definition allows operations operating on different parts of the simulated data structure to proceed in parallel without any interference, except for accesses to the timestamp object.

Finally, we present a new universal construction, called TI-DAP-UC, that ensures wait-freedom and timestamp-ignoring disjoint-access parallelism when applied to any sequential data structure that has a bounded number of entry points; an *entry point* to a data structure is any data item passed as input to an operation on the data structure. For instance, in the linked-list example, the entry points are the pointer to the (first) node from which search starts and the pointer to the (last) node on which append is applied.

#### 1.3.2 New Software Transactional Memory Algorithms

#### 1.3.2.1 WFR-TM

For read-intensive workloads it is really important to ensure that transactions that never update a data item (which are called *read-only* transactions) never abort and are wait-free; i.e. they always commit within a finite number of steps. As a first step towards achieving enhanced parallelism in the STM context, we introduce WFR-TM, an STM algorithm which aims at combining some of the advantages from both optimistic and pessimistic STM, while trying to avoid their drawbacks. Specifically, in WFR-TM read-only transactions are wait-free, and they perform only two writes to shared memory and these writes are to single-writer registers. Additionally, WFR-TM allows multiple *update* transactions (that are not read-only) to execute in parallel. Specifically, update transactions use a pessimistic approach to synchronize with concurrently executed read-only transactions: they wait for such transactions to complete. However, they use an optimistic approach to synchronize with each other: they are executed concurrently in a speculative way, and they commit if they have not encountered any conflict with other update transactions during their execution. Thus, WFR-TM, in contrast to pessimistic STM algorithms, imposes less restrictions on parallelism.

Briefly, in WFR-TM, a read-only transaction  $T_r$  starts by announcing itself. An update transaction  $T_w$  that wants to update a data item x after  $T_r$  is announced (and thus probably after  $T_r$  has read x), does so only after  $T_r$  has committed. So, before  $T_w$  completes, it waits

for all read-only transactions that have been initiated and not yet completed at some point of  $T_w$ 's execution (before  $T_w$  began its waiting phase), to commit. Notice that  $T_w$  may wait a read-only transaction with which it does not conflict. Also, notice that an update transaction waits only for a finite number of read-only transactions. We remark that it is not necessary to know in advance whether a transaction is read-only; any transaction is read-only when it begins and becomes an update transaction the first time it accesses a data item for write. Update transactions in WFR-TM employ fine-grained locking for accessing data items, so that those that do not conflict can commit in parallel. We remark that, in WFR-TM, read-only transactions are able to read a consistent value even for a locked data item, without having to wait for its owner to unlock it. Thus, wait-freedom of read-only transactions is not violated in case an update transaction fails while holding a lock on some data item.

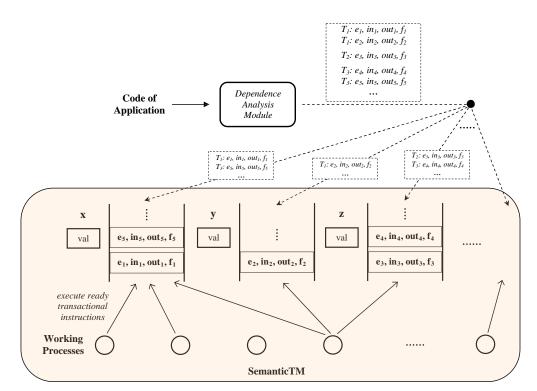

#### 1.3.2.2 SemanticTM

Finally, we introduce SemanticTM, an STM algorithm which achieves fine-grain parallelism at the transactional instruction level. This means that in addition to instructions of different transactions, instructions of the same transaction that do not depend on each other can be executed concurrently. Additionally, for simple transactions and assuming compiler support, SemanticTM ensures that all transactions (both read-only and update) complete within a finite number of steps and never abort, by ensuring that no transactions conflict. Since SemanticTM ensures local-progress, it naturally supports irrevocable operations.

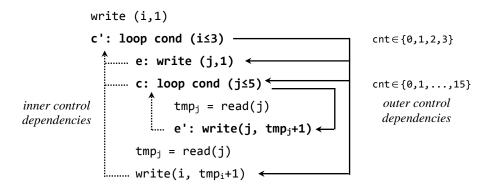

Briefly, SemanticTM employs a list for each data item. The instructions of each transaction are placed in the appropriate lists in FIFO order; specifically, since each instruction is executed on a single data item, it is placed in the list of the data item that it accesses. A set of worker processes execute instructions from the lists, in order. The algorithm is highly fault-tolerant; even if some worker processes fail by crashing, all transactions whose instructions have been placed in the lists will be executed. In this thesis we focus on relatively simple transactions that access a known set of data items, and their codes contain read and write instructions on them, conditionals (i.e. if, else if, and else), loops (i.e. for, while, etc.), and function calls. For such transactions, the work of placing the instructions of the transaction together with their dependencies in lists can be done at compile time (so there is no need to employ a scheduling component for doing so). Despite this fact, for simplicity, we refer to a scheduling process (sometimes called scheduler) which undertakes this task. We briefly discuss, in Section 7.2, how to extend SemanticTM to cope with more

complicated transactional codes.

We remark that several dependencies may exist among the instructions of a single transaction; specifically, a single instruction may have several dependencies. SemanticTM requires these dependencies to be predicted statically. By using compiler support, these dependencies become known before the beginning of the execution of the transactions. SemanticTM stores information about them together with the corresponding instruction in the appropriate list. In Section 6.2.1, we describe the dependencies expected by SemanticTM in order to guarantee the correct execution of the corresponding transactions. It is worth mentioning that in this work, we do not focus on how these dependencies are extracted. SemanticTM can make use of any existing or future work on dataflow analysis. After its placement in the appropriate list, each transactional instruction is executed as soon as its data are available. Thus, SemanticTM can be thought of as a dataflow algorithm in the sense that it mimics, in software, a dataflow architecture.

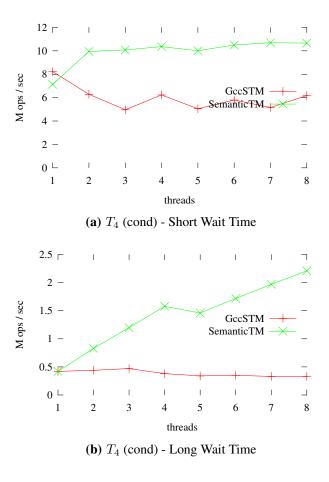

In Section 6.5, we present some experimental results where a simplified version of SemanticTM executes simple static transactions testing different conflict patterns among them. In the experiments, SemanticTM exhibits good performance; specifically, in all these experiments, SemanticTM performs better than GccSTM [33] which is an industry software transactional memory standard.

The current version of SemanticTM does not support dynamic transactions. A discussion on how this limitation could be overcomed is provided in Section 7.2. Since SemanticTM ensures that all transactions will commit, it does not provide any support for explicitly aborting transactions.

### 1.4 Roadmap

In Chapter 2, we present the model of computation, provide several useful definitions for universal constructions and STM algorithms, describe correctness and progress properties, and some variants of disjoint-access parallelism, including the two new definitions introduced. In Chapter 3, we provide a discussion of the related work.

In Chapter 4, we present the results on disjoint-access parallelism. Specifically, the impossibility result is presented in Section 4.2. Then, in Section 4.3, the new universal construction called DAP-UC is presented and in Section 4.4, we formally prove that (for certain classes of data structures) the concurrent data structures that DAP-UC produces are

#### Roadmap

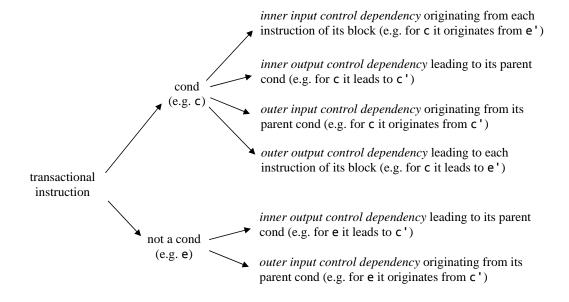

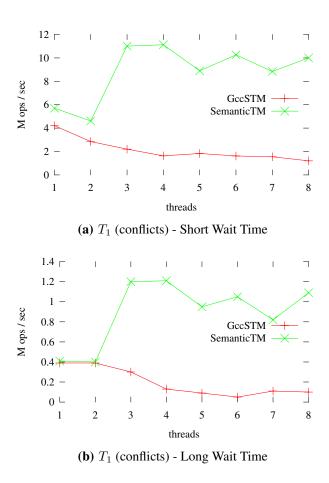

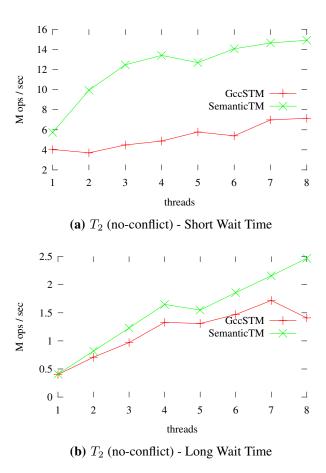

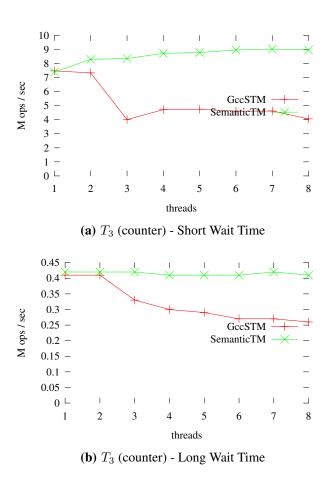

linearizable, wait-free, and disjoint-access parallel. Finally, in Section 4.5, we present an extension of DAP-UC which (for certain classes of data structures) produces linearizable, wait-free, and timestamp-ignoring disjoint-access parallel concurrent data structures.