### UNIVERSITY of CRETE

Physics Department

# Fabrication and analysis of heterostructure field effect transistors based on AlN and InN

A dissertation submitted in fulfillment of the requirements for the degree of

Doctor of Philosophy

by

Christos Zervos

Heraklion, Crete, March 2018

#### Ph. D Dissertation

## Fabrication and analysis of heterostructure field effect transistors based on AlN and InN

by

#### Christos Zervos

Advisory Committee:

Alexandros Georgakilas (Advisor) Professor, Physics Department, University of Crete

*Eleftherios Iliopoulos Associate Professor, Physics Department, University of Crete*

Zekentes Konstantinos Researcher, Institute of Electronic Structure and Laser, FORTH

Examination Committee:

Alexandros Georgakilas (Advisor) Professor, Physics Department, University of Crete

*Eleftherios Iliopoulos Associate Professor, Physics Department, University of Crete*

Konstantinos Zekentes Researcher, Institute of Electronic Structure and Laser, FORTH

Nikos Pelekanos Professor, Department of Materials Science and Technology, University of Crete

Zaharias Hatzopoulos Associate Professor, Physics Department, University of Crete

George Konstantinidis Principal Researcher, Institute of Electronic Structure and Laser, FORTH

*George Deligeorgis Researcher, Institute of Electronic Structure and Laser, FORTH*

#### Abstract

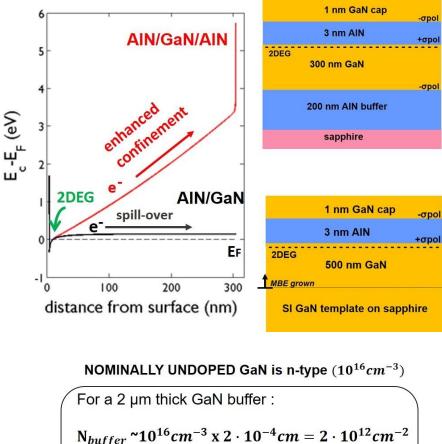

The aim of this thesis was to create new knowledge for material and device processing effects on the performance of novel III-Nitride Heterostructure Field Effect (HFET) transistors using either an AIN barrier or InN channel layers. The AIN/GaN heterojunction offers the highest polarization discontinuity for GaN two-dimensional electron gas (2DEG) channel transistors, and high electron mobility transistor (HEMT) devices can be realized with ultra-shallow channels and very high current density.

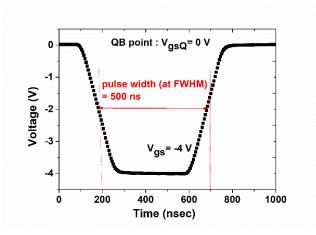

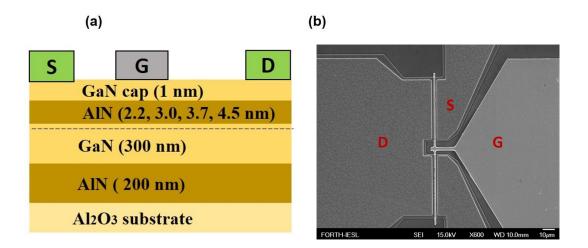

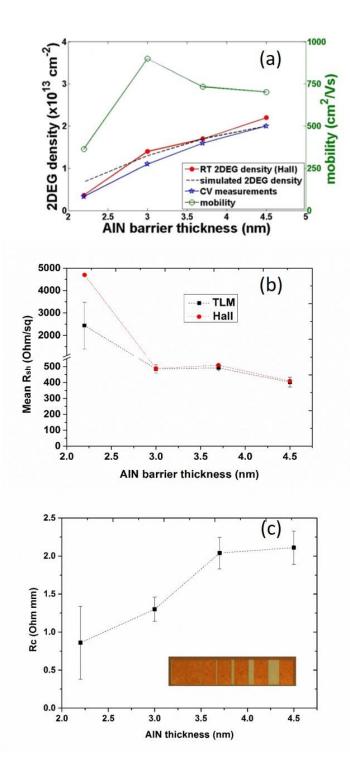

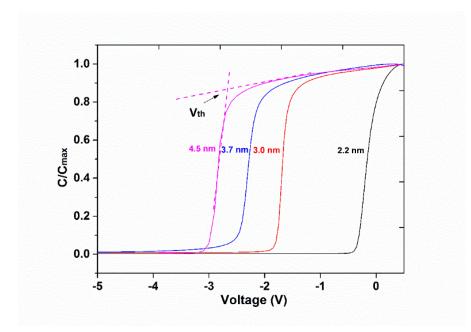

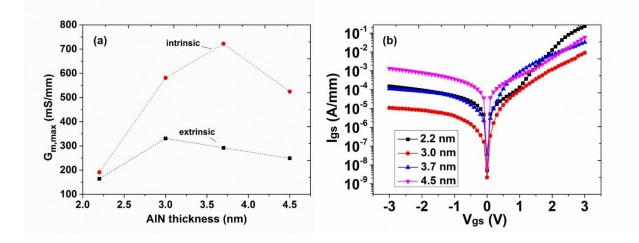

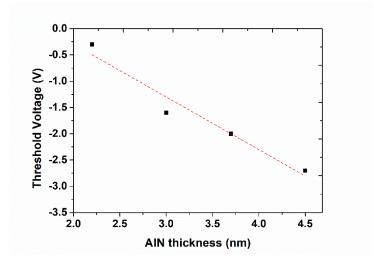

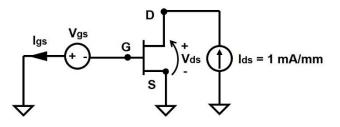

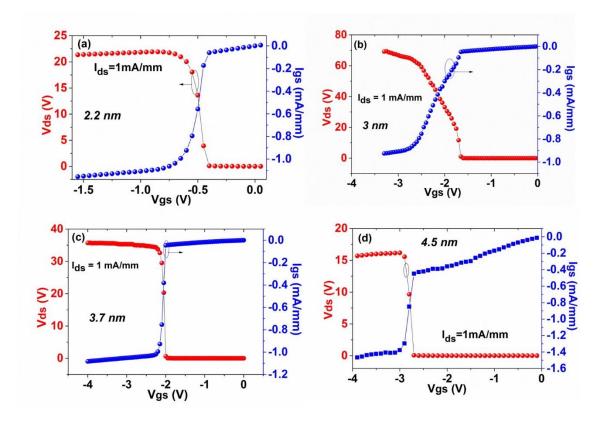

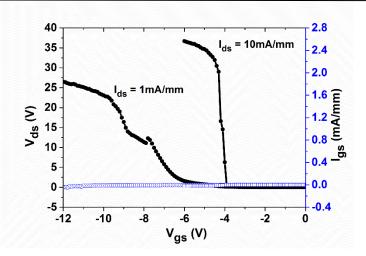

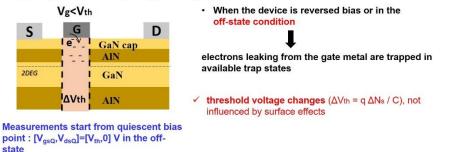

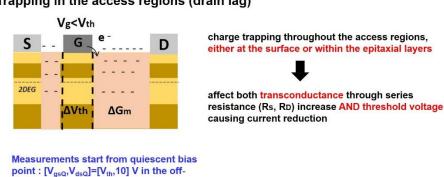

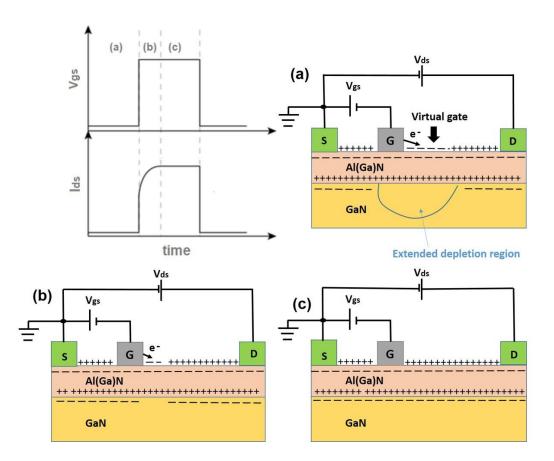

In this work, an extensive study of unpassivated HEMTs (with  $L_{g}\sim 1 \mu m$ ) based on thin double AIN/GaN/AIN heterostructures with 1 nm GaN cap, directly grown on sapphire subtrates by plasma-assisted molecular beam epitaxy (PAMBE) is reported. The analysis is based on dc, pulsed and breakdown measurements, which were carried out on the devices for an AIN top barrier thickness in the range of 2.2-4.5 nm. The 2DEG density (N<sub>s</sub>) varied from 6.8 x  $10^{12}$  to 2.1 x  $10^{13}$ cm<sup>-2</sup> as the AIN barrier thickness increased from 2.2 to 4.5 nm and the maximum dc drain-source current (Ids) was 1.1 A/mm for AIN barrier thickness of 3.0 and 3.7 nm. The 3.0 nm AIN barrier HEMT exhibited the best operation in terms of standard performance metrics such as transconductance and off-state breakdown voltage (Vbr). Moreover, the Vbr of the 3.0 nm AIN barrier HEMT was more than double (70 V) the value measured for a single AIN/GaN HEMT grown on a thick GaN buffer layer, due to improved electron confinement in the 2DEG channel. Pulsed measurements were performed with a 500 ns pulse-width and exhibited a current collapse varied between 6%–12% and 10%–15% under gate and drain lag conditions, respectively. Small positive shifts of threshold voltage (0.2-0.4 V) with negligible reduction of transconductance interpreted to suggest small electron trapping predominantly in the layers and interfaces underneath the Schottky gate contact. These results suggest that the double heterostructures may offer intrinsic advantages for the breakdown and current stability characteristics of high current HEMTs.

AlN/GaN/AlN double heterostructures using a 5-nm-thick GaN quantum well were also tested for transistor normally-off operation. The fabricated devices exhibited very low maximum  $I_{ds}$  currents, ranging between 0.16-0.60 mA/mm, due to very high on-resistances resulting from the

absence of 2DEG across the entire source-drain region. These structures may offer promise well beyond the established power-related applications and could be useful for digital applications.

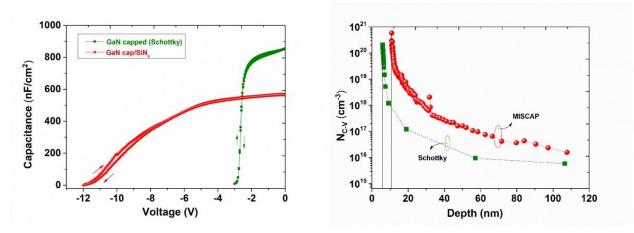

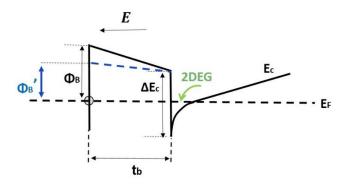

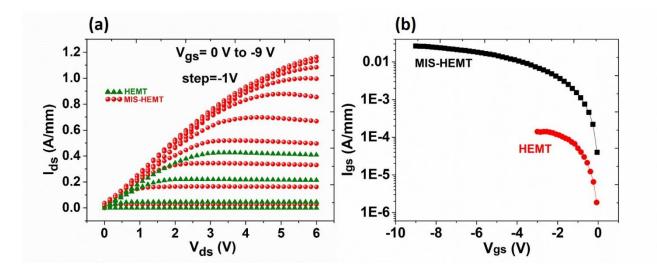

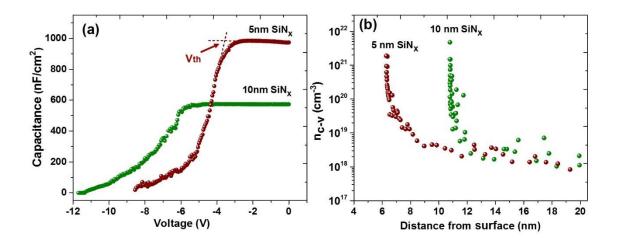

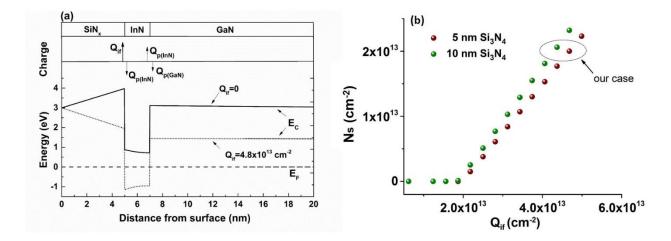

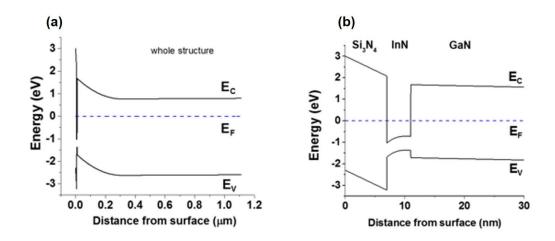

The potential of using in situ SiN<sub>x</sub> deposition by PAMBE on an AlN/GaN/AlN HEMT structure (with 1 nm GaN cap and 3.5 nm AlN top barrier thickness) as a passivation layer and gate dielectric, was also investigated. The 5 nm in situ SiN<sub>x</sub> dielectric resulted in a large increase in N<sub>s</sub>, exhibiting a value of  $3.8 \times 10^{13}$  cm<sup>2</sup>, when compared to a similar structure without SiN<sub>x</sub> cap, in which N<sub>s</sub> was  $1.9 \times 10^{13}$  cm<sup>2</sup>, suggesting the presence of an additional positive charge at the SiN<sub>x</sub>/GaN cap interface. HEMT devices with ~1 µm gate length exhibited drain-source currents directly comparable to the N<sub>s</sub> values, being 1.15 and 0.43 A/mm at V<sub>gs</sub> = 0 V for SiN<sub>x</sub> and Schottky-gate AlN/GaN/AlN HEMTs, respectively. However, the SiN<sub>x</sub>/AlN/GaN/AlN HEMTs exhibited increased gate leakage currents and severe current collapse due to the presence of high interface trap state densities.

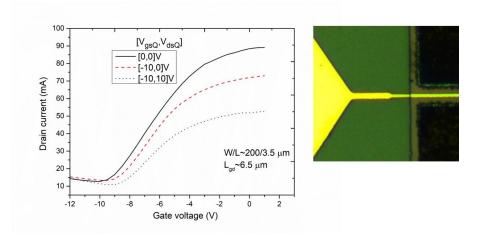

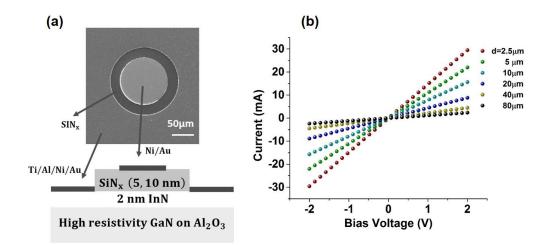

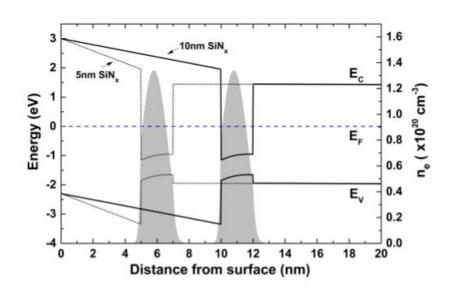

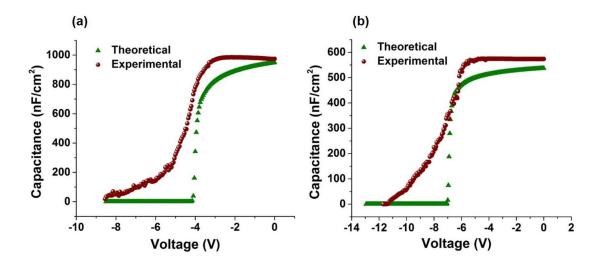

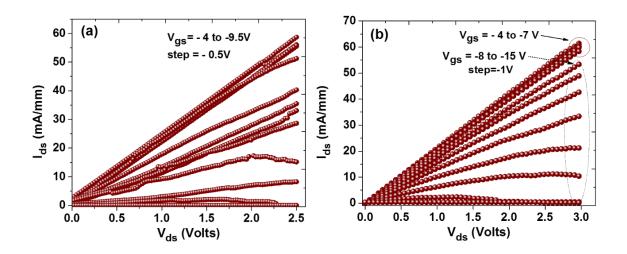

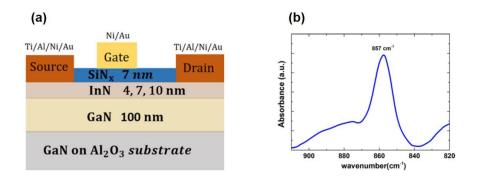

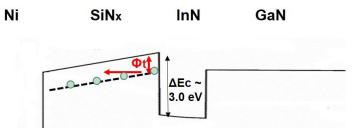

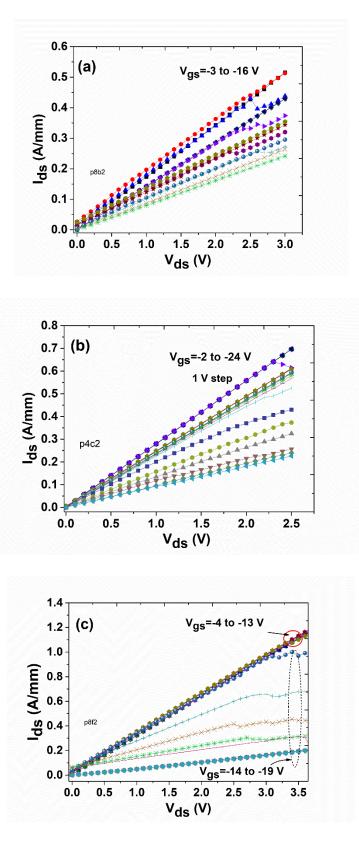

To boost performance over GaN-based devices and pave the way for terahertz frequency electronics, InN as channel material represents the best candidate due to its unique transport properties. SiN<sub>x</sub> deposited in situ in the PAMBE system could effectively modulate the electron concentration and work as a gate dielectric for 2 nm ultrathin InN channel field effect transistors. Operation of InN-on-GaN field effect transistors was demonstrated for the first time exhibiting a maximum  $I_{ds}$  of about 60 mA/mm and a pinch-off voltage of -9.5 V and -15 V for 5 and 10 nm thick SiN<sub>x</sub>, respectively.

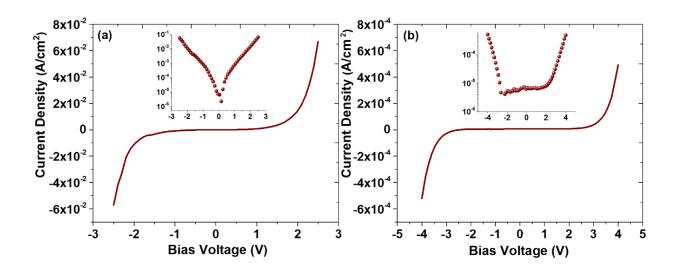

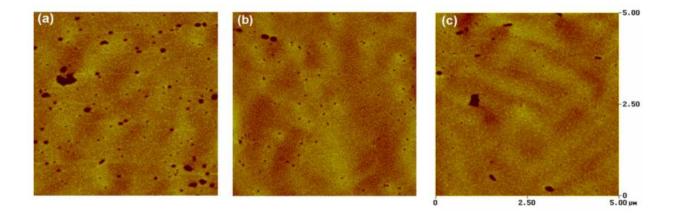

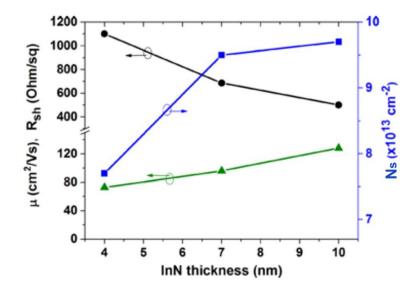

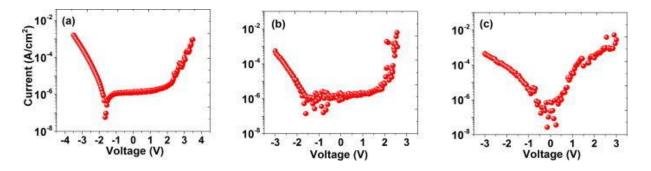

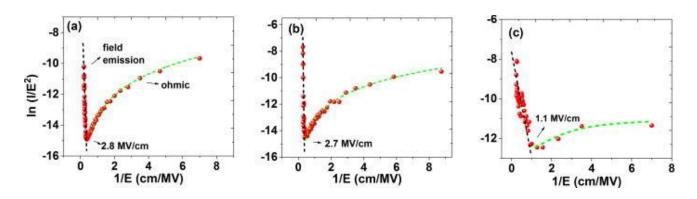

An increase of InN layer thickness, in the 4-10 nm thickness range, could increase significantly  $I_{ds}$  up to 1.2 A/mm, however, the channel could not fully pinch-off. This was attributed to the increased conductivity of the InN layers, caused by the high density of dislocations formed due to the large lattice mismatch between InN and GaN. The charge conduction mechanisms of Ni/SiN<sub>x</sub>/InN metal-insulator-semiconductor capacitors were investigated and I-V analysis suggested ohmic conduction by hopping at low electric fields, while field emission of electrons from trap centers in SiN<sub>x</sub> located 1.1-1.3 eV below the conduction band was prevailed at high electric fields. These results emphasize the use of ultrathin InN layers and the growth optimization of SiN<sub>x</sub> dielectric and SiN<sub>x</sub>/InN interface formation as a prerequisite for the development of InN channel transistors for ultra-high frequency applications.

#### ACKNOWLEDGEMENTS

I would especially like to thank my advisor, Prof. Alexandros Georgakilas, for giving me the opportunity to realize this work in the microelectronics research group of University of Crete and FORTH, as well as for his significant guidance and support during my PhD study.

I am very grateful to all the people in the microelectronics research group for their valuable contribution and assistance during this research project. Adam Adikimenakis for the growth of MBE samples and Thanasis Kostopoulos for his constant support in the clean room activities. Petros Beleniotis, who worked very closely with me during his master's thesis project, was extremely valuable during my research work. He performed a part of theoretical calculations and helped me a lot in the electrical characterization and analysis of a countless number of devices.

I also want to express my gratitude to Antonis Bairamis who carried out band diagram simulations in the first part of this study. Many thanks to Maria Kayambaki for her assistance and technical support in the electrical characterization lab, Katerina Tsagaraki who characterized my samples by SEM and AFM and Maria Androulidaki for FTIR and Raman measurements. I would also like to acknowledge George Stavrinidis for training in the processing lab and George Deligeorgis regarding the rf characterization of devices. I am greatful to friends and colleagues I had the privilege of working with including George Doundoulakis, Stelios Kazazis and Foteini Miziou. I am thankful for their help and support.

Finally, I would like to especially thank Dr. Jan Kuzmik and Milan Tapajna from Slovak Academy of Sciences for all the interesting discussions.

This work was supported partially by the ESPA ARISTEIA program, Project No. 1935: "NITROHEMT" and was co-funded by the European Social Fund (ESF) and National Resources. I am also grateful for the financial support provided by IESL-FORTH until the completion of this research project.

#### **Journal publications**

- <u>Ch. Zervos</u>, A. Adikimenakis, P. Beleniotis, A. Kostopoulos, M. Androulidaki, K. Tsagaraki, M. Kayambaki, G. Konstantinidis, and A. Georgakilas, "Investigation of of thin InN/GaN heterostructures with *in situ* SiN<sub>x</sub> dielectric grown by plasma-assisted molecular beam epitaxy", J. Vac. Sci. Technol. B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena 35, 021210, 2017.

- <u>Ch. Zervos</u>, A. Adikimenakis, P. Beleniotis, A. Kostopoulos, K. Tsagaraki, M. Kayambaki, G. Konstantinidis, and A. Georgakilas, "In-situ SiN<sub>x</sub>/InN structures for InN channel transistors", Appl. Phys. Lett. 108, 142102, 2016.

- <u>Ch. Zervos</u>, A. Adikimenakis, A. Bairamis, A. Kostopoulos, M. Kayambaki, K. Tsagaraki, G. Konstantinidis, and A. Georgakilas, "Analysis of current instabilities of thin AlN/GaN/AlN double heterostructure high electron mobility transistors", Semicond. Sci. Technol. 31, 065002, 2016.

- A. Bairamis, <u>Ch. Zervos</u>, A. Adikimenakis, A. Kostopoulos, M. Kayambaki, K. Tsagaraki, G. Konstantinidis & A. Georgakilas, "Electron density and currents of AlN/GaN high electron mobility transistors with thin GaN/AlN buffer layer", Appl. Phys. Lett. 105, 113508, 2014.

#### **Publications in conference preceedings**

- A. Adikimenakis, <u>Ch. Zervos</u>, P. Beleniotis, A. Kostopoulos, K. Tsagaraki, M. Kayambaki, G. Konstantinidis, and A. Georgakilas, "InN/SiN<sub>x</sub> MIS capacitors and MISFETs grown by Plasma-Assisted MBE", 40<sup>th</sup> Workshop on Compound Semiconductors Devices and Integrated Circuits (WOCSDICE), 6-10 June 2016, Aveiro, Portugal, pp. 45-46.

- <u>Ch. Zervos</u>, A. Bairamis, A. Adikimenakis, A. Kostopoulos, M. Kayambaki, K. Tsagaraki, G. Konstantinidis & A. Georgakilas, "AlN/GaN/AlN double heterostructures with thin AlN top barriers", 10<sup>th</sup> International Conference on Advanced Semiconductor Devices and Microsystems (ASDAM), 20-22 October 2014, Smolenice, Slovakia, pp. 113-116 (IEEE, 2014).

- <u>Ch. Zervos</u>, A. Bairamis, A. Adikimenakis, A. Kostopoulos, M. Kayampaki, K. Tsagaraki,

G. Konstantinidis, and A. Georgakilas, "AlN/GaN HEMTs with thin GaN/AlN buffer

layers on sapphire (0001) substrates", 38<sup>th</sup> Workshop on Compound Semiconductors Devices and Integrated Circuits (WOCSDICE), 15-20 June 2014, Delphi, Greece, pp. 55-56.

#### **Conference presentations**

- <u>Ch. Zervos</u>, A. Adikimenakis, P. Beleniotis, A. Kostopoulos, M. Kayambaki, M. Androulidaki, K. Tsagaraki, G. Konstantinidis, and A. Georgakilas, "InN field-effect transistors with in-situ SiN<sub>x</sub> gate dielectric", European Congress and Exhibition on Advanced Materials and Processes (EUROMAT 2017), 17-22 September 2017, Thessaloniki, Greece.

- A. Georgakilas, A. Adikimenakis, <u>Ch. Zervos</u>, A. Bairamis, K. E. Aretouli, K. Tsagaraki, A. Kostopoulos, A. Stavrinidis, E. Tsikritsaki, E. Iliopoulos, and G. Konstantinidis, "Physics and growth of AlN/GaN HEMT structures on sapphire and diamond substrates", European Materials Research Society (EMRS 2015), 15-18 September 2015, Warsaw, Poland. (invited paper).

- <u>Ch. Zervos</u>, A. Adikimenakis, A. Bairamis, A. Kostopoulos, M. Kayambaki, K. Tsagaraki, G. Konstantinidis, and A. Georgakilas, "Analysis of device characteristics of thin AlN/GaN/AlN HEMTs grown on sapphire substrates", 11<sup>th</sup> International Conference on Nitride Semiconductors (ICNS-11), 30 August – 4 September 2015, Beijing, China.

- A. Bairamis, <u>Ch. Zervos</u>, A. Adikimenakis, A. Kostopoulos, M. Kayampaki, K. Tsagaraki, G. Konstantidis and A. Georgakilas, "Growth and evaluation of thin AlN/GaN/AlN HEMT structures by molecular beam epitaxy", 11th International Conference on Nitride Semiconductors (ICNS-11), 30 August – 4 September 2015, Beijing, China.

- A. Adikimenakis, K. Tsagaraki, A. Bairamis, <u>Ch. Zervos</u>, and A. Georgakilas, "Growth and properties of AlN on sapphire (0001) substrates", 11th International Conference on Nitride Semiconductors (ICNS-11), 30 August – 4 September 2015, Beijing, China.

- <u>Ch. Zervos</u>, A. Bairamis, A. Adikimenakis, A. Kostopoulos, M. Kayampaki, K. Tsagaraki, G. Konstantinidis and A. Georgakilas, "AlN/GaN/AlN double heterostructures with thin AlN top barriers", 10th International Conference on Advanced Semiconductor Devices and Microsystems (ASDAM 2014), Smolenice Castle, Slovakia, 20-22 October, 2014.

- <u>Ch. Zervos</u>, A. Bairamis, A. Adikimenakis A. Kostopoulos, M. Kayampaki, K. Tsagaraki, G. Konstantinidis and A. Georgakilas, "AlN/GaN HEMTs with thin GaN/AlN buffer layers on sapphire (0001) substrates", 38th Workshop on Compound Semiconductor Devices and Integrated Circuits" (WOCSDICE 2014), Delphi, Greece, 15-18 June, 2014.

- <u>Ch. Zervos</u>, A. Adikimenakis, F. Miziou, A. Bairamis, M. Kayambaki, A. Kostopoulos, G. Konstantinidis, and A. Georgakilas, "Effects of Al cap layers and HCl treatment on contacts on AlN/GaN 2DEG heterostructures", International Workshop on Nitride Semiconductors (IWN 2014), Wroclaw, Poland, 24-29 August, 2014.

- A. Bairamis, <u>Ch. Zervos</u>, A. Adikimenakis, A. Kostopoulos, M. Kayambaki, K. Tsagaraki, G. Konstantinidis and A. Georgakilas, "Growth and evaluation of thin AlN/GaN/AlN HEMT structures by Molecular Beam Epitaxy", 30th Panhellenic Conference on Solid-State Physics and Materials Science, Heraklion, Crete, Greece, 21-24 September, 2014.

'On the meridian of time, there is no injustice:

## there is only the poetry of motion creating the illusion of truth and drama'

Henry Miller

## Contents

| CHAPTER 1                                                | 1 |

|----------------------------------------------------------|---|

| Introduction                                             | 1 |

| 1.1 III-Nitride semiconductors                           | 1 |

| 1.2 Scope of this work                                   |   |

| 1.3 Chapter 1 references                                 | 5 |

| CHAPTER 2                                                | 8 |

| Fundamentals of III-Nitrides & Device Characteristics    |   |

| 2.1 Polarization physics and the AIN/GaN heterostructure |   |

| 2.2 AIN/GaN HEMT device characteristics                  |   |

| 2.2.1 Scattering effects and mobility                    |   |

| 2.2.2 Current-voltage relationship of HEMT               |   |

| 2.2.3 Transconductance and parasitic resistance          |   |

| 2.2.4 Breakdown voltage                                  |   |

| 2.2.5 Ohmic and Schottky contacts                        |   |

| 2.3 Metal-Insulator-Semiconductor Capacitors             |   |

| 2.3.1 Ideal MIS Capacitor                                |   |

| 2.3.2 Interface traps                                    |   |

| 2.3.3 Insulator charges                                  |   |

| 2.3.4 Flat-band voltage                                  |   |

| 2.3.5 Charge conduction mechanisms                       |   |

| 2.4 Literature summary for III-nitride HEMTs             |   |

| 2.4.1 Overview of the AIN/GaN heterostructure system     |   |

| 2.4.2 InN-based heterostructures background              |   |

| 2.5 Chapter 2 references                                 |   |

| CHAPTER 3                                                |   |

| Device Processing and Characterization                   |   |

| 3.1 Device fabrication                                   |   |

| 3.1.1 Surface cleaning                                   |   |

| 3.1.2 Mesa isolation                                     |   |

| 3.1.3 Ohmic metallization                                                |     |

|--------------------------------------------------------------------------|-----|

| 3.1.4 Gate metallization                                                 |     |

| 3.2 Electrical characterization methods                                  |     |

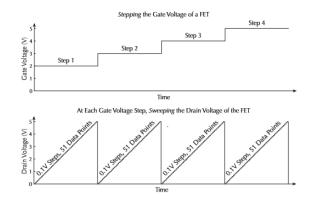

| 3.2.1 DC characterization                                                |     |

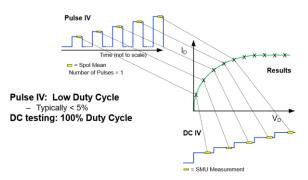

| 3.2.2 Pulsed characterization                                            |     |

| 3.2.3 Capacitance-Voltage characterization                               | 51  |

| 3.3 Chapter 3 references                                                 | 56  |

| CHAPTER 4                                                                | 58  |

| AIN/GaN/AIN HEMTs                                                        | 58  |

| 4.1 Introduction and motivation of the study                             | 58  |

| 4.2 Experimental details                                                 | 61  |

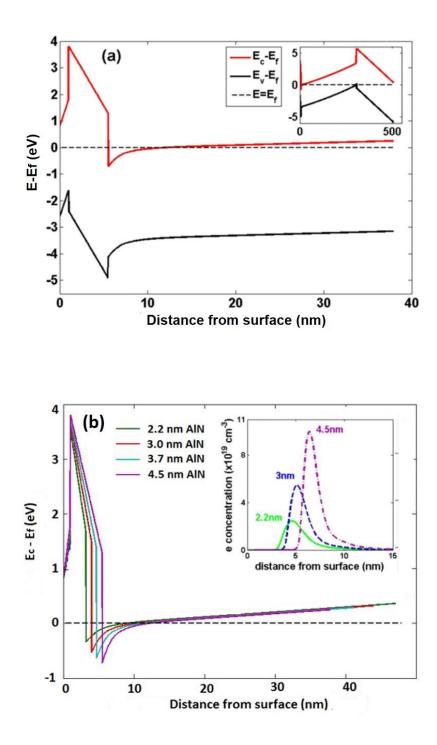

| 4.3 Polarization effects                                                 | 63  |

| 4.4 Electrical properties                                                | 65  |

| 4.5 C-V characterization of Schottky contacts                            | 67  |

| 4.6 DC characterization of AIN/GaN/AIN HEMT transistors                  | 69  |

| 4.7 Pulsed characterization of AIN/GaN/AIN HEMTs and of trapping effects | 76  |

| 4.8 Normally-off approach of AIN/GaN heterostructures                    |     |

| 4.9 AIN/GaN/AIN HEMTs with in-situ deposited $SiN_x$                     |     |

| 4.8 Conclusions                                                          |     |

| 4.9 Chapter 4 references                                                 |     |

| CHAPTER 5                                                                |     |

| InN-based devices                                                        |     |

| 5.1 Introduction to InN                                                  | 107 |

| 5.2 $SiN_x/InN/GaN$ structures with 2 nm ultrathin InN layer             |     |

| 5.3 SiN <sub>x</sub> /InN/GaN structures with $4/7/10$ nm thin InN layer | 116 |

| 5.4 Summary                                                              |     |

| 5.6 Chapter 5 references                                                 |     |

| CHAPTER 6                                                                |     |

| Conclusions                                                              |     |

| 6.1 Summary of the results                                               |     |

| 6.2 Future work                                                          |     |

| 6.3 Chapter 6 references                                                 |     |

#### **CHAPTER 1**

#### Introduction

#### 1.1 III-Nitride semiconductors

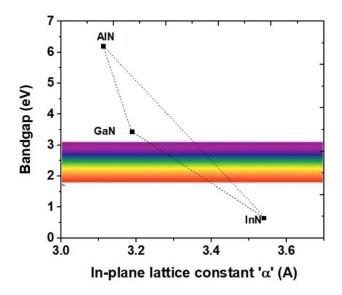

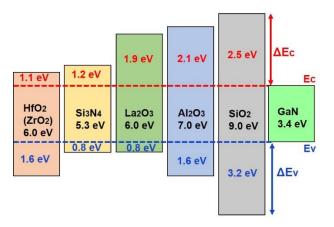

Since the emergence of III-Nitride semiconductors (GaN, AlN, InN) and the first reports of GaNbased field effect transistors in the early 1990s [1,2], the III-Nitride system with direct band gap energies from 0.65 to 6.2 eV, which cover the whole visible spectrum (Fig. 1.1), has attracted an enormous attention by various academic institutions and industrial laboratories for both optical and electronic applications. The large bandgap (except for InN) and the corresponding high breakdown electric fields, excellent transport properties and the high thermal stability are the primary advantages of the nitrides over other semiconductors. They also exhibit spontaneous and piezoelectric polarization along the usual growth axis (the [0001], c-axis), which can result to the formation of a two-dimensional electron gas (2DEG) at the heterointerface of two III-Nitride layers. Thus, 2DEG structures suitable for fabrication of high electron mobility transistors (HEMTs) can be realized, without the introduction of dopants.

Typically, a thin  $Al_xGa_{1-x}N$  layer epitaxially grown on Ga-face (0001) GaN results to a polarization induced 2DEG at the GaN side of the AlGaN/GaN heterointerface, which is used as the channel of GaN HEMTs. The 2DEG density which can reach values in the  $10^{13}$  cm<sup>-2</sup> range, well in excess of those observed in other III-V semiconductor systems, can be modified by changing the thickness of the AlGaN barrier as well as the Al content (AlN mole fraction, x). However, to achieve high frequency operation ultra-scaled devices are needed. This implies a decrease of the metallurgical gate length  $L_g$  as well as a decrease of the barrier thickness  $t_b$  to avoid short channel effects [3-5] restricting the performance of devices. Short channel effects take the form of a degraded drain current modulation by the gate voltage, which causes a negative threshold voltage shift resulting from poor confinement of electrons in the channel [4,5]. Typically, an aspect ratio  $L_g/t_b \ge 5$  is required [4]; for example, for  $L_g = 20$  nm the barrier thickness should be decreased

Figure 1.1. The bandgap versus lattice constant ' $\alpha$ ' plot. The color scale for the visible spectrum corresponds to the bandgap.

to 4 nm to obtain  $L_g/t_b = 5$  and mitigate short channel effects [4]. However, decreasing the AlGaN barrier thickness below 10 nm results in a strong decrease on the 2DEG density [6] causing a poor device performance.

To minimize the Al<sub>x</sub>Ga<sub>1-x</sub>N barrier thickness while achieving a high 2DEG density for GaN HEMTs, an ultrathin AlN barrier is an excellent candidate since the net polarization charge at the interface, and therefore the possible 2DEG density (ranging between  $2 - 6 \times 10^{13} \text{ cm}^2$ ), is the highest that can be achieved for the Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN heterojunction [7]. On the other hand, AlN/GaN heterostructures may exhibit epitaxial growth and fabrication issues due to factors like large tensile strain ~2.4% between the AlN and the underlying GaN layer, strain relaxation and surface sensitivity of AlN [7-13].

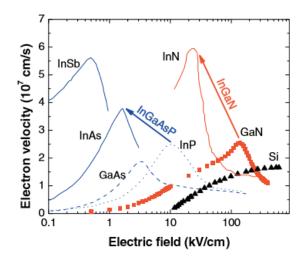

To boost performance over GaN-based devices and pave the way for terahertz frequency electronics, InN as channel material may represent the best candidate due to its unique properties such as small electron effective mass, very high mobility, and high electron peak velocity (~6 x  $10^7$  cm/s) [14,15] (Fig.1.2). However, several challenges need to be addressed before any high-speed/frequency InN channel transistors will be developed. Major impediments are related to (a) high bulk electron concentration in  $10^{18}$ – $10^{19}$ cm<sup>-3</sup> range, (b) Fermi level pinning at the InN surface

Figure 1.2. Electron velocity dependence on the electric field at room temperature in various semiconductors. Image taken from ref. [15].

within the conduction band [16] and formation of a surface electron accumulation layer [16-18], (c) large lattice mismatch (>10%) between InN and either GaN or AlN buffer layers, leading to immediate strain relaxation by introduction of misfit dislocations [19-21], with the accompanying formation of threading dislocations, and (d) electron accumulation at the highly defective epilayer/substrate interfaces [17,18].

#### **1.2 Scope of this work**

Polarization plays an important role in the electrical properties of nitride heterostructures and presents many interesting possibilities for the realization of novel device structures. While the targeted goal of GaN-based transistors is in high-frequency/high power applications, the scope of this work was not to set records in maximum operation frequencies or output power densities. Instead, the objective of this research effort was to identify the effects of epitaxial growth, heterostructure design and device fabrication processes on the operation characteristics of novel HEMT devices, with either AIN barrier or InN channel.

Chapter 2 presents the essential background of the III-Nitride semiconductor system. GaN-based HEMT basic operation is enlightened and brief description of the devices characteristics such as transconductance, breakdown and ohmic/Schottky and MIS contacts is provided. Charge

conduction mechanisms are also discussed. The chapter concludes with a literature summary concerning the Al(Ga)N/GaN system and the InN-based heterostructures background.

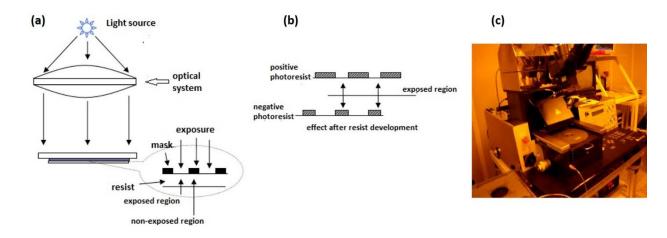

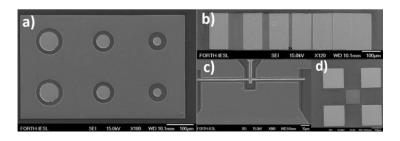

Chapter 3 presents the basic fabrication tools and details regarding the processing steps followed in this work; UV lithography, plasma etching, ohmic and gate metallization. The basic electrical characterization methods (DC and pulsed I-V, C-V) are also presented.

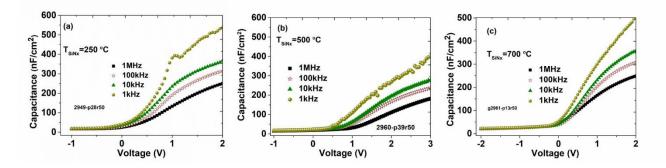

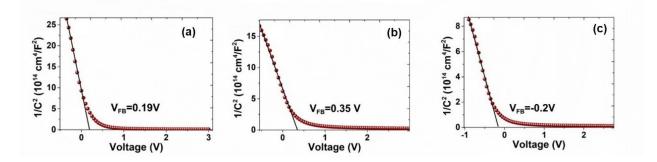

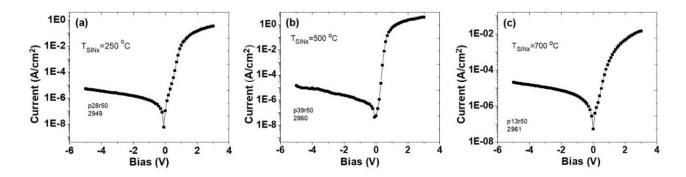

In Chapter 4, the potential of thin double AIN/GaN/AIN HEMT heterostructures (~0.5  $\mu$ m total thickness), with 1 nm GaN cap, and different AIN top barrier thicknesses, directly grown on sapphire substrates by plasma-assisted molecular beam epitaxy (PAMBE), is demonstrated. Dc and pulsed I–V, C-V and electric breakdown measurements were performed in the fabricated devices and the electrical characteristics are analyzed and discussed. AIN/GaN/AIN double heterostructures using a 5-nm-thick GaN quantum well were also tested for transistor normally-off operation. The potential of using in situ SiN<sub>x</sub> deposition on AIN/GaN/AIN HEMT structures, at the end of their growth in the PAMBE reactor, as a passivation layer and gate dielectric, is also investigated. Finally, the electrical characteristics of Ni/SiN<sub>x</sub>/GaN metal-insulator-semiconductor capacitors (MISCAPs) with a SiN<sub>x</sub> dielectric deposited at three different temperatures, 250, 500 and 700 °C, are evaluated.

Chapter 5 focuses on the formation and properties of Ni/SiN<sub>x</sub>/InN MISCAPs and InN MIS-gate field effect transistors (MISFETs). SiN<sub>x</sub> dielectric layers were deposited in-situ in the PAMBE system on the surface of thin InN layers, grown on GaN buffer layers. MISCAPs were fabricated and the C-V and I-V measurements are presented. The capability of MISCAPs to control the electron concentration in the InN layer allowed the successful fabrication and operation of MISFET InN transistors in the case of an ultrathin 2 nm InN layer. To further extend this evaluation, the effect of InN channel thickness is examined and the charge conduction mechanisms are analyzed and discussed for a 4-10 nm InN thickness range.

Chapter 6 concludes the results obtained in this work and provides suggestions for future research.

#### **1.3 Chapter 1 references**

[1] M. Asif Khan, J. N. Kuznia, A. R. Bhattarai, and D. T. Olson. Metal semiconductor field effect transistor based on single crystal GaN. Appl. Phys. Lett. 62, 1786, 1993.

[2] M. Asif Khan, A. Bhattarai, J. N. Kuznia, and D. T. Olson. High electron mobility transistor based on GaN-Al<sub>x</sub>Ga<sub>1-x</sub>N heterojunction. Appl. Phys. Lett. 63, 1214, 1993.

[3] G. H. Jessen, R. C. Fitch, J. K. Gillespie, G. Via, A. Crespo, D. Langley, D. J. Denninghoff, M. Trejo, and E. R. Heller. Short-channel effect limitations on high-frequency operation of AlGaN/GaN HEMTs for T-gate devices. IEEE Trans. Electron Devices 54, 2589, 2007.

[4] K. Shinohara, D. C. Regan, Y. Tang, A. L. Corrion, D. F. Brown, J. C. Wong, J. F. Robinson, H. H. Fung, A. Schmitz, T. C. Oh, S. J. Kim, P. S. Chen, R. G. Nagele, A. D. Margomenos, and M. Micovic. Scaling of GaN HEMTs and schottky diodes for submillimeter-wave MMIC applications. IEEE Trans. Electron Devices 60, 2982, 2013.

[5] M. J. Uren, K. J. Nash, R. S. Balmer, T. Martin, E. Morvan, N. Caillas, S. L. Delage, D. Ducatteau, B. Grimbert, and J. C. De Jaeger. Punch-through in short-channel AlGaN/GaN HFETs. IEEE Trans. Electron Devices 53, 395, 2006.

[6] F. Medjdoub. Ultrathin GaN-on-Silicon devices for millimeter wave applications. Microelectronics Reliability 54, 1, 2014.

[7] Y. Cao and D. Jena. High-mobility window for two-dimensional electron gases at ultrathin AlN/GaN heterojunctions. Appl. Phys. Lett. 90, 182112, 2007.

[8] K. D. Chabak, D. E. Walker, M. R. Johnson, A. Crespo, A. M. Dabiran, D. J. Smith, A. M. Wowchak, S. K. Tetlak, M. Kossler, J. K. Gillespie, R. C. Fitch, and M. Trejo. High-performance AIN/GaN HEMTs on sapphire substrate with an oxidized gate insulator. IEEE Electron Device Lett. 32, 1677, 2006.

[9] A. Adikimenakis, K. E. Aretouli, E. Iliopoulos, A. Kostopoulos, K. Tsagaraki, G. Konstantinidis, and A. Georgakilas. High electron mobility transistors based on the AlN/GaN heterojunction. Microelectron. Eng. 86, 1071, 2009.

5

[10] T. Huang, X. Zhu, K. M. Wong, and K. M. Lau. Low-leakage-current AlN/GaN MOSHFETs using Al<sub>2</sub>O<sub>3</sub> for increased 2DEG. IEEE Electron Device Lett. 32, 212, 2012.

[11] S. Taking, D. MacFarlane, and E. Wasige. AlN/GaN MOS-HEMTs with thermally grown Al<sub>2</sub>O<sub>3</sub> passivation. IEEE Electron Device Lett. 32, 1418, 2011.

[12] A. Bairamis, Ch. Zervos, A. Adikimenakis, A. Kostopoulos, M. Kayambaki, K. Tsagaraki,

G. Konstantinidis & A. Georgakilas. Electron density and currents of AlN/GaN high electron mobility transistors with thin GaN/AlN buffer layer. Appl. Phys. Lett. 105, 113508, 2014.

[13] Ch. Zervos, A. Adikimenakis, A. Bairamis, A. Kostopoulos, M. Kayambaki, K. Tsagaraki, G. Konstantinidis, and A. Georgakilas. Analysis of current instabilities of thin AlN/GaN/AlN double heterostructure high electron mobility transistors. Semicond. Sci. Technol. 31, 065002, 2016.

[14] Ch. Zervos, A. Adikimenakis, P. Beleniotis, A. Kostopoulos, K. Tsagaraki, M. Kayambaki,

G. Konstantinidis, and A. Georgakilas. In-situ SiN<sub>x</sub>/InN structures for InN channel transistors.

Appl. Phys. Lett. 108, 142102, 2016.

[15] T. Palacios. Beyond the AlGaN/GaN HEMT: new concepts for high speed transistors. Phys. Status Solidi A 206, 1145, 2009.

[16] I. Mahboob, T. D. Veal, C. F. McConville, H. Lu, and W. J. Schaff. Intrinsic electron accumulation at clean InN surfaces. Phys. Rev. Lett. 92, 036804, 2004.

[17] H. Lu, W. J. Schaff, L. F. Eastman, and C. E. Stutz. Surface charge accumulation of InN films grown by molecular-beam epitaxy. Appl. Phys. Lett. 82, 1736, 2003.

[18] C. C. Katsidis, A. O. Ajagunna, and A. Georgakilas. Optical characterization of free electron concentration in heteroepitaxial InN layers using Fourier transform infrared spectroscopy and a 2 x 2 transfer matrix algebra. J. Appl. Phys. 113, 073502, 2013.

[19] E. Dimakis, E. Illiopoulos, K. Tsagaraki, Th. Kehagias, Ph. Komninou, and A. Georgakilas.Heteroepitaxial growth of In-face InN on GaN (0001) by plasma-assisted molecular-beam epitaxy.J. Appl. Phys. 97, 113520, 2005.

[20] Th. Kehagias, A. Delimitis, Ph. Komninou, E. Iliopoulos, E. Dimakis, A. Georgakilas, and G. Nouet. Misfit accommodation of compact and columnar InN epilayers grown on Ga-face GaN (0001) by molecular-beam epitaxy. Appl. Phys. Lett. 86, 151905, 2005.

[21] Ch. Zervos, A. Adikimenakis, P. Beleniotis, A. Kostopoulos, M. Androulidaki, K. Tsagaraki, M. Kayambaki, G. Konstantinidis, and A. Georgakilas. Investigation of of thin InN/GaN heterostructures with *in situ* SiN<sub>x</sub> dielectric grown by plasma-assisted molecular beam epitaxy. J. Vac. Sci. Technol. B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena 35, 021210, 2017.

#### CHAPTER 2

#### Fundamentals of III-Nitrides & Device Characteristics

#### 2.1 Polarization physics and the AlN/GaN heterostructure

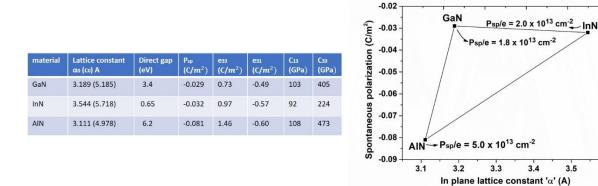

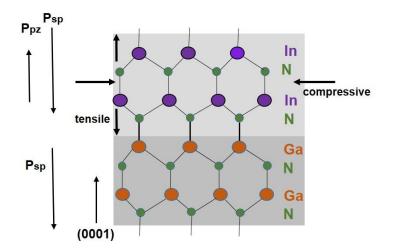

Polarization in the III-Nitride semiconductor system comprises an attractive characteristic for the development of HEMT devices and will be discussed briefly in the following. For an in depth analysis of the polarization physics in III-Nitrides, the reader is cited to the book of C. Wood and D. Jena [1]. Our studies will be confined to metal (Ga, Al or In)-face (0001) structures, meaning that the crystal surface would consist of Ga or Al or In atoms if one cuts the crystal along a plane with vertical bonds. The bonds in all III-V and II-VI semiconductors are polar due to the difference in the ionicity of the constituent atoms. The wurtzite crystal structure characteristic of III-Nitrides results to the existence of a large spontaneous polarization field  $P_{sp}$  aligned along the [0001] direction. The nonzero  $P_{sp}$  exists due to the lower symmetry of the wurtzite crystal structure compared to the cubic zinc-blende structure, for which  $P_{sp}$  vanishes [1]. To obtain an estimation of the magnitude of  $P_{sp}$ , the (spontaneous) polarization induced surface charge densities of relaxed InN, GaN and AlN crystals,  $P_{sp}/e$  (e = -1.602 x 10<sup>-19</sup> C), are ~ 1.99 x 10<sup>13</sup>, 1.81 x 10<sup>13</sup> and 5.05 x 10<sup>13</sup> cm<sup>-2</sup>, respectively (Table 2.1, Fig. 2.1) [2]. These charges are fixed, and are large enough to affect significantly the electrical properties of the material at surfaces and interfaces.

In addition to spontaneous polarization effects, III-Nitrides are also characterized by large piezoelectric coefficients and large values of piezoelectric polarization arise when strain is applied to the crystal. Lateral expansion or contraction of the films' crystal results from the strained epitaxial growth on a substrate with a different lattice constant, and leads to the generation of a piezoelectric polarization field  $P_{pz}$  that can be comparable in magnitude to  $P_{sp}$  [1].  $P_{pz}$  can be calculated from

$$P_{pz} = 2 \frac{a - a_0}{a_0} \left( e_{31} - e_{33} \frac{C_{13}}{C_{33}} \right)$$

(2.1)

where  $\alpha_0$  is the equilibrium in-plane lattice constant,  $\alpha$  is the actual lattice constant (strained),  $e_{31}$  and  $e_{33}$  are the piezoelectric coefficients, and  $C_{13}$ ,  $C_{33}$  are the elastic constants (Table 2.1).

(left) Table 2.1 III-Nitride material properties [1], (right) Fig. 2.1 Predicted spontaneous polarization Psp for GaN, AIN and InN showing the corresponding surface polarization charge densities  $P_{sp}/e$  [1,2].

3.5

3.6

The values of  $C_{13}$ ,  $C_{33}$  and  $e_{33}$  are always positive in wurtzite III-Nitrides, while  $e_{31}$  is always negative. This means that  $(e_{31} - e_{33}C_{13}/C_{33})$  will always be negative. As a result,  $P_{pz}$  in these materials is always negative for layers under tensile strain ( $\alpha > \alpha_0$ ) and positive for layers under compressive strain ( $\alpha < \alpha_0$ ). P<sub>sp</sub> is always negative, which means that the polarization vector points towards the  $[000\overline{1}]$  direction (the substrate), P<sub>sp</sub> and P<sub>pz</sub> are parallel to each other for tensile strain, and in the case of compressive strain the two polarizations are antiparallel [1].

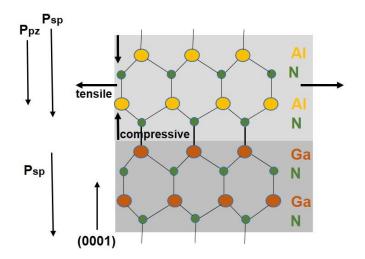

Since most of the material presented in this work will deal with growth on GaN (0001) buffer layers, strain will be referenced to the relaxed lattice of GaN. In the following, the AIN/GaN heterojunction will be discussed for the case of a strained AIN layer grown on top of a strainrelaxed GaN layer, which comprise a significant part of this thesis. In that case, Psp in GaN points in the direction shown in Fig. 2.2 towards the substrate and there is an absence of piezoelectric polarization. The AIN is grown pseudomorphically on GaN and will have an in-plain tensile strain  $\varepsilon_1 = (\alpha_{GaN} - \alpha_{AIN}) / \alpha_{AIN} > 0$  due to its smaller lattice constant  $\alpha$  compared to GaN. This results to a piezoelectric polarization in the AlN layer in addition to the spontaneous polarization. Utilizing the piezoelectric and spontaneous polarization coefficients from ref. [3], for fully strained AIN, the polarization sheet charge at the AlN/GaN interface will be:

Fig. 2.2 Schematic drawing showing polarization fields in Ga-face strained AlN/GaN heterostructures (adapted from *Polarization effects in semiconductors- C. Wood and D. Jena.*, ref. [1]). The lattice mismatch causes a biaxial tensile strain, and the thermal mismatch (caused by the thermal expansion coefficient difference between the substrate and the epitaxial layer) may result a biaxial compressive strain in the growth plane [1].

$$\sigma/e = \Delta P/e = 1/e[(P_{(AIN)} - P_{(GaN)}] = 1/e\{P_{sp(AIN)} + P_{pz(AIN)}\} - (1/e)P_{sp(GaN)} = +6.4 \times 10^{13} / cm^2$$

As a consequence, free electrons will be attracted by the positive bound sheet charge at the AlN/GaN interface, and a 2DEG with a sheet carrier density (N<sub>s</sub>) close to the density of the bound sheet charge can be formed. In real applications, the surface band bending prevents approaching sheet carrier densities as high as  $6.4 \times 10^{13}$  cm<sup>-2</sup> for AlN barrier thicknesses up to ~5 nm, which is the maximum possible thickness without strain relaxation (formation of microcracks) [4].

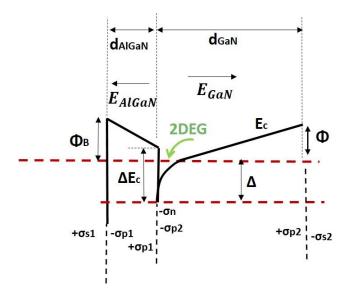

Nowadays it is generally accepted that donor-like surface states play an important role in the formation of the 2DEG. The group of U. K. Mishra in 2000 was the first group to point this out based on a simple electrostatic analysis in an AlGaN/GaN structure [5]. The sum of the various space charges should be zero since the structure as a whole must be charge neutral in the absence of an externally applied field. Following Fig. 2.3, the charge components contained in the structure are (a) the 2DEG electrons with a charge  $\sigma_n=eN_s$ , (b) polarization-induced charges;  $\sigma_{p1}$  is the total (spontaneous plus piezoelectric) polarization charge at the AlGaN edges and  $\sigma_{p2}$  is the polarization

Fig. 2.3 Schematic energy band diagram, shown relative to the Fermi level for the AlGaN/GaN heterostructure where the 2DEG channel of the HEMT can be approximately characterized by a triangular potential well. Charges associated with each interface are also indicated.

charge at the GaN buffer edges, (c) charge  $\sigma_{s1}$  due to ionized surface states, and (d)  $\sigma_{s2}$  is the magnitude of the negative charge at the bottom buffer interface. The polarization-induced charges, by their nature, form a dipole whose net contribution to the total space charge is zero.

If the bottom buffer interface is neglected, since in well-designed field effect transistors the buffer (bulk) charge should be as small as possible, the following charge neutrality equation can be obtained

$$\sigma_{s1} - eN_s = 0 \tag{2.2}$$

The above equation implies that a positive surface charge must exist due to electron transfer from donor-like surface states into empty states in the GaN that are lower in energy [5]. Now considering the conduction band profile (Fig. 2.3), by applying Gauss' law at the heterointerface a relationship between the fields in each layer to the interface charges is given by [6,7]

$$\varepsilon_{\text{GaN}} E_{\text{GaN}} + \varepsilon_{AlGaN} E_{AlGaN} = \sigma_{p1} - \sigma_{p2} - \sigma_n \tag{2.3}$$

where  $\varepsilon_{GaN}$  and  $\varepsilon_{AIGaN}$  are the permittivity of the buffer and barrier respectively, and  $E_{GaN}$ ,  $E_{AIGaN}$  are the electric fields. Similarly, by assuming zero field outside the structure, the positive surface charge  $\sigma_{s1}$  is related to the field in the barrier by [6,7]:

$$-\varepsilon_{AlGaN} E_{AlGaN} = \sigma_{S1} - \sigma_{p1} \tag{2.4}$$

Also, from the equilibrium band diagram of the structure another equation for  $E_{AlGaN}$  can obtained: [1,7]

$$\Phi_B - eE_{AlGaN} d_{AlGaN} - \Delta E_c + \Delta = 0 \tag{2.5}$$

$\Delta$  is the magnitude of the depth of the quantum well in the conduction band below the Fermi level, which is determined by the electron density in the well [6,7],  $\Phi_B$  is the metal/AlGaN Schottky barrier height (or the surface potential),  $\Delta E_c$  is the AlGaN/GaN conduction band offset and  $d_{AlGaN}$ is the thickness of the AlGaN layer.

From Eq. (2.5), the electric field in the barrier is

$$E_{AlGaN} = \frac{\Phi_B - \Delta E_c + \Delta}{ed}$$

(2.6)

The field in the buffer can be approximated by

$$E_{GaN}d_{GaN} = \Phi \tag{2.7}$$

where  $\Phi$  is the potential difference along the buffer layer.

By substituting Eq. (2.6, 2.7) in Eq. (2.3) it is derived that

$$\sigma_n = \sigma_{p1} - \sigma_{p2} - \varepsilon_{AlGaN} \left( \frac{\Phi_B - \Delta E_c + \Delta}{e d_{AlGaN}} \right) - \varepsilon_{GaN} \frac{\Phi}{d_{GaN}}$$

(2.8)

In Eq. (2.8), the last term that corresponds to the depletion term from the buffer can be neglected, since the buffer layer is typically much thicker than the barrier ( $d_{GaN} >> d_{AlGaN}$ ). Taking into account that  $\sigma_n = eN_s$ , Eq. (2.8) results in the widely cited equation reported by Ambacher et al [3]

$$N_{s} = \frac{\sigma_{p1} - \sigma_{p2}}{e} - \frac{\varepsilon_{AlGaN}}{de^{2}} (\Phi_{B} - \Delta E_{c} + \Delta)$$

(2.9)

Thus, from the above discussion it is concluded that  $N_s$  increases with thickness of the AlGaN barrier according to the interplay between Fermi level, occupied surface states, and the AlGaN/GaN conduction band discontinuity.

#### 2.2 AIN/GaN HEMT device characteristics

AlN/GaN HEMTs are excellent candidates for high frequency and high-power switching applications due to the extremely shallow channel with very high electron density and gate capacitance, enabling very high drive current (J=eN<sub>s</sub> $v_e$ ) and transconductance (g<sub>m</sub> ~  $v_{sat}C_{gs}$ ) [8]. The high electron mobility and 2DEG density in these structures yield a high N<sub>s</sub>µ product which contributes to a low on-state resistance R<sub>on</sub> [1]. At the same time, the wide band gap of GaN makes the breakdown voltage of III-nitride based devices generally higher than analogous devices of the same size fabricated with Si or classical III-V semiconductors.

#### 2.2.1 Scattering effects and mobility

In any semiconductors, electrons are accelerated by an electric field and achieve an average velocity determined by the carrier scattering effects [1]. Mobility is a key parameter in the operation of electronic devices used to characterize the microscopic quality of the semiconductor layers. The low field mobility ( $\mu$ ) is defined as the proportionality constant in the average carrier velocity ( $v_d$ ) versus electric field (E) relationship:

$$v_d = \mu E \tag{2.10}$$

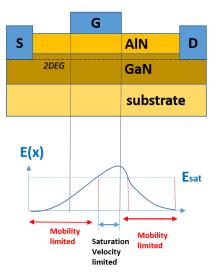

In high electric fields, Eq. 2.10 is invalid since the velocity at a specific lateral electric field within the HEMT channel approaches a constant value known as the saturated drift velocity (Fig. 2.4) [1]. This property arises from various scattering effects within the crystal. When the electric field achieves such a level that scattering prohibits further increase in velocity at higher fields, velocity saturation occurs [1].

Figure 2.4 shows the structure of the AlN/GaN HEMT and the electric field directed along the channel E(x) during typical device operation [1]. The integrated area under the electric field plot equals to the drain-source (symbols: d, s, respectively) applied voltage,  $-\int_{s}^{d} E(x) dx = V_{ds}$  [1]. Since usually the drain contact is biased while the source is grounded, the electric field is non-

Fig. 2.4 AIN/GaN HEMT structure and the electric field along the channel under typical HEMT operation. The integrated area under the electric field plot equals to the drain-source applied voltage,  $-\int_{s}^{d} E(x) dx = V_{ds}$  (adapted from *Polarization effects in semiconductors - C. Wood and D. Jena.*, ref. [1]).

uniform and it peaks at the gate side towards the drain [1]. Under typical device operation, the field in this regime exceeds the field beyond which the electron velocity saturates,  $E_{sat}$  (Fig. 2.4) [1]. Even in this situation, which occurs at high bias conditions, a major fraction of the channel has an electric field lower than the saturationfield, where the electron velocity v(x) is linearly related to the field through the relationship  $v(x) = \mu E(x)$ . The source-access region (the region between source and gate) is an unwanted series resistance which slows the HEMT operation and the resistivity of this region is limited by the N<sub>s</sub>µ product [1]. Therefore, the electrons transport through a part of the channel is always mobility limited, as shown in Fig. 2.4.

A high electron mobility is of great importance for obtaining high speed devices. The AlN/GaN heterostructure, as a binary junction, eliminates disordered alloy scattering [1] which is present in the case of an  $Al_xGa_{1-x}N$  barrier, and therefore greatly benefits the 2DEG low-field mobility [9]. However, a number of scattering mechanisms exists for AlN/GaN HEMTs limiting the conductivity. Coulombic scattering can occur due to charged dislocations and remote (surface) charged states (N<sub>surf</sub> ~ N<sub>s</sub> by charge neutrality) [9]. At room temperature, scattering from polar

optical phonons dominates over all other scattering processes and interface roughness scattering has been found to be dominant at low temperatures [9].

#### 2.2.2 Current-voltage relationship of HEMT

In an AlN/GaN HEMT the electrons flowing between the source and drain ohmic contacts, through the highly conductive 2DEG channel, are controlled by the Schottky gate contact. A schematic drawing of the AlN/GaN HEMT is shown in Fig 2.4. When a voltage  $V_{ds}$  is applied to the drain electrode with the source electrode grounded, a current  $I_{ds}$ , whose magnitude depends on the total resistivity of the 2DEG channel, flows between the two electrodes. The gate electrode, by acting on the 2DEG density below it with the application of voltage  $V_{gs}$ , modulates the channel resistivity and thus  $I_{ds}$ . Typically, the gate is placed asymmetrically and shifted away from the drain side to obtain low source resistance,  $R_s$ , and reduce the peak of the electric field which occurs at the gate end towards the drain at high  $V_{ds}$  values [1], and can have detrimental effects on the devices breakdown characteristics.

Keeping in mind that the drain current  $I_{ds}$  must be constant throughout the channel and if we do not consider any field dependence of  $\mu$ , to simplify analysis for a basic understanding of the current-voltage characteristics,  $I_{ds}$  may expressed by [1]

$$I_{ds} = \sigma_n(x)Wv(x) = \sigma_n(x)WE(x)\mu$$

(2.11)

where x is the direction along the channel,  $\sigma_n(x) = eN_s(x)$  is the 2DEG charge per unit area, v is the velocity, W is the gate width. For long channel transistors (long gate length) and/or for very small V<sub>ds</sub> we can assume that the channel voltage V(x) varies along the channel, from 0 to V<sub>ds</sub>. N<sub>s</sub> is a function of the distance x, along the channel, and thus [1]:

$$\sigma_n(x) = eN_s(x) = \frac{\varepsilon}{d + \Delta d} \{ \left( V_{gs} - V_{th} - V(x) \right) \}$$

(2.12)

where d is the barrier thickness and  $\Delta d$  is the effective distance of the 2DEG from the heterointerface. With the contribution of Eq. 2.12, Eq. 2.11 becomes

$$I_{ds} = \frac{W\varepsilon E(x)\mu}{d+\Delta d} \{ (V_{gs} - V_{th} - V(x)) \}$$

(2.13)

Considering that E(x) = dV(x)/dx Eq. 2.13 is given by [1]

$$I_{ds} = \frac{W\varepsilon\mu}{d+\Delta d} \{ (V_{gs} - V_{th} - V(x)) \} dV(x) / dx$$

(2.14)

By integrating this equation over the gate length  $L_g$ , from the source to the drain, and keeping in mind that V(x=0)=0;  $V(x=L_g)=V_{ds}$  we obtain a relation between  $I_{ds}$  and  $V_{ds}$ :

$$I_{ds} = \frac{W\varepsilon\mu}{L_g(d+\Delta d)} \left[ (V_{gs} - V_{th}) V_{ds} - \frac{V_{ds}^2}{2} \right] = \beta_d \left[ V_{geff} V_{ds} - \frac{V_{ds}^2}{2} \right]$$

(2.15)

where  $V_{geff} = V_{gs} - V_{th}$  and  $\beta_d = \frac{\mu W\varepsilon}{L_g d}$

In a field effect transistor,  $V_{ds}$  produces a lateral field. The current saturates when  $V_{ds}$  is increased to the point where the field in the channel exceeds its critical value thereby causing the velocity to saturate [1]. In the saturation region the drain current is given by:

$$I_{dss} = eWv_{sat}N_s = \frac{\varepsilon Wv_{sat}}{d + \Delta d} (V_{gs} - V_{th} - V_{dss}) = \beta_d V_0 (V_{geff} - V_{dss})$$

(2.16)

where  $V_{dss}$  is the saturation drain voltage,  $I_{dss}$  is the saturation current,  $V_0 = v_{sat} L_g/\mu$ , and  $v_{sat}$  the saturation velocity. For AlGa/GaN devices  $\Delta d$  can be neglected because the maximum of the 2DEG is typically 2-4 nm from the interface, which is smaller than the thickness of the barrier layer, typically greater than 20 nm [1]. However, this is not valid in the case of AlN/GaN HEMTs. The above analysis is known as the two-piece model, implying that an abrupt transition occurs from the constant mobility region to the constant velocity region [1], where  $\mu$  assumed to be constant and independent of the electric field E. At high electric fields, carriers fail to follow this model due to the velocity saturation effect [1]. A more precise analysis of the HEMT operation can be obtained if a smoother transition is assumed allowing the use of a phenomenological velocity-field relationship. In this approach, the peak in the velocity-field plot is neglected and Si-like velocity-field characteristics are assumed [1]. In that case:

$$v = \frac{\mu E(x)}{1 + \mu E(x)/v_{sat}} = \frac{\mu E(x)}{1 + E(x)/E_c}$$

(2.17)

where  $\mu$  the low field mobility and  $E_c = v_{sat}/\mu$  is the electric field in the saturation point.

By using:

$$I_{ds} = \frac{W\varepsilon v(x)}{d} \left( V_g - V_{th} - V(x) \right)$$

(2.18)

and by substituting Eq. 2.17 in Eq. 2.18:

$$I_{ds} = \frac{W \varepsilon \mu v_{sat}}{d} \left[ \frac{\frac{dV(x)}{dx}}{v_{sat} + \frac{\mu dV(x)}{dx}} \{ V_g - V_{th} - V(x) \} \right]$$

(2.19)

By integrating Eq. 2.19 from the source end (x=0) of the channel to the drain end (x=L):

$$I_{ds} = \frac{W \varepsilon \mu v_{sat}}{d} \left[ \frac{V_{geff} V_{ds} - \frac{V_{ds}^2}{2}}{v_{sat} L_g + \mu V_{ds}} \right] = \frac{1}{1 + \frac{\mu V_{ds}}{v_{sat} L_g}} \left\{ \frac{\mu W}{L_g} \frac{\varepsilon}{d} \left[ (V_g - V_{th}) V_{ds} - \frac{V_{ds}^2}{2} \right] \right\}$$

(2.20)

It can be noticed that for large values of  $L_g$  or small values of  $V_{ds}$  or when the saturation velocity approaches infinity, Eq. 2.20 is simplified to Eq. 2.15 which is valid when the mobility is constant and for long channel transistors ( $L_g>1$  µm). For short channel devices (small gate lengths) the current is smaller than what would be expected due to the velocity saturation effect.

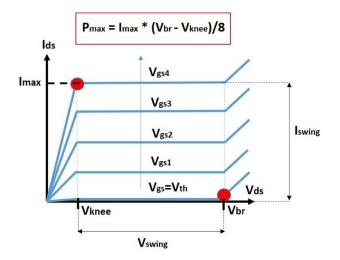

When the transistor operates as an amplifier, an estimation of the maximum power density can be obtained through the relationship [1]  $P_{max} = I_{max} * (V_{br} - V_{knee})/8$ , where  $V_{br}$  is the breakdown voltage and  $I_{max}$  and  $V_{knee}$  are the maximum current density and the knee voltage values, respectively, based on the values measured at DC (Fig. 2.5). Thus, a high power density is obtained if  $V_{br}$  is high and if the on-resistance is minimized in order to have a low  $V_{knee}$  value. It is noted that a high  $N_s$  value is also desirable because it translates to a high  $I_{max}$ .

Fig. 2.5 Schematic of  $I_{ds}$ - $V_{ds}$  characteristics of a HEMT with basic parameters defined in the graph. The maximum output current  $I_{max}$ , the knee voltage  $V_{knee}$  and the breakdown voltage  $V_{br}$  may be used to estimate the maximum output power  $P_{max}$  when the transistor operates as an amplifier.

#### 2.2.3 Transconductance and parasitic resistance

The transconductance is an important parameter in HEMTs and is defined by  $g_m = \partial I_{ds} / \partial V_{gs}$  at a fixed value of  $V_{ds}$ . The extrinsic (measured)  $g_{m(ext)}$  is always smaller than the intrinsic transonductance  $g_{m(int)}$  due to the effect of source series resistance [10] as explained in the following. Suppose that the HEMT has a parasitic source-drain series resistance  $R_{sd}=R_s+R_d$  where  $R_s = R_c + R_{s(a)}, R_d = R_c + R_{d(a)}, R_c$  is the contact resistance of the source/drain electrode and  $R_{s(a)}$ ,  $R_{d(a)}$  are the access resistances of the gate-to-source and gate-to-drain channel regions, respectively. The differential of the drain-source current  $dI_{ds}$  is given by [10]

$$dI_{ds} = \left(\frac{\partial I_{ds}}{\partial V'_{gs}}\right)|_{V'_{ds}} dV'_{gs} + \left(\frac{\partial I_{ds}}{\partial V'_{ds}}\right)|_{V'_{gs}} dV'_{ds} = g_{m(int)} dV'_{gs} + g_{d(int)} dV'_{ds}$$

(2.21)

where  $g_{d(int)} = \frac{\partial I_{ds}}{\partial V'_{ds}}$  is by definition the intrinsic drain conductance and  $V'_{gs}$ ,  $V'_{ds}$  are the internal effective voltages:

$$V'_{ds} = V_{ds} - R_{sd} I_{ds}$$

(2.22)

$$V_{gs}' = V_{gs} - R_s I_{ds} (2.23)$$

At constant V<sub>ds</sub> (i.e., dV<sub>ds</sub>=0)

$$dV'_{ds} = -R_{sd}dI_{ds} aga{2.24}$$

$$dV_{gs}' = dV_{gs} - R_s dI_{ds} aga{2.25}$$

By substituting Eqs. (2.24) and (2.25) into Eq. (2.21)

$$g_{m(int)} = \frac{(1 + R_{sd}g_{d(int)})g_{m(ext)}}{1 - R_{s}g_{m(ext)}}$$

(2.26)

where the extrinsic (measured) transconductance is

$$g_{m(ext)} = \left(\frac{\partial I_{ds}}{\partial V_{gs}}\right)|_{V_{ds}}$$

Similarly, it can be shown [10] that

$$g_{d(int)} = \frac{(1 + R_s g_{m(int)}) g_{d(ext)}}{1 - R_{sd} g_{d(ext)}}$$

(2.27)

where  $g_{d(ext)} = \left(\frac{\partial I_{ds}}{\partial V_{ds}}\right)|_{V_{gs}}$  is the measured (extrinsic) drain conductance.

When the measured drain conductance  $g_{d(ext)}$  becomes zero (in saturation), Eq. (2.26) yields

$$g_{m(int)} = \frac{g_{m(ext)}}{1 - R_s g_{m(ext)}}$$

(2.28)

Typically, in GaN-based devices  $R_c >> R_{a(s)}$  [11] which means  $R_s \approx R_c$ . This approximation has a higher validity in AlN/GaN HEMTs due to the very low sheet resistances and high contact resistances in these devices [11]. Moreover,  $g_{m(ext)}$  can be expressed as follows [11]

$$g_{m(ext)} = \frac{\partial I_{ds}}{\partial V_{gs}} = \frac{\partial}{\partial V_{gs}} (eN_s v) = e \left( v \frac{\partial N_s}{\partial V_{gs}} + N_s \frac{\partial v}{\partial V_{gs}} \right)$$

(2.29)

By taking into account that  $\sigma_n = eN_s = C_gV$  it can be obtained that  $e\partial N_s/\partial V = C_g$ , where  $C_g$  is the "intrinsic" gate capacitance. Therefore, in the velocity saturation region, the transconductance is directly proportional to the gate capacitance and is given by:

$$g_m = ev_{sat} \frac{\partial N_s}{\partial V_{gs}} = ev_{sat} C_g$$

(2.30)

Transconductance has a strong dependence on the gate voltage, as will be demonstrated in chapter 4. It has been proposed that the non-linear increase in the differential source access resistance (defined as  $dV_{gs}/I_{ds}$ ) is the cause for the decrease in transconductance with increase in drain current (or equivalently, when increasing the gate voltage) [12]. Palacios et al. [12] showed, by simulating the electric field in the source access region for different gate voltages, that an early or "quasi-saturation" occurs in nitride-based structures that causes a reduction in the electron mobility which translates into an increase in the differential access resistance [12]. The origin for the quasi-saturation in the electron velocity profile is generally related to the high optical phonon energy in nitride-based semiconductors, which is much lower in other semiconductors, like Si or GaAs, and this early saturation cannot be distinguished from the standard saturation [12].

#### 2.2.4 Breakdown voltage

Many different physical effects are limiting the power performance of GaN-based HEMTs. The most important GaN-related breakdown mechanisms have been discussed in detail in the book of F. Medjdoub and K. Iniewski [13]. The breakdown voltage of GaN devices is usually defined as the voltage level at which the drain current of pinched-off transistors exceeds a normalized value of 1mA per millimeter of device width [13]. V<sub>br</sub> depends on many parameters, such as the epitaxial design of the buffer layer, its material quality and the lateral geometrical design of the devices. Specifically, short gate lengths and short gate-drain distances reduce V<sub>br</sub> as a consequence of the increase of the peak electric field at the drain side of the gate [13]. Thus, transistors designed for operation at high frequencies (which require short gate lengths) can reach lower power densities when compared to the ones operating at lower frequencies [13]. Usually, the maximum operation voltage is limited by excessive gate or drain leakage currents, which may origin from several technological issues. Leakage current originating from the gate usually concerns leakage through the Al(Ga)N barrier [13,14], strain-induced leakage [13,15] and/or surface leakage, which may be

Fig. 2.6 Energy-band diagrams of metal-semiconductor contact for n-type semiconductor, for the case  $\Phi_M < \Phi_S$  where an ohmic contact is formed. (a) corresponds to separate metal and semiconductor, while (b) gives the thermal equilibrium energy band diagram.

introduced when a passivation layer is adopted to alleviate the surface-state-induced current collapse problem [13,16]. The punch-through short channel effect [13,17] can substantially increase subthreshold leakage current. In this case, even at low drain voltages and closed-channel conditions, electrons are bypassing the gate control region via the buffer [13,17,18]. In standard GaN devices, where a GaN buffer layer is adopted, there is an insufficient confinement to the bottom side which may give rise to this punch-through phenomenon. If high leakage paths are suppressed through proper technological advancements, the breakdown voltage of GaN-based HEMTs scales with increasing gate to drain distance,  $d_{gd}$  [13]. Therefore,  $d_{gd}$  defines the highest HEMT voltage operation.

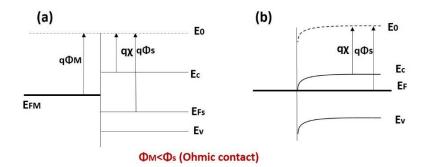

#### 2.2.5 Ohmic and Schottky contacts

#### a) Ohmic contacts

By definition, an ohmic contact is defined as a metal-semiconductor contact that has a negligible junction resistance relative to the total resistance of the semiconductor device [19]. The work function  $\Phi$  of a crystal is defined as the energy required to remove an electron from the Fermi level to the vacuum level E<sub>0</sub>, respectively. In the case of n-type semiconductor, and for an ideal ohmic contact, the work function of the semiconductor should be greater than the work function of the metal ( $\Phi_S > \Phi_M$ ) (Fig. 2.6).

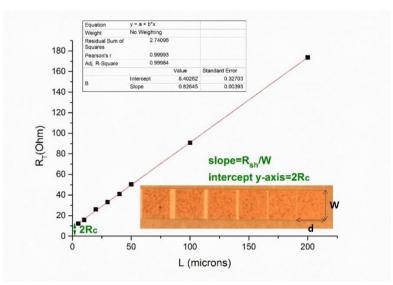

Fig. 2.7 Total resistance R<sub>T</sub> plot with TLM pad spacing for an AlN/GaN HEMT structure. Inset shows an optical microscope image of a TLM pattern.

The transmission line model (TLM) method is commonly used to assess the quality of the ohmic contacts, as well as the electrical properties of the structure [20]. An optical microscope image of a TLM test pattern is shown in the inset of Fig. 2.7. It consists of rectangular metal contact pads with increasing spacing between them, L, while W is the contact pad width, d is the contact pad length. The total resistance,  $R_T$ , is given by [20]

$$R_{T} = \frac{2R_{sh1}L_{T}}{W} + R_{sh2}\frac{L}{W} = 2R_{c} + R_{sh2}\frac{L}{W}$$

(2.31)

where  $R_c$  is the contact resistance,  $R_{sh1}$  and  $R_{sh2}$  the semiconductor sheet resistance under the contact pads and between the contact pads, respectively, and  $L_T$  is the transfer length which refers to the distance across which most of the current transfers into the contact pads from the semiconductor and vice versa [20]. By the assumption that the deposition of the metal does not change the sheet resistance of the semiconductor:  $R_{sh1}=R_{sh2}=R_{sh}$ , Eq. 2.31 becomes

$$R_{T} = \frac{2R_{sh}L_{T}}{W} + R_{sh}\frac{L}{W} = 2R_{c} + R_{sh}\frac{L}{W}$$

(2.32)

where  $R_c = R_{sh}L_T/W$ . By plotting  $R_T$  as a function of L, a linear fit to the data can be obtained as shown in Fig. 2.7. The slope of the line gives the value of  $R_{sh}/W$  and the intercept with y-axis gives the value of  $2R_c$ . It should be noted that the value of  $R_c$  is independent of the contact length d, and only depends on its width i.e. only on the dimension perpendicular to the current flow. In order to normalize the contact resistance, the value of  $R_c$  is multiplied with W to obtain a value in Ohm.mm.

As far as it concerns the contact metal scheme in Al(Ga)N/GaN structures, the most popular metallization is based on the Ti/Al/Ni/Au system [21-23]. The first explanation for the formation of ohmic contact on Al(Ga)N or GaN by annealing a Ti/Al/Ni/Au metallization is based on the formation of a TiN alloy at the interface, which leaves in the III-Nitride an excess of N-vacancies that provide a highly n-doped region underneath the metal contact [21-23]. Al reacts with Ti and forms an Al<sub>3</sub>Ti layer that prevents oxidation of the underlying Ti metal [23] and helps in contact formation. It also reacts with the semiconductor to form AlN, resulting in N vacancies, which contribute to the increase of n-type doping in the underlying semiconductor, enabling electrons to tunnel easily to the 2DEG [24].

The second explanation of ohmic contact formation with Ti/Al/Ni/Au deposition approaches the subject from the standpoint of differences in work functions between the metal and semiconductor [21]. Taking into account that the work function of GaN is 4.1 eV, very close to that of Al, the Al-containing contacts should be ohmic due to the low barrier between the two materials. Researchers in the recent years, supported the first explanation since cross sectional TEM has shown the formation of TiN alloyed layers and spiking at the contact-semiconductor annealed interface [25, 26].

Ni (or Pt, Ti, Mo) is used to avoid the Au indiffusion and the Al outdiffusion and the intermixing between Al and Au, and Au is used to protect from oxidation the Ti and Al metals during high annealing temperatures and to improve the ohmic contacts conductivity [27].

While the metallization combination is important, another issue in ohmic contact formation is the thickness of the AIN barrier the metal stack should penetrate during annealing. In Ga-polar III-Nitrides the thickness of the barrier is proportional to the 2DEG density. This means that the barrier must be thick enough to create the 2DEG, and on the other hand at the same time the barrier should be thin enough for sufficient metal diffusion to occur at high annealing temperatures to contact the

Fig. 2.8 Energy-band diagrams of metal-semiconductor contact for n-type semiconductor, for the case  $\Phi_M > \Phi_S$  where a Schottky contact is formed. (a) corresponds to separate metal and semiconductor, while (b) gives the thermal equilibrium energy band diagram.

2DEG [11]. In the case of AlN, the barrier is much thinner than AlGaN but it also has a much wider bandgap (stronger atomic bonds) making the anneal-diffusion of the contact metals a more difficult case.

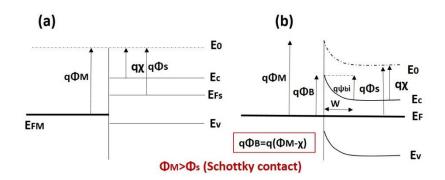

#### b) Schottky contacts

The Schottky contact, the gate electrode in HEMT, is formed when a metal with work function greater than the semiconductor  $(\Phi_M > \Phi_S)$  contacts the respective semiconductor as shown in Fig. 2.8. Unlike the case of ohmic contacts, the gate metals are not annealed in order to form the barrier. Under equilibrium, a barrier height,  $\Phi_B=\Phi_M$ -X, according to the ideal theory, forms for electrons to flow from metal to semiconductor. Thus, the barrier height depends both on the metal work function as well as on the electron affinity X of the semiconductor. A high  $\Phi_B$  associated with a low reverse leakage current is an essential condition for high power radio frequency applications. The commonly used metal combination for Schottky contacts in Al(Ga)N/GaN HEMTs is a Ni/Au metal stack due to the highest work function (~5.15 eV) compared to other metals. The electron affinity, X, of Al<sub>x</sub>Ga<sub>1-x</sub>N decreases with increasing Al content (mole fraction x) [28]. Therefore, the barrier height of a metal on (Al)GaN should increase with increasing Al content of the barrier layer. However, the Schottky barrier in III-Nitrides, as it is usually for many semiconductors, is mainly defined by Fermi level pinning, the barrier height is given by  $\Phi_B=S(\Phi_M - \Phi_s) + (\Phi_s - X)$ , where

S is the pinning factor (0<S<1) and  $\Phi_s$  is the pinning energy at the semiconductor surface in reference to the vacuum level [29]. S=0 describes the case of strong pinning, while S=1 denotes the absence of pinning. The Fermi level pinning typically results in a fixed  $\Phi_B$ , independent of the used gate metal.

The low conductivity of AlN layers and the formation of 2DEG complicates the analysis of I-V measurements for the extraction of Schottky barrier height on AlN. In AlN/GaN structures the analysis of the I-V curve is inadequate since the leakage current consists not only of thermionic emission current but also of tunneling and/or other residual leakage currents [29,30]. Up to now, there are no reports on measured Schottky barrier heights of AlN/GaN structures. A surface potential (or surface barrier height, given by the position of the surface Fermi level, relatively to the conduction band minimum) of ~1.9 eV, independent of the AlN barrier layer thickness, has been reported [30] which is an evidence of Fermi level pinning; however, the Schottky barrier may be different than the barrier on the free AlN surface [30]. Non-published experimental results in our lab for Al-rich AlGaN and InAlN compounds suggest a Schottky barrier height close to 3.0 eV. This barrier height has been assumed in charge control modeling of the AlN/GaN HEMT structures by self-consistent solution of the Poisson and Schrodinger equations and resulted to a good agreement with the experimental measured N<sub>s</sub> of the 2DEG.

#### 2.3 Metal-Insulator-Semiconductor Capacitors

A brief analysis on the characteristics and operation of the metal-insulator-semiconductor capacitor (MISCAP), for an ideal n-type semiconductor ( $n\approx N_d$ ,  $N_d$  is the doping carrier concentration), will be followed, which is the most useful device in the study of semiconductor surfaces. A comprehensive and in-depth analysis of the MOS capacitor can be found in many well respected texts [19,31,32].

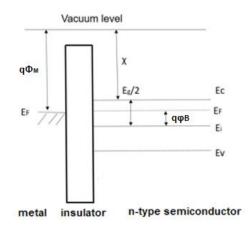

#### 2.3.1 Ideal MIS Capacitor

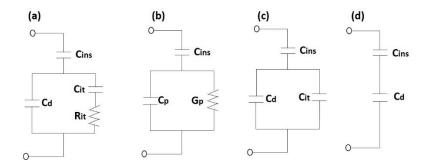

The ideal MISCAP is shown in Fig. 2.9 and has the following characteristics [19]: (a) The only charges that are present in the structure under any applied bias are those in the semiconductor and those on the metal surface adjacent to the insulator, with an equal but opposite sign; this means that it is assumed that no interface trap nor any kind of oxide charge exists; (b) When a dc bias is

Fig. 2.9 Energy-band diagram of ideal MIS capacitor at equilibrium (V= 0) for n-type semiconductor. The difference between the metal work function  $\Phi_M$  and the semiconductor work function was assumed to be zero ( $\Phi_{MS}=0$ ). Adapted from *Physics of semiconductor devices - S.M. Sze* (ref. [19]).

applied, there is no carrier transport through the insulator or the resistivity of the insulator is infinite. The difference between  $\Phi_M$  and the semiconductor work function  $\Phi_{MS}$  (or ideal flat band voltage V<sub>FB</sub>) is given by [19] (Fig. 2.9):

$$\Phi_{MS} = \Phi_M - \left(X + \frac{E_G}{2q} - \varphi_B\right) = \Phi_M - \left[X + \left(\frac{E_C - E_F}{q}\right)\right]$$

(2.33)

where  $\varphi_B$  is the bulk potential given by [19]

$$\mathbf{E}_{\mathbf{F}} - \mathbf{E}_{\mathbf{i}} = k \operatorname{Tln}(\mathbf{N}_{\mathbf{d}}/\mathbf{n}_{\mathbf{i}}) = \mathbf{q} \boldsymbol{\varphi}_{\mathbf{B}} \tag{2.34}$$

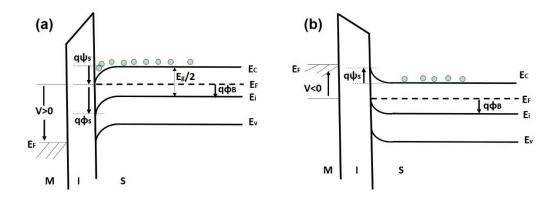

$n_i$  is the semiconductor intrinsic carrier concentration (for GaN  $n_i=2 \times 10^{-10} \text{ cm}^{-3}$ ).  $E_i$  is the intrinsic Fermi level which is always parallel to both  $E_c$  and  $E_v$ , everywhere in the semiconductor. Now, if a positive voltage (V > 0) is applied to the metal plate, the conduction-band edge  $E_c$ , bends downwards near the surface and is closer to the Fermi level (Fig. 2.10). For an ideal MISCAP, no current flows in the structure (or  $dE_F/dx = 0$ ), so  $E_F$  remains flat in the semiconductor [19].

Since the carrier density depends exponentially on the energy difference  $(E_c - E_F)$ , this band bending causes an accumulation of electrons near the semiconductor surface. This is the accumulation condition. In the depletion case, when a negative voltage (V<0) is applied, the bands

Fig. 2.10 Energy-band diagrams for an ideal MIS capacitor. (a) When V > 0 the metal fermienergy is lowered (E=-qV) and the capacitor is under accumulation, and (b) when V < 0 the metal fermi-energy is raised (E=-qV) and the capacitor is under depletion. Adapted from *Physics of semiconductor devices* - *S.M. Sze* (ref. [19]).

bend upward, and the electrons are depleted (Fig. 2.10). The inversion characteristic can be expected when a large negative voltage is applied. In that case, the energy bands would bend upwards furthermore, so that the intrinsic level at the surface would cross over the Fermi level. As a result, the concentration of minority carriers (holes) would be larger near the semiconductor surface. However, the formation of surface inversion is impossible in wide gap semiconductors due to the extremely low generation rate of holes at room temperature [33], and typically the deep-depletion behavior (in the highly negative bias region) is observed.

#### **2.3.2 Interface traps**

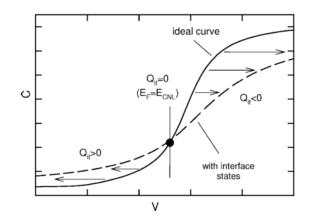

In real MISCAPs, interface traps exist affecting significantly the ideal MISCAP characteristics. Interface traps of density  $D_{it}$  and trapped charge  $Q_{it}$ , located at the insulator/semiconductor interface with trap states within the semiconductor forbitten bandgap, can be charged or discharged, depending on the surface potential [19]. Thus, unlike fixed charge, interface trapped charge is in electrical communication with the underlying semiconductor and its amount is bias dependent.  $Q_{it}$  is present in the forbidden bandgap due to the interruption of the lattice structure at the surface of a crystal (defects caused by bond breaking processes), structural defects, oxidation-induced defects and metal impurities [19,32]. The donor-type interface states filled with electrons

are neutral and become positively charged by giving up electrons, while acceptor-type interface traps are neutral when they are empty and become negatively charged when they are filled with electrons. In the case of MIS-HEMTs, a high amount of acceptor-like interface traps existing close to the insulator/semiconductor interface may cause a serious problem in device operation, since such interface traps can result in Fermi level pinning under the gate and the gate voltage may not be able to modulate sufficiently the overwhelming charge densities (2DEG density plus interface trap state density) [11].

## 2.3.3 Insulator charges

Insulator charges, other than interface trapped charge, include (a) the fixed insulator charge, (b) the insulator trapped charge and (c) mobile ionic charge [19,32]. The fixed insulator charge is generally a positive charge, located very near the semiconductor-insulator interface and is considered to be at that interface. Its density is not greatly affected by the insulator thickness but it depends on deposition conditions [19]. Fixed charge is stable and immobile under an applied electric field [32]. The insulator trapped charge (may be positive or negative), may be distributed inside the insulator layer and exists due to carriers trapped in the insulator. Trapping may result from avalanche injection, Fowler-Nordheim tunneling, or any current passing through the insulator [19,32]. The mobile ionic charge, which may be distributed throughout the insulator, is mainly caused by mobile positive ions of Na<sup>+</sup>, K<sup>+</sup>, in the case of silicon dioxide, and possibly H<sup>+</sup>. Negative ions and heavy metals may also contribute to this charge [32].

#### 2.3.4 Flat-band voltage

The flat-band voltage is determined by the metal-semiconductor work function difference  $\Phi_{MS}$  and the various insulator charges through the relationship [32]

$$V_{FB} = \Phi_{MS} - \frac{Q_{it}(\psi_s)}{C_{ins}} - \frac{Q_f}{C_{ins}} - \frac{1}{C_{ins}} \int_0^d \frac{x}{d} \rho(x) dx$$

(2.35)

where d is the insulator thickness,  $Q_f$  is the fixed trapped charge and  $\rho(x)$  is the charge density (per unit volume) from trapped and mobile charge, which may be distributed throughout the insulator.  $Q_{it}$  is designated as  $Q_{it}(\psi_s)$ , because the occupancy of the interface trapped charge depends on the surface potential  $\psi_s$  [32]. It should be noted that the intrinsic energy level  $E_i$  (which is everywhere

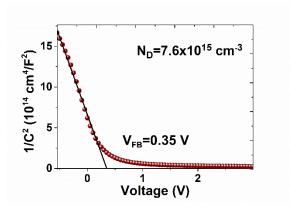

Fig. 2.11  $1/C^2$  vs bias voltage plot showing the extraction of flat band voltage of a SiN<sub>x</sub>/GaN MISCAP device at f = 1 MHz.

parallel to  $E_c$  and  $E_v$ ) in the neutral part of the device is taken as the zero reference potential and the surface potential  $\psi_s$  is measured from this reference level [32]. The effect of charges on V<sub>FB</sub> depends on the location of the charge. When the charge is located at the insulator-semiconductor interface, the effect on V<sub>FB</sub> is greatest because then it images all of its charge in the semiconductor [32]. On the other hand, when the charge is located at the gate-insulator interface, it images all of its charge in the gate and has no effect on the flat-band voltage [32]. In the case of MISCAPs where a III-Nitride is studied, the spontaneous polarization along the [0001] direction leads to a negativebound surface charge  $P_{sp}$  ( $\approx$  -1.8 x 10<sup>13</sup> cm<sup>2</sup> for Ga-face GaN) which should be included in Eq. (2.35) [33]. Thus, by assuming negligible insulator-trapped charge and mobile charge, Eq. (2.35) is given by [33,34]

$$V_{FB} = \Phi_{MS} - \frac{Q_{it}(\psi_s) + Q_f + P_{sp}}{C_{ins}} = \Phi_{MS} - \frac{Q_{eff}}{C_{ins}}$$

(2.36)

where  $Q_{eff}$ , is the total (or effective) charge at the insulator/III-nitride interface. To calculate  $Q_{eff}$  from Eq. (2.36) the experimental  $V_{FB}$  should be calculated from the  $C_{FB}$  value given by [19]

$$C_{FB} = \frac{1}{C_{ins}} + \frac{1}{C_{d(FB)}}$$

(2.37)

where  $C_{d(FB)} = \epsilon_s \epsilon_0 / L_D$ , is the capacitance of the semiconductor depletion layer at flat-band condition ( $\psi_s=0$ ),  $\epsilon_s$  is the permittivity of the semiconductor and  $L_D$  is the extrinsic Debye length

$$L_D = \left(\frac{\varepsilon_s \varepsilon_0 kT}{q^2 N_d}\right)^{\frac{1}{2}}$$

(2.38)

Another way to determine  $V_{FB}$  experimentally is to plot  $1/C^2$  versus V, measured at a high frequency, as shown in Fig. 2.11, where the lower knee of this curve occurs at V=V<sub>FB</sub> [32].

By taking into account that  $C_{ins}=\varepsilon_0\varepsilon_{ins}/d(\varepsilon_0 \text{ and } \varepsilon_{ins} \text{ are the vacuum permittivity and dielectric constant, respectively), Eq. (2.36) yields$

$$V_{FB} = \Phi_{MS} - \frac{Q_{eff}d}{\varepsilon_0 \varepsilon_{ins}}$$

(2.39)

Thus, for a given interfacial charge density, the flatband voltage is reduced as the insulator capacitance increases, i.e., for thinner oxides. Hence, oxide charges usually contribute little to flatband or threshold voltage shifts for MIS devices with thin insulators [32].

### 2.3.5 Charge conduction mechanisms

In the case of an ideal MISCAP, the conduction of the insulator is assumed to be zero. However, a real insulator may exhibit some degree of charge conduction when an electric field is applied. An estimation of the electric field in an insulator under bias is given by  $E_i \approx E_s$  ( $\varepsilon_s / \varepsilon_i$ )  $\approx V/d$ , where  $E_i$ ,  $E_s$  are the electric fields in the insulator and the semiconductor, respectively, and  $\varepsilon_s$ ,  $\varepsilon_i$  are the corresponding permittivities [19]. This equation assumes that oxide charges are negligible and that  $V_{FB}$  and the semiconductor band bending  $\psi_s$  are small compared to the applied bias voltage.

The following is foced to the electrical conduction mechanisms of silicon nitride  $(SiN_x)$  dielectric which comprises a significant part of this research work. The electrical conduction of  $SiN_x$  may be divided into three components:  $I=I_1+I_2+I_3$ , [19,35] where

$$I_{1} = C_{1} Eexp\left\{-\frac{q\left[\varphi_{1} - \left(\frac{qE}{\pi\varepsilon_{0}\varepsilon_{d}}\right)^{\frac{1}{2}}\right]}{kT}\right\}$$

(2.39)

$$I_2 = C_2 E^2 \exp(-E_2/E)$$

(2.40)

$$I_3 = C_3 E \exp(-\frac{q\varphi_3}{kT}) \tag{2.41}$$

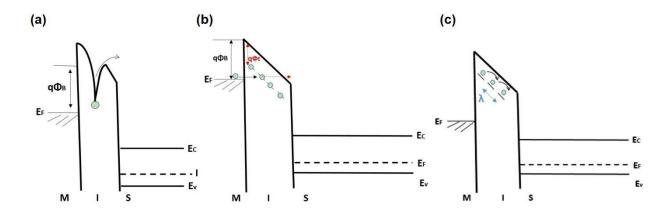

Fig. 2.12 Energy band diagrams exhibiting the basic conduction mechanisms (a) Poole-Frenkel emission, (b) field emission tunneling and (c) ohmic (hopping) conduction. When the insulator has a non-negligible number of traps, the tunneling emission is prevailed by field ionization of trapped electron into the conduction band of the insulator [19,36,37]; in that case, the measured barrier height  $\Phi_B$  is lower than the ideal (theoretical) expected value and  $\Phi_B$  may be replaced by the trap barrier height  $\Phi_t$  [36,37].

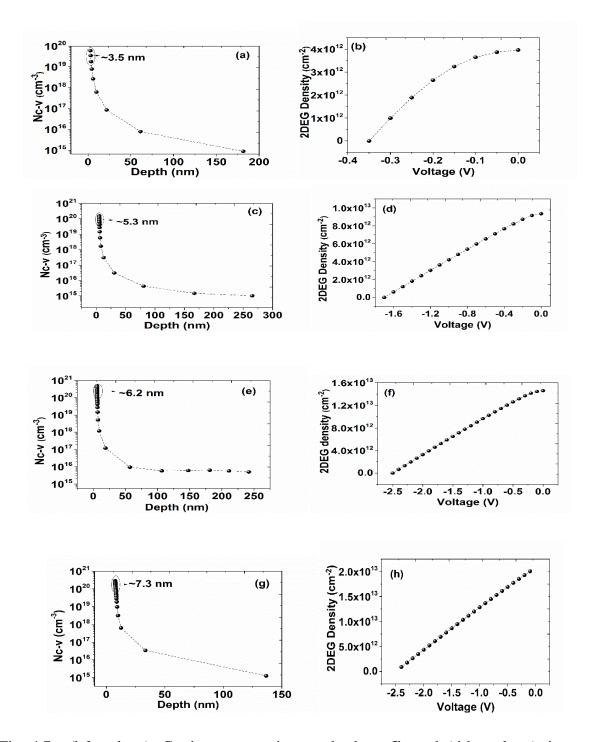

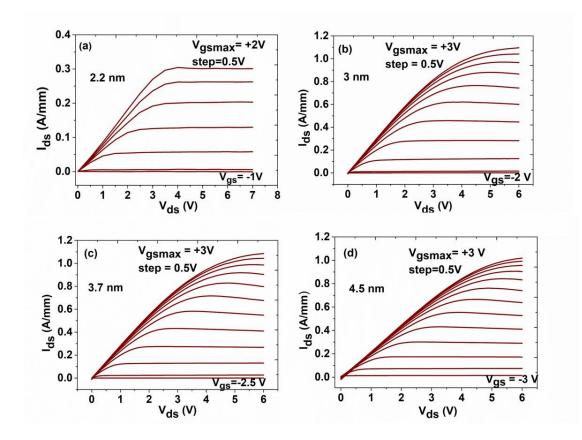

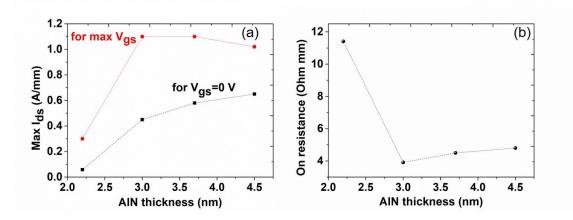

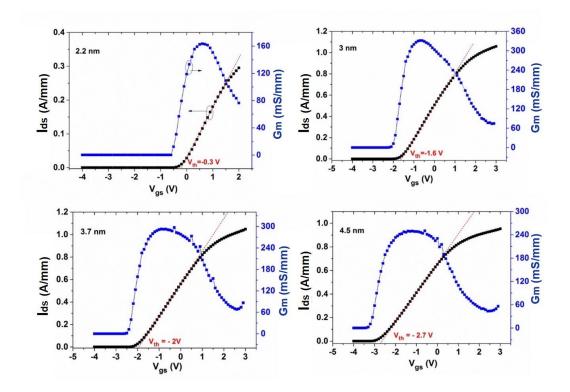

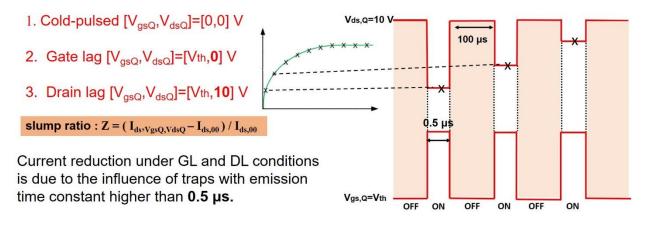

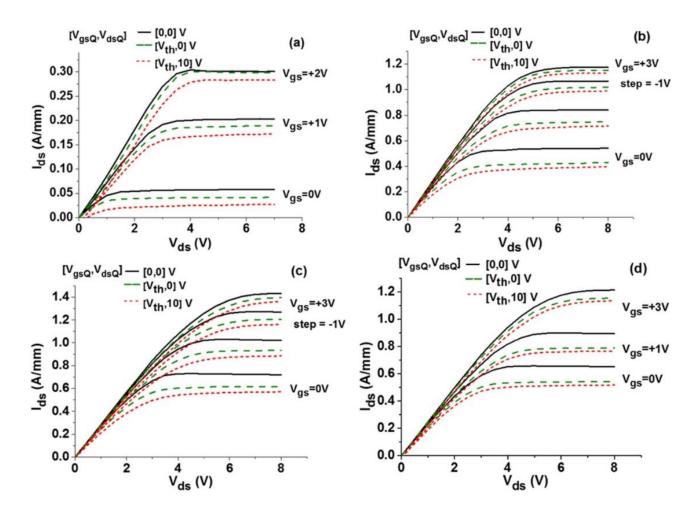

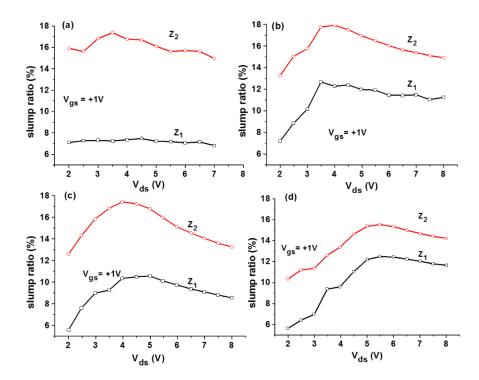

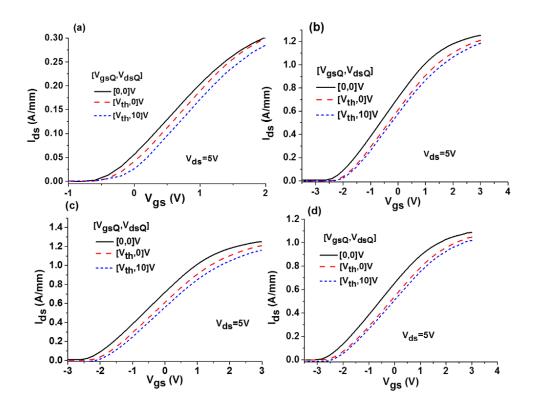

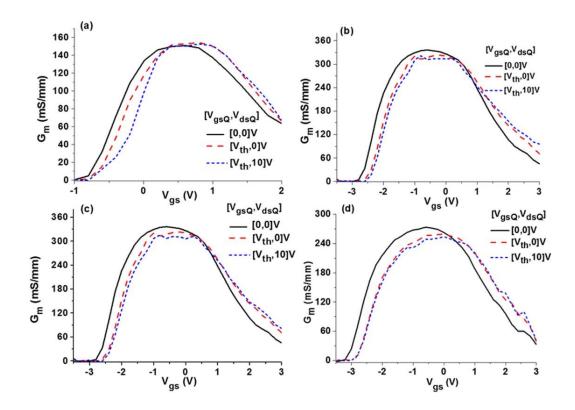

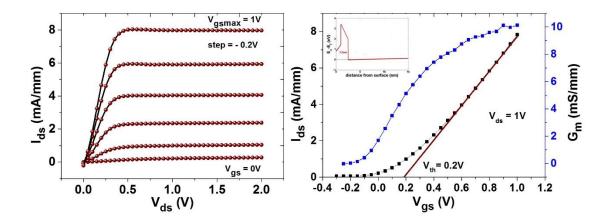

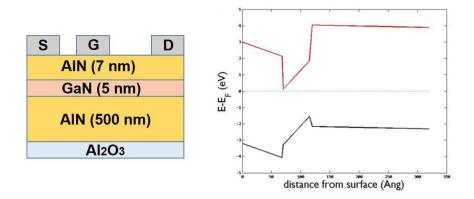

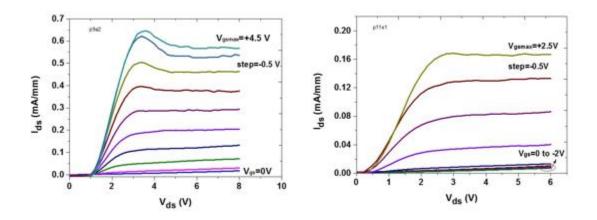

The process described by Eq. (2.39) is known as the Poole–Frenkel (PF) effect and is due to field-enhanced thermal emission of trapped electrons into the conduction band of the SiN<sub>x</sub> (Fig. 2.12). E is the electric field, q is the electron charge,  $\varphi_1$  the depth of the trap potential well,  $\varepsilon_d$  is the dynamic electric constant, and C<sub>1</sub> a proportionality constant [35]. The PF emission is somehow like an internal Schottky emission. Considering an electron in a trapping center, the barrier height for the electron emission from the trap state equals to the trap energy level without an external electric field. With an external electric field applied, the Coulomb potential energy can be reduced by a mechanism similar to that of the Schottky effect in the thermionic emission, which results in a lower potential barrier height for an electron being thermally excited out of the traps into the conduction band [19,35].