# Design and Implementation of a Directory based Cache Coherence Protocol

Dimitris Tsaliagos

Thesis submitted in partial fulfillment of the requirements for the Master of Science degree in Computer Science at the:

> University of Crete School of Sciences and Engineering Computer Science Department Knossos Av. Heraklion, GR-71409, Greece

Thesis Supervisor: Prof. Manolis G.H Katevenis

Work performed at the:

Foundation for Research and Technology - Hellas (FORTH) Institute of Computer Science (ICS) Computer Architecture and VLSI Systems (CARV) Laboratory 100 N. Plastira Av. Vassilika Vouton, Heraklion, GR-70013, Greece

April 2011

### UNIVERSITY OF CRETE COMPUTER SCIENCE DEPARTMENT

### Design and Implementation of a Directory based Cache Coherence Protocol

Thesis submitted by

### **Dimitris Tsaliagos**

in partial fulfillment of the requirements for the Master of Science degree in Computer Science

### THESIS APPROVAL

Author:

Dimitris Tsaliagos

Committee approvals:

Manolis G.H. Katevenis Professor, Thesis Supervisor

Dionisios N. Pnevmatikatos Professor

Dimitrios S. Nikolopoulos Associate Professor

Departmental approval:

Angelos Bilas

Associate Professor, Director of Graduate Studies

Heraklion, April 2010

#### Abstract

As the number of processors per chip increases, so does the need for efficient and high-speed communication support. This is necessary so that applications can exploit the numerous cores available in contemporary chip multiprocessors. Although explicit communication mechanisms such as RDMA can be used, implicit replication of data among the cores significantly simplifies the programming effort in large scale systems, by providing a simple and intuitive programming model.

This approach, however, introduces a problem known as cache coherence, where multiple copies of the data need to be kept consistent. An orthogonal solution to implicit migration of data, is to use directory based coherence protocols, which offer increased scalability by reducing the volume of messages exchanged as opposed to broadcast protocols. In this thesis a directory based cache coherence protocol is implemented in a four-core FPGA based prototype that was developed at the CARV (Computer Architecture and VLSI Systems) laboratory of FORTH (Foundation for Research and Technology – Hellas).

The protocol that is implemented can support up to 16 processors and extented an existing system, which provides local memory for cache and scratchpad use, RDMA and special hardware support for synchronization support [1].

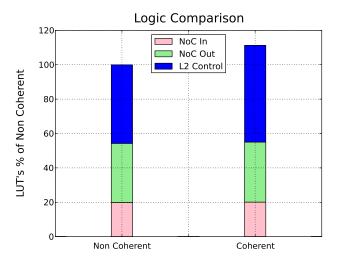

Finally, our main finding is that the logic overhead for coherence, without accounting for directory memory, as opposed to a non-coherent is 4%. Preliminary evaluations of our protocol uses custom software micro-benchmarks, which emulate common synchronization operations (found in parallel applications), such as locks and barriers. Also matrix multiplication and producer-consumer test application were developed for evaluating the protocol. Results show that matrix multiplication scales on our coherence implementation achieving a speedup of 3.74 on 4 cores.

# Contents

| 1 | Intr                                    | oducti                    | oduction 1                                |    |  |  |

|---|-----------------------------------------|---------------------------|-------------------------------------------|----|--|--|

|   | 1.1                                     | Cache                     | Coherence Basics                          | 2  |  |  |

|   |                                         | 1.1.1                     | The Coherence Problem                     | 2  |  |  |

|   | 1.2                                     | Impler                    | mentation Schemes                         | 4  |  |  |

|   | 1.3                                     | Thesis                    | Contributions                             | 6  |  |  |

| 2 | Bac                                     | kground                   |                                           |    |  |  |

|   | 2.1 Directory-Based Coherence Protocols |                           |                                           |    |  |  |

|   | 2.2                                     | 2.2 Consistency Models    |                                           |    |  |  |

|   | 2.3                                     | 3 Directory Organizations |                                           |    |  |  |

|   |                                         | 2.3.1                     | Flat Schemes                              | 15 |  |  |

|   |                                         | 2.3.2                     | Hierarchical Schemes                      | 15 |  |  |

|   |                                         | 2.3.3                     | Reducing Directory Memory Overhead        | 16 |  |  |

| 3 | $\mathbf{Des}$                          | ign an                    | d Implementation                          | 19 |  |  |

|   | 3.1                                     | Baseli                    | ne System                                 | 20 |  |  |

|   | 3.2                                     | Design                    | 1                                         | 21 |  |  |

|   |                                         | 3.2.1                     | Hash Directory Organization               | 21 |  |  |

|   |                                         | 3.2.2                     | Protocol Design                           | 24 |  |  |

|   |                                         | 3.2.3                     | L2 Cache Architecture                     | 30 |  |  |

|   |                                         | 3.2.4                     | L2 Cache Controller Modifications         | 33 |  |  |

|   |                                         | 3.2.5                     | Directory Controller Design               | 38 |  |  |

|   | 3.3                                     | 3.3 Implementation        |                                           | 40 |  |  |

|   |                                         | 3.3.1                     | Protocol Packet Format                    | 40 |  |  |

|   |                                         | 3.3.2                     | Directory Controller NoC Input Module     | 41 |  |  |

|   |                                         | 3.3.3                     | Directory Controller Hash Lookup Module   | 43 |  |  |

|   |                                         | 3.3.4                     | Directory Controller Action Lookup Module | 48 |  |  |

|   |                                         | 3.3.5                     | Directory Controller NoC Output Module    | 50 |  |  |

|   |                                         |                           | i                                         |    |  |  |

| 4 | 4 Evaluation |               |                                |    |  |

|---|--------------|---------------|--------------------------------|----|--|

|   | 4.1          | Target        | FPGA                           | 53 |  |

|   | 4.2          | Hardware Cost |                                |    |  |

|   |              | 4.2.1         | Directory Controller Resources | 54 |  |

|   |              | 4.2.2         | L2 Cache Hardware Resources    | 56 |  |

|   | 4.3          | Berformance   |                                |    |  |

|   |              | 4.3.1         | Protocol Performance Metrics   | 57 |  |

|   |              | 4.3.2         | Micro-benchmarks               | 59 |  |

| 5 | Con          | clusio        | ns                             | 67 |  |

|   | 5.1          | Future        | Work                           | 68 |  |

# List of Figures

| 1.1  | Cache Coherence problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2  | Simple Directory Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.1  | Basic MSI Protocol Cache FSM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.2  | Basic MSI Protocol Directory FSM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

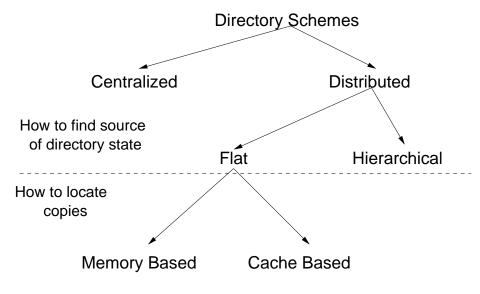

| 2.3  | Directory Schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

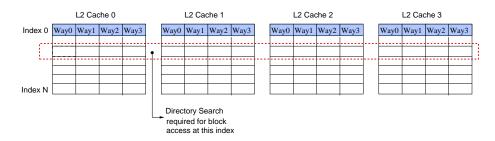

| 2.4  | Sparse Directory Associativity Demands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

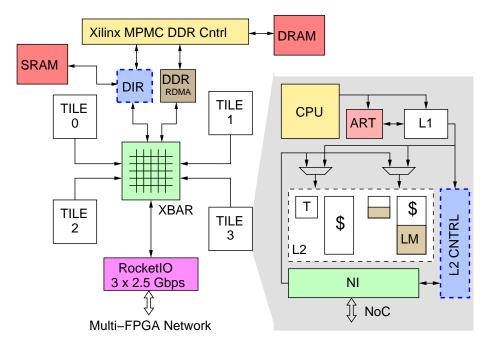

| 3.1  | System Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

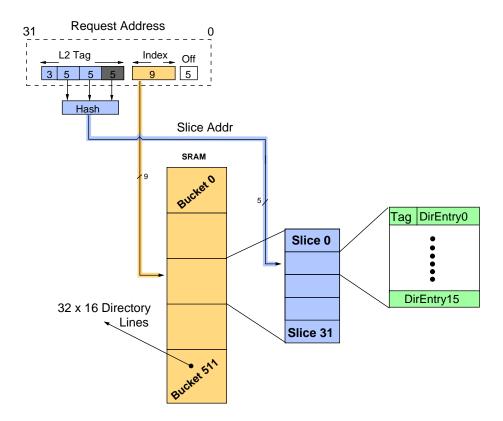

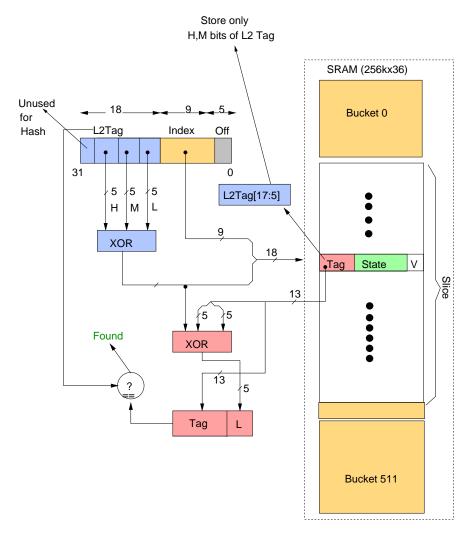

| 3.2  | $Hash \ Directory \ Organization \qquad \ldots \qquad \ldots \qquad 23$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.3  | $Simple\ Protocol\ Transactions\ Example\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.4  | Transient States and Protocol Races $\hdots \hdots \hdots$ |

| 3.5  | L2 Cache Block Diagram $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 31$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.6  | Atomic-Fetch-and $\Phi$ operation FSM $\hfill \ldots \ldots \ldots \hfill 38$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

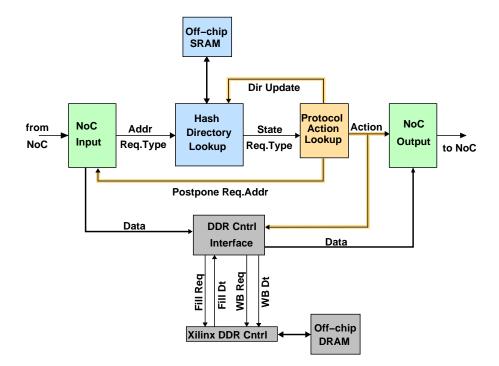

| 3.7  | Directory Controller Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

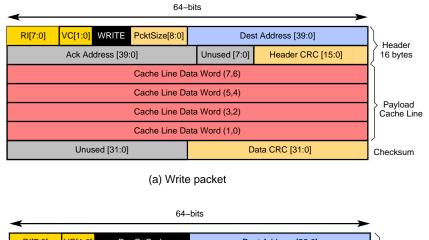

| 3.8  | $Coherence\ Packet\ Format \ \ \ldots \ \ \ldots \ \ \ldots \ \ \ \ \ \ \ \ \ \ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

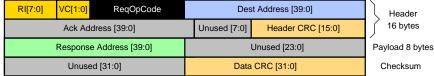

| 3.9  | Directory Network Input Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.10 | Directory Hash Lookup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

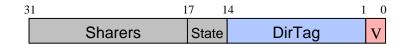

| 3.11 | Directory Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

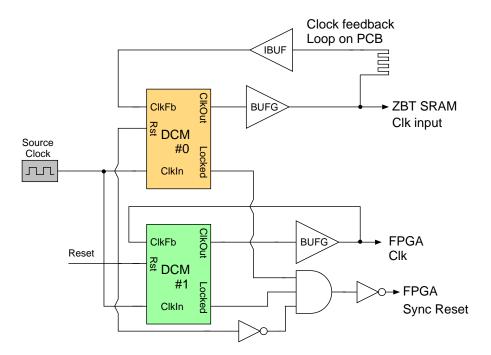

| 3.12 | SRAM Memory Clock Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

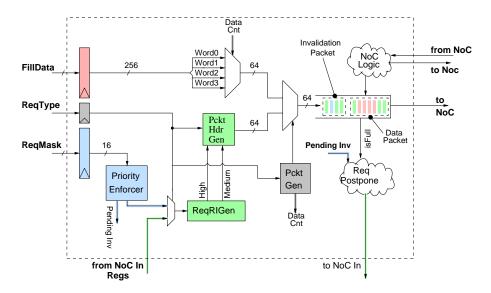

|      | NoC Output Datapath                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

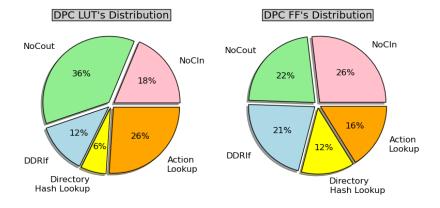

| 4.1  | Directory LUT's and FF's utilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.2  | LUT's Comparison of Coherent and Baseline Design $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.3  | Read Miss Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# List of Tables

| 3.1  | Protocol Messages Categorization                                                 | 25 |

|------|----------------------------------------------------------------------------------|----|

| 3.2  | Coherence VC / Direction                                                         | 30 |

| 3.3  | L2C (Stable) States transition Table $\ldots \ldots \ldots \ldots \ldots \ldots$ | 34 |

| 3.4  | L2C (Transient) States transition Table                                          | 35 |

| 3.5  | Directory Protocol States                                                        | 49 |

|      |                                                                                  |    |

| 4.1  | Virtex-5 LX110T                                                                  | 53 |

| 4.2  | System Resource Utilization                                                      | 54 |

| 4.3  | Directory Hardware Resources breakdown                                           | 55 |

| 4.4  | L2 Cache controller LUT's distribution                                           | 57 |

| 4.5  | Coherence Transactions Latency                                                   | 58 |

| 4.6  | Shared Counter Slowdown                                                          | 62 |

| 4.7  | Atomic Fetch and Add Latency                                                     | 62 |

| 4.8  | Synchronization Primitives Latencies                                             | 63 |

| 4.9  | Producer Consumer Latency                                                        | 64 |

| 4.10 | Matrix Multiplication Speedup                                                    | 64 |

|      |                                                                                  |    |

#### ACKNOWLEDGMENTS

The work reported in this thesis has been conducted at the Computer Architecture and VLSI Systems (CARV) Laboratory of the Institute of Computer Science (ICS) of the Foundation for Research and Technology - Hellas (FORTH), and has been financially supported by a FORTH-ICS scholarship, including funding by the European Commission.

First of all I would like to thank my advisor Prof. Manolis G.H Katevenis as also Prof. Dionisis N. Pnevmatikatos and Prof. Dimitris S. Nikolopoulos, for their guidance and their support throughout this work. Their constructive remarks and the time they devoted to me constitute a significant amount of help. Furthermore, I would like to thank all my fellow students and/or co-workers at FORTH for their help and their support in all the good and bad times. Working in the same environment with you my friends (Manolis Marazakis, Mixalis Ligerakis, Spyros Lyberis, Stamatis Kavadias, Vasilis Papaefstathiou, Michalis Alvanos, Giannis Klonatos, and many othesr....) has been an honor and very pleasant. Also, I would like to thank especially George Nikiforos and George Kalokairinos for guiding and helping me throughout this work as the initial design of the system was designed by them. Finally, I would like to thank my family (Mixalis, Zoe, and Marialena) for their love and support they have offered me all these years. They have sacrificed everything in order to help me reach my goals. Without their help I would certainly have not made it to here. Last but not least, I would like to thank my close friends for encouraging me and supporting me all these years: Thanos Makatos, Zoe Sebepou, Artemis Papakonstantinou, Alexandros Kapravelos, Vicky Papavisileiou, Evi Dagalaki, Evi Galanou and Antigoni Konstantinou.

to my nephew Michalis

# Chapter 1

# Introduction

Having a large number of cores on a single chip, certainly alters the architectural decisions that have been considered efficient in traditional multiprocessors until now. Chip Multiprocessor (CMP) architectures are very suitable for throughput computing, where several independent programs run in different processing cores. Nevertheless, the need to make all the processing cores cooperate efficiently for a single computation, is of major importance for the scalability of these architectures. A primary component of these architectures, on which a great amount of attention is focused, is the communication architecture among the multiple processors, as well as between processors and off-chip main memory.

Cache coherence protocols are a key component, which provides a way for the programmer to write parallel applications that employ conventional ld/st instructions to shared addresses and allows implicit replication and migration of data among the caches of the processors comprising the system, to improve performance.

With an increasing number of cores the most suitable way of providing cache coherence is to implement a directory-based protocol, alternative protocols are utilize broadcasts to other caches in the system and thus are not as scalable as directory based protocols. Bus-based broadcast protocols, usually called snooping protocols as also directory broadcast protocols are not very powerefficient due to the large amount of messages they generate. To avoid broadcasts, directory based protocols require a system wide auxiliary structure to hold the state of the blocks cached or the corresponding state of a block in main memory. A significant part of the scalability of such architectures depends on the area and increased complexity that the cache coherence protocol adds, which are mostly accounted to the directory memory controllers as it will be discussed in Chapter 4.

There are two central aspects of directory implementation; the directory

organization and the set of messages types and message actions of the protocol that is discussed in Chapter 3. The former provides the basic properties of the abstract data structures used to store the directory information, which determine the amount of state required to store the sharing information. Furthermore, it may affect the latency of directory accesses, since some directory organizations require more complex logic to implement than others as it is will be discussed in Chapter 2. Message types and actions are dictated by the specific coherence protocol, and must be carefully designed to account for potential interactions with attributes of the chosen directory organization, as it will be described in Section 3.2.1.

In this thesis we design and implement a directory based cache coherence protocol, focusing on the directory state organization. An MSI cache coherence protocol is used to maintain the coherence property among L2 private caches in a prototype board that implements the SARC architecture [1]. A single node of the prototyped system is a single Xilinx XUPV5 board that consists of four microblaze soft-core processors, each with a private cache hierarchy, on a single Field Programmable Gate Array (FPGA) chip. The prototypes supports multi-board configurations, utilizing 3 SATA connections. The prototype architecture will be detailed in section 3.1. Memory resource limitation, in the baseline FPGA design, prevent an on-chip directory implementation. Thus, our design employs Off-chip Static Random Access Memory (SRAM), for directory memory, while the directory controller is implemented on the FPGA chip.

A primary goal of the coherence design in this work, is to reduce the average latency of directory access exploiting an address-based hashing to retrieve coherence information of cached blocks, that are kept in off-chip. SRAM.The directory organization we propose can support coherence up to 16 processors, which is supported in the baseline architecture by connecting multiple FPGA boards.

## **1.1** Cache Coherence Basics

This section presents some background information about the cache coherence property as well as the two basic protocol implementation schemes that enforce the cache coherence property.

#### 1.1.1 The Coherence Problem

The use of private caches in a shared memory multiprocessor environment, introduces an inherent cache coherence problem. If more than one processors maintain locally cached copies of a memory data block , any modification to the

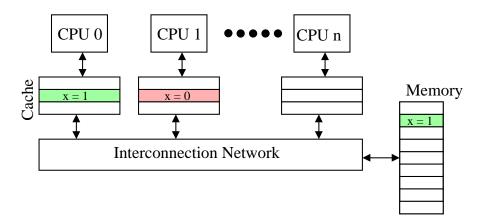

Figure 1.1: Cache Coherence problem

block's data is likely to lead to data incoherence. .

The cache coherence problem is illustrated in Figure 1.1. Assume that, initially memory contains the value 0 at the memory location for variable x, and that both CPU0 and CPU1 read x and cache it locally. So if subsequently CPU0 writes value 1 in x, data in CPU1 cache will become stale, since reading x from CPU1 will return the old value of x by accessing the copy locally cached.

Informally, we could say that a memory system is coherent if any read of a data item returns the most recently written value of that data item. This definition, although intuitively appealing, is vague and simplistic; the reality is much more complex. This simple definition contains two different aspects of memory system behavior, both of which are critical to writing correct sharedmemory programs. The first aspect, called coherence, defines what values can be returned by a read. The second aspect, called consistency, determines when a written value will be returned by a read which is discussed in Chapter 2. Let's look at the strict definition of coherence first [7].

A memory system is coherent if

- 1. A read by a processor P to a location X that follows a write by P to X, with no writes of X by another processor occurring between the write and the read by P, always returns the value written by P.

- 2. A read by a processor to location X that follows a write by another processor to X returns the written value if the read and write are sufficiently separated in time and no other writes to X occur between the two accesses.

- Writes to the same location are serialized; that is, two writes to the same location by any two processors are seen in the same order by all processors. For example, if the values 1 and then 2 are written to a location, processors

can never read the value of the location as 2 and then later read it as 1.

The first property simply preserves program order—we expect this property to be true even in uni-processors. The second property defines the notion of what it means to have a coherent view of memory: If a processor could continuously read an old data value, we would clearly say that memory was incoherent. The need for write serialization is more subtle, but equally important.

If appropriate coherence actions were invoked whenever a cache line was written, then the load issued from CPU1 would return the correct value either by invalidating all the cached copies of location x or by updating the values of all the cached copies of x with the latest value. Although some hybrid techniques have been proposed, most modern cache-coherent multiprocessors use the invalidation technique rather than the update technique since it is easier and scalable in terms of network traffic than update protocols.

## **1.2 Implementation Schemes**

The previous section describes the cache coherence problem and introduces the coherence protocols as the agents that solves the coherence problem. There are two main implementation schemes of cache coherence protocols, bus-based protocols (snoopy) and directory-based protocols. In this section, we present the two dominant hardware schemes that are used to enforce the cache coherence property.

#### Bus Based Protocols (Snoopping)

Shared memory systems that are based on a shared broadcast medium follow the Snooping approach, no parts of memory are assigned to any processor. Assuming a single level of private caches, a processor that requests to access a memory block, which does not resides in its local cache, it sends a message to all the other caches and main memory. All the caches snoop the traffic on the interconnection network to identify a new message. If no cache has a copy of the requested block then the block is loaded from main memory. If, however, one or more caches maintain a valid copy, one of them sends the requested block back to the cache that requested it. Messages are used not only to facilitate data transferring. Every message is assigned a type, which has a specific meaning for the coherency protocol. Based on this type caches that receive such messages are becoming aware of the intention of the requesting processor.

Having this knowledge, caches are able to follow the steps imposed by the coherency protocol. This category of coherency protocols add a requirement to the interconnection network properties, which constitutes the basic property of

Figure 1.2: Simple Directory Design

the protocol. This requirement refers to the ability that must be offered to any cache to broadcast messages and also to snoop the bus activity. Otherwise, it is impossible for the distributed protocol to synchronize the requests of processors. In snooping protocols the bus act as the serialization point for coherence transactions.

#### **Directory Protocols**

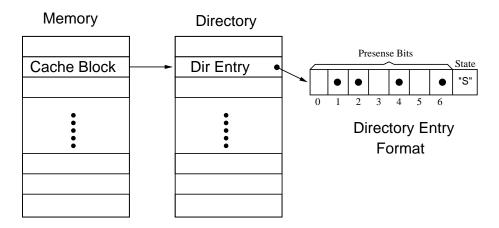

The use of an arbitrary multi-stage interconnection network poses challenges to the implementation of cache-coherent shared memory. Although connecting the processing nodes on a scalable network topology, .i.e (Mesh, hybercube), yields to potentially more bandwidth efficient system, it also takes away the inherent broadcast capabilities of a shared bus that can be exploited to implement broadcast-based coherence. Instead, such systems are based on tracking which processor cache contain a memory line, to send the number of necessary messages, and avoid broadcasts. Sharing information is kept in an auxiliary data structure called a directory [6], illustrated in Figure 1.2.

Furthermore, directory information can be distributed to multiple directory engines to avoid the performance bottleneck of a single, monolithic directory. Each node or group of nodes is associated with a directory corresponding to the locations in that node's group local memory. As shown in Figure 1.2, an example of one node's group directory contents. The directory consists of a collection of directory entries, one for each memory block in the node's local memory. Because the processor caches interface to the system at a cache line granularity that is, each processor cache miss or write back transfers a single cache line of data between memory and the cache — the size of the memory block tracked by each directory entry is usually one cache line. In its simplest form, a directory entry contains two fields: a state indication and a presence bit vector. In invalidation-based protocols the state indication specifies whether the memory line associated with the directory entry is held shared (i.e., read-only) in one or more caches or whether it is held exclusive (i.e., with read/write permission) in a single processor's cache. The presence bit vector indicates which processors are caching the memory line; if the memory line is held exclusive, only one presence bit may be set. The directory entry depicted in Figure 1.2 shows a case in which the corresponding memory line is held shared, indicated symbolically by the "S" in the state field, and is present in the caches of processors 1, 2, 4, and 6, indicated by the presence bit vector.

When a memory request arrives at a processing node, the controller of the node then retrieves the corresponding directory entry to determine what additional actions are required to service the request. For example, as shown in Figure 1.2, if processor 3 requested exclusive access to the memory line, the memory line first must be removed, or invalidated, from all processor caches currently holding it. In a distributed system, the controller of the node must consult the presence bit vector to determine that explicit invalidation messages need to be sent to processors 1, 2, 4, and 6. In a bus-based system, these invalidation's would be performed automatically when processor 3's exclusive request was issued on the bus.

This is a simplified case is just one example of the operation of a distributed cache coherence protocol. In practice, these protocols are complex, especially because so many race conditions can occur as a result of the lack of a shared bus to serialize all processors' memory requests. More details of distributed cache coherence protocol implementation can be found in [18].

## **1.3** Thesis Contributions

This thesis presents the design and implementation of a directory-based cache coherence protocol in an FPGA prototype. The main contribution of this thesis are the following:

- Working hardware implementation of an MSI directory-based cache coherence protocol empolying the necessary transient states in order to handle distributed controller cooperation and protocol races (Chapter 3).

- Design and implementation of a hash based directory state organization in off-chip SRAM that minimize the latency of directory accesses to conceptually associative directory state (Sections 3.2.1, 3.3.3).

The rest of the thesis is organized as follows. Background information is discussed in the rest of this chapter. Chapter 2 presents various directory organizations that are commonly used and the problems that arise from each one. In Chapter 3 the cache coherence support on the SARC prototype is detailed. The evaluation of the proposed directory organization in terms of area and complexity, and the protocol performance is presented in Chapter 4. Finally, Chapter 5 concludes this study and future work directives are discussed.

# Chapter 2

# Background

## 2.1 Directory-Based Coherence Protocols

The basic states of a cache block in a directory-based protocol are exactly like those in a snooping protocol, and the states in the directory are also analogous to snooping protocols. Thus we present simple state diagrams that show the state transitions for an individual cache block and then examine the state diagram for the directory entry corresponding to each block in memory. These state transition diagrams do not represent all the details of a coherence protocol; they only show the basic MSI protocol, without showing the detailed implementation that depends on a number of details, such as the interconnection network ordering properties, the directory organization restrictions, and the buffering structures that are used.

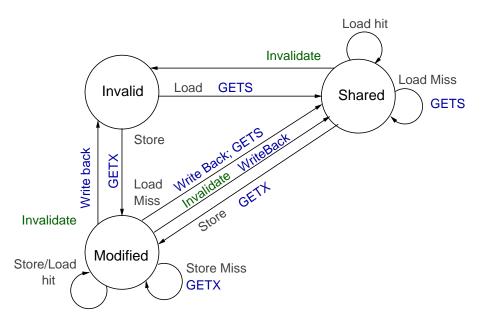

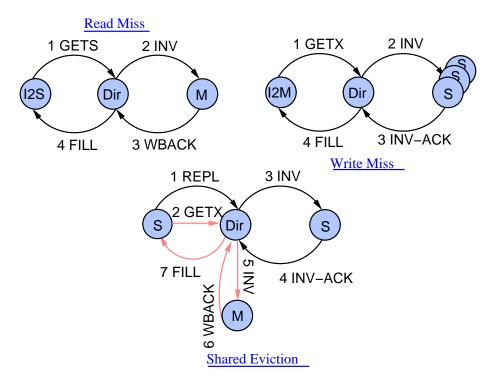

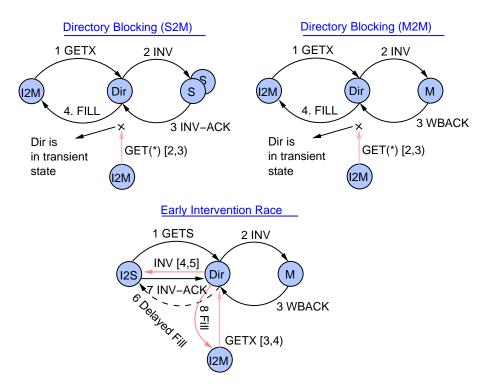

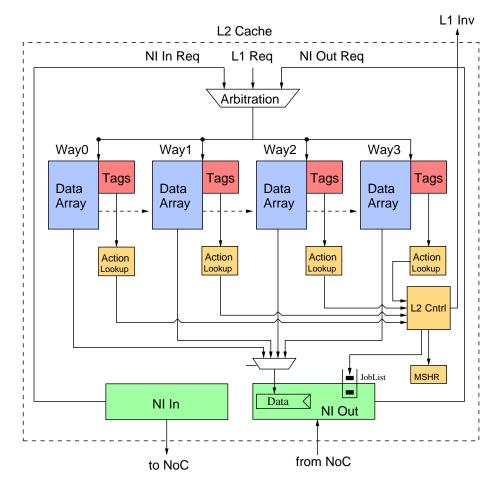

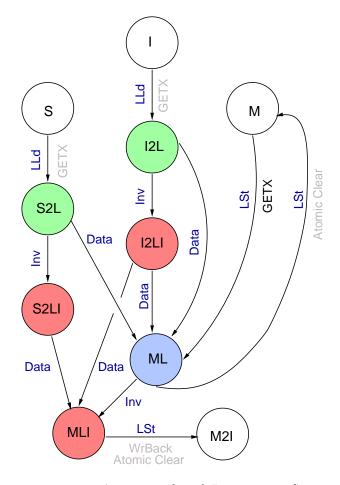

In this section we present the basic protocol state diagrams. The issues involved in implementing these state transition diagrams are examined in Section 3.3. Figure 2.1 shows the protocol actions to which an individual cache responds. The notation that we use is the following: requests coming from the directory are showed in green and processor, requests that are sent to the directory are showed in blue, and processor events are showed in gray.

The state transitions for an individual cache are caused by read misses that generate GETS messages, write misses that generate GETX messages and from invalidation requests that generates write backs; these operations are all shown in Figure 2.1.

GETS and GETX requests require data value replies, and these events wait for replies before changing state. Knowing when invalidates complete is a separate problem and is handled separately. The operation of the state transition diagram for a cache block is as follows. Upon a load to a cache block that it is in shared or invalid state, a GETS request is sent to the directory. For stores to a

Figure 2.1: Basic MSI Protocol Cache FSM

cache block that hit in the cache, a GETX request is sent instead. Furthermore, the directory send data replies and invalidation requests respectively according to the directory side of the protocol. Furthermore, write back messages are generated from the cache in response to an invalidation request, or due to cache eviction as it is shown in the state diagram below.

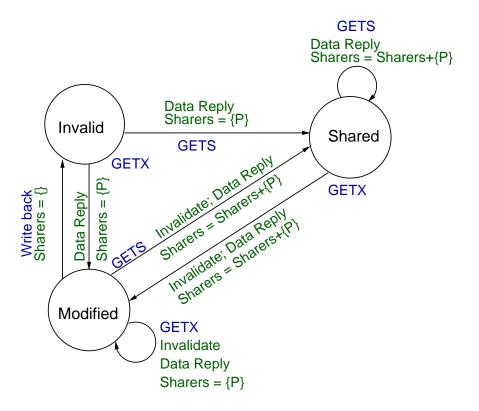

In a directory-based protocol, the directory implements the other half of the coherence protocol. A message sent to a directory causes two different types of actions: updating the directory state and sending additional messages to satisfy the request. The states in the directory represent the three standard states for a block; unlike in a snoopy scheme, however, the directory state indicates the state of all the cached copies of a memory block, rather than for a single cache block. The memory block may be uncached by any node (invalid), cached in multiple nodes and readable (shared), or cached exclusively and writable in exactly one node (modified). In addition to the state of each block, the directory must track the set of processors that have a copy of a block; we use a set called Sharers to perform this function.

Directory requests need to update the set Sharers and also read the set to perform invalidation's. Figure 2.2 shows the actions taken at the directory in response to messages received. The directory receives three different requests: GETS, GETX and write back. Our simplified protocol assumes that some actions are atomic, such as requesting a value and sending it to another node; a realistic implementation cannot use this assumption. To understand these directory operations, let's examine the requests received and actions taken state by state. When a block is in the invalid state, the copy in memory is the current value, so the only possible requests for that block are:

- *GETS* : The requesting processor is sent the requested data from memory, and the requestor is made the only sharing node. The state of the block is made shared.

- *GETX* : The requesting processor is sent the value and becomes the sharing node. The block is made exclusive to indicate that the only valid copy is cached. Sharers indicates the identity of the owner.

When the block is in the shared state, the memory value is up to date, so the same two requests can occur:

- *GETS* : The requesting processor is sent the requested data from memory, and the requesting processor is added to the sharing set.

- *GETX* : The requesting processor is sent the value. All processors in the set Sharers are sent invalidate messages, and the Sharers set is to contain the identity of the requesting processor. The state of the block is made modified.

When the block is in the modified state, the current value of the block is held in the cache of the processor identified by the set Sharers (the owner), so there are three possible directory requests:

- *GETS*: The owner processor is sent a data fetch message, which causes the state of the block in the owner's cache to transition to shared and causes the owner to send the data to the directory, where it is written to memory and sent back to the requesting processor. The identity of the requesting processor is added to the set Sharers, which still contains the identity of the processor that was the owner (since it still has a readable copy).

- Write Back : The owner processor is replacing the block and therefore must write it back. This write back makes the memory copy up to date (the home directory essentially becomes the owner), the block is now uncached, and the Sharers set is empty.

- *GETX* : The block has a new owner. A message is sent to the old owner, causing the cache to invalidate the block and send the value to the directory, from which it is sent to the requesting processor, which becomes the new owner. Sharers is set to the identity of the new owner, and the state of the block remains exclusive.

Figure 2.2: Basic MSI Protocol Directory FSM

This state transition diagram in Figure 2.2 is a simplification. In the case of a directory, as well as a snooping scheme implemented with a network other than a bus, our protocols will need to deal with non-atomic memory transactions and implementations issues. Section 3.2.2explores these issues in depth.

### 2.2 Consistency Models

A Consistency model [5] is a contract between the software and the memory system. It says that if the software agrees to obey certain rules, the memory promises to work correctly according to the programmer's expectations. Unfortunately but expectably there is a trade-off between the restrictions the consistency model poses on the programmer and the performance of such a model when utilized in a distributed shared memory system. The most intuitive is the Sequential Consistency model.

Sequential consistency is a slightly weaker memory model than strict consistency. Lamport [2], who first defined it, posted the following definition: A system is sequentially consistent if:

"The result of any execution is the same as if the operations of all processes

#### 2.3. DIRECTORY ORGANIZATIONS

were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program".

This fairly complicated definition states that any interleaving of programs operations is acceptable behavior, but all processors must see the same sequence of memory references. A memory system in which one processor sees one interleaving and another processor sees a different one is not sequentially consistent.

A better solution in terms of performance, would be to let a processor finish its critical section and then make sure that the final results were visible everywhere, not worrying whether all intermediate results had also been propagated to all memories in order, or even at all. Such a consistency model is the weak consistency model. The properties of the weak consistency models are the following:

- Accesses to synchronization variables are sequentially consistent.

- No access to a synchronization variable should be issued until all previous processor data accesses (writes) have completed.

- No data access (read or write) should be issued until all previous processor accesses to synchronization variables have been performed.