# Realization and physical analysis of field-effect transistors based on GaN nanofins and vertical nanowires

Doctoral thesis

*by* George Doundoulakis

# UNIVERSITY OF CRETE PHYSICS DEPARTMENT

# Realization and physical analysis of field-effect transistors based on GaN nanofins and vertical nanowires

by George Doundoulakis

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Physics

October 2019

# Realization and physical analysis of field-effect transistors based on GaN nanofins and vertical nanowires

### Ph.D dissertation

by

George Doundoulakis

#### Advisor Committee:

Alexandros Georgakilas, Professor, Supervisor

Eleftherios Iliopoulos, Associate Professor

George Konstantinidis, Research Director, IESL, FORTH

#### **Examination Committee:**

Alexandros Georgakilas, Professor, Supervisor

Eleftherios Iliopoulos, Associate Professor

George Konstantinidis, Research Director, IESL, FORTH

Xenophon Zotos, Professor

Nikolaos Pelekanos, Professor, Dpt. of Materials Science and Technology, Univ. of Crete

$Konstantinos\ Zekentes, Principal\ Researcher, IESL, FORTH$

George Deligeorgis, Assistant Researcher, IESL, FORTH

#### **Abstract**

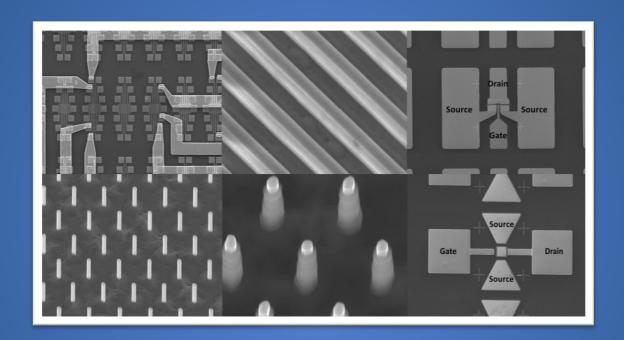

Semiconductor nanostructures, such as nanowires (NWs) and nanofins, have gained significant interest as promising elemental building blocks in nanoelectronic and nanophotonic applications. Their reduced dimensionality and high aspect ratio could enhance the miniaturization of devices and lead to high device density, decreased power consumption and high operation frequency. Among them, nanostructures of gallium nitride (GaN) have attracted much attention for the exploitation of the fundamental advantages of GaN material, such as wide direct band gap, high thermal conductivity and high breakdown voltage. This work has created new knowledge for material and device processing effects on the performance of next-generation GaN-based nanoelectronic devices, with focus on field-effect transistors (FETs) based on GaN nanofins (FinFETs) and vertical nanowires (V-NW FETs).

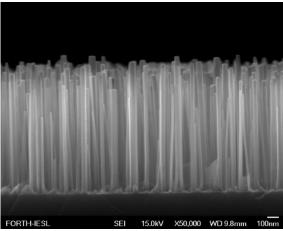

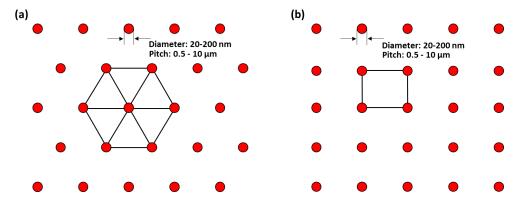

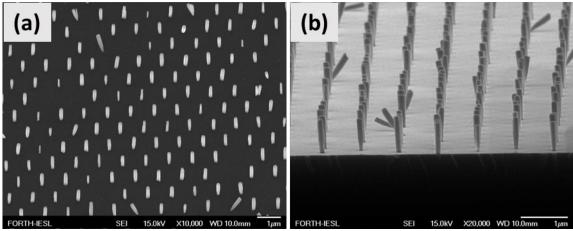

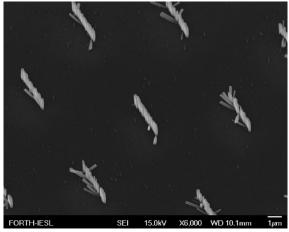

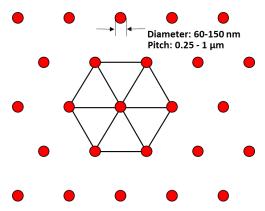

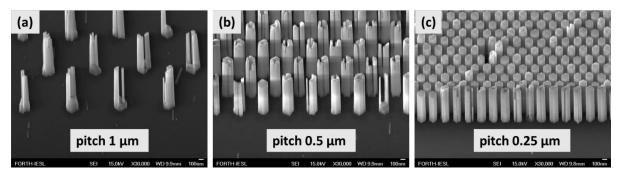

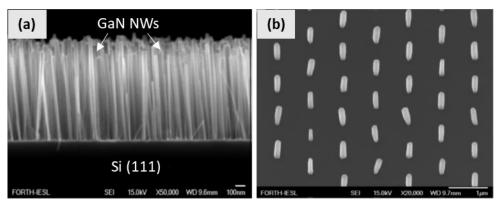

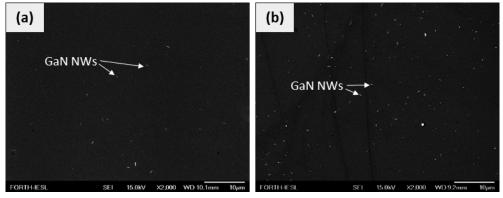

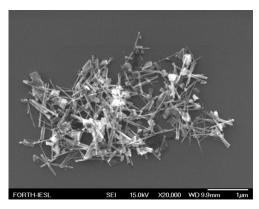

Initially, the experimental bottom-up processes for formation of GaN-based NWs and nanofins by Plasma Assisted Molecular Beam Epitaxy (PAMBE) are briefly discussed. The spontaneous growth of GaN NWs by PAMBE resulted to large deviations in shape and size of GaN NWs, critical parameters for the assembly of V-NW FETs, where an accurate control of the position and dimensions of NWs is necessary. Therefore, selective area growth (SAG) was studied for aligning GaN NWs on different substrates without using metal catalysts, which is accomplished by epitaxial growth on a substrate coated with a nanopatterned mask. Two different substrates were used for the SAG of GaN NWs. The growth of GaN NWs on Si (111) substrates patterned with a thermally grown SiO<sub>2</sub> mask revealed the difficulty of filling all the Si mask windows with GaN NWs, while the grown GaN NWs exhibited larger diameter than the mask window and, in some cases, inclined direction. Nanoribbons (stripes) were also patterned on the SiO<sub>2</sub>/Si substrates, resulted to nucleation and growth of multiple GaN NWs inside each nanoribbon, instead of a compact fin material. The use of SiO<sub>2</sub>/GaN/Si substrates for the SAG of GaN NWs was also investigated. In this case, the deposition of GaN material was enhanced by the reduction of window pitch, with the pitch of 250 nm exhibiting single NW formation that follows the diameter of the mask window. However, photoluminescence (PL) experiments may suggest the formation of crystal defects in these compact NWs, possibly due to coalescence of multiple narrow NWs.

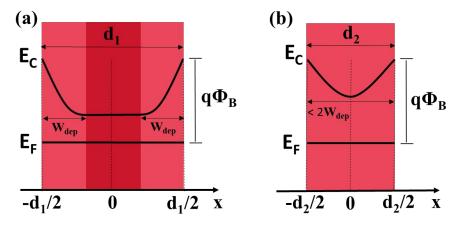

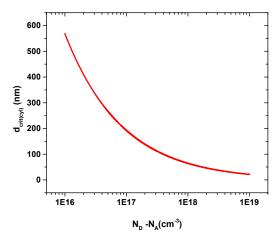

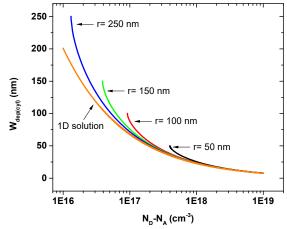

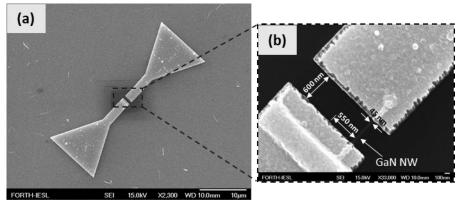

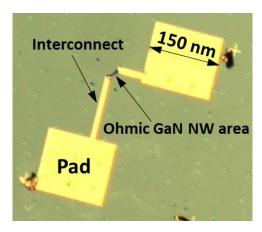

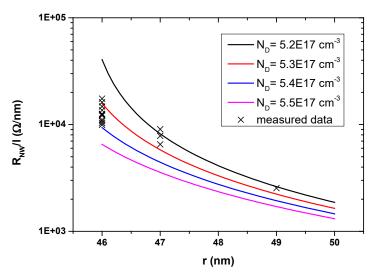

The electrical transport properties of GaN NWs grown spontaneously on Si (111) and nanopatterned  $SiO_2/Si$  (111) substrates were determined, in order to evaluate the unintentional doping, and understand the surface states induced band-bending and the size effects on the conductivity of bottom-up grown GaN NWs. Conventional nanofabrication techniques were used to define multiple ohmic contacts to individual GaN NWs dispersed on  $SiO_2/Si$  (111) substrates, with NW diameters ranging from 30 to 140 nm and lengths ranging from 500 to 1900 nm. Current-Voltage (I-V) measurements indicated that the apparent resistivity values of GaN NWs depended on their diameter, due to carrier depletion induced by Fermi level pinning at the lateral NW surfaces. Assuming that  $(E_C-E_F)_S=0.55$  eV at the GaN NW lateral surface, a critical GaN NW

diameter of ~87 nm for full depletion (punch through) of the GaN NW was calculated, in agreement with the experimental observations. The actual resistivity of the GaN NW crystal was then calculated by subtracting the value of the critical GaN NW diameter from the nominal one, which resulted to resistivity values in the range of 0.01 to 0.03  $\Omega$ cm. The estimated average doping concentration was  $5.2 \times 10^{17}$  cm<sup>-3</sup>.

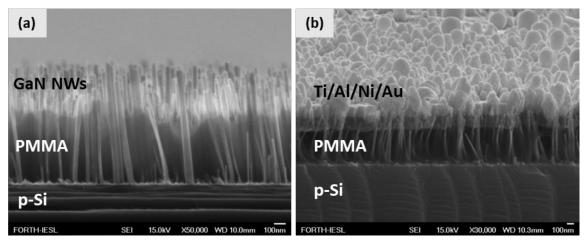

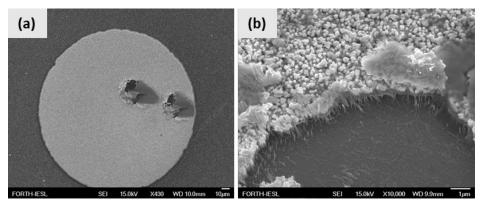

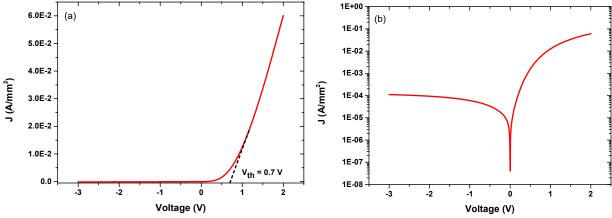

The n-type behavior of GaN NWs was exploited in the first time, to our knowledge, fabrication of vertical p-Si/n-GaN NW heterojunction diodes. The diodes exhibited a clear rectifying behavior, although a non-optimized fabrication process was used, which is promising for future nanophotonic and nanoelectronic device applications (e.g. nanowire heterojunction solar cells).

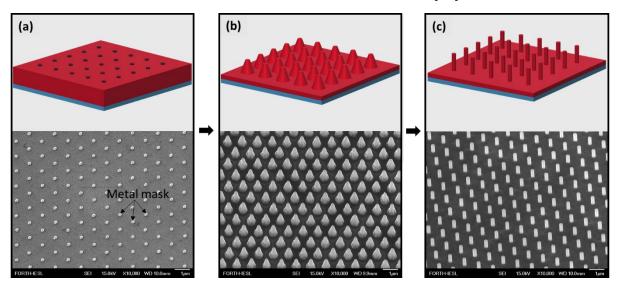

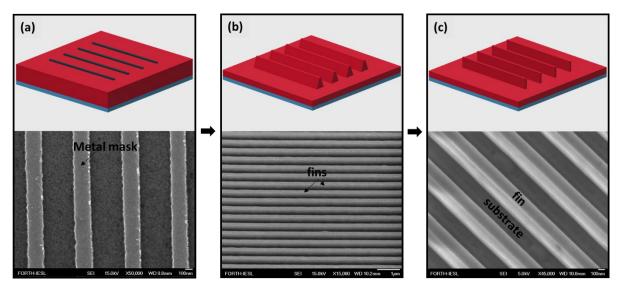

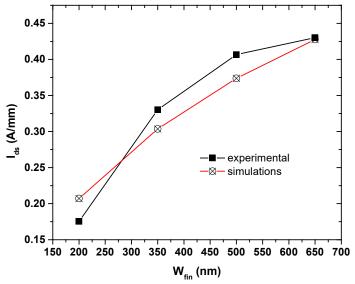

The difficulties to develop a well-controlled SAG process for GaN NWs and nanofins, within a reasonable time frame, shifted our research interest to a top-down process for their formation from GaN-based films, using three processing steps: nanopatterning by electron-beam lithography (e-beam), reactive-ion etching (RIE) and anisotropic wet-chemical etching, based on a Tetramethylammonium hydroxide (TMAH) solution. The TMAH treatment removes the plasma damage and smoothens the lateral surface of the RIE-formed nanostructures, resulting to very steep and uniform GaN-based NWs and nanofins.

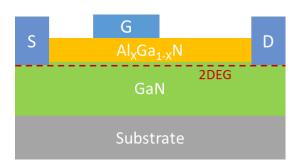

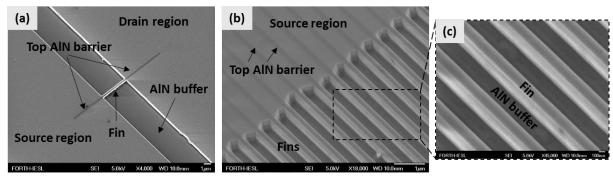

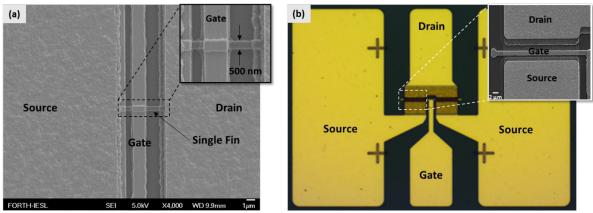

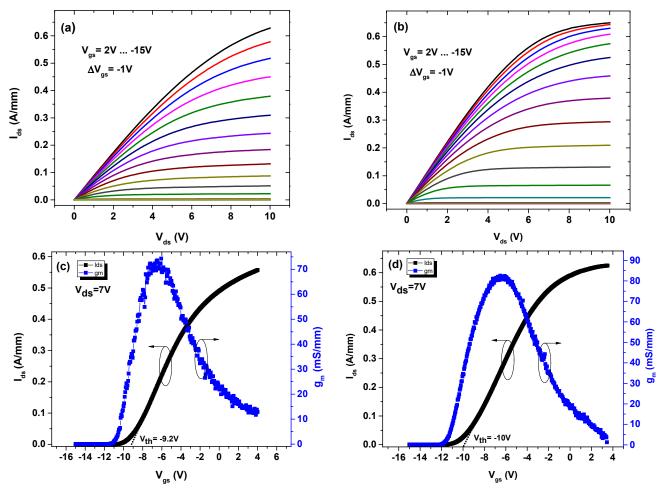

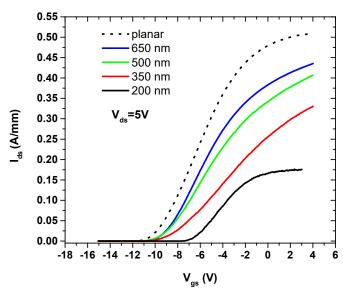

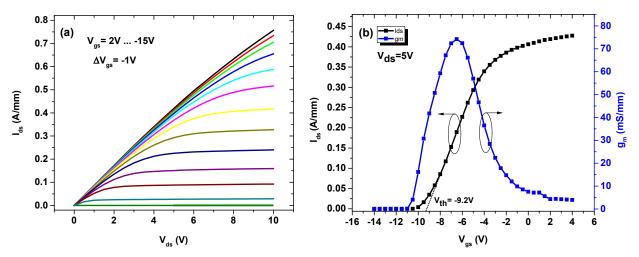

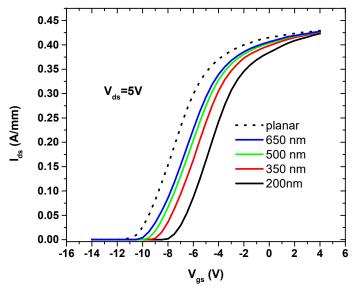

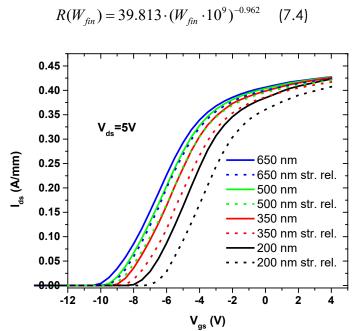

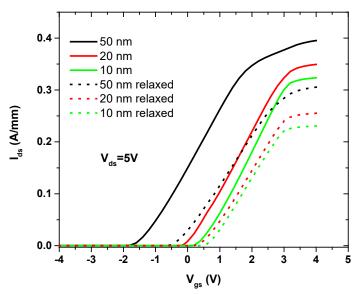

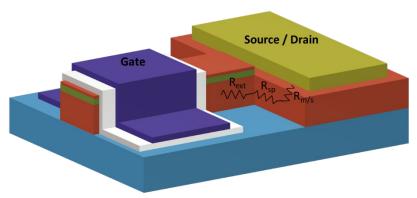

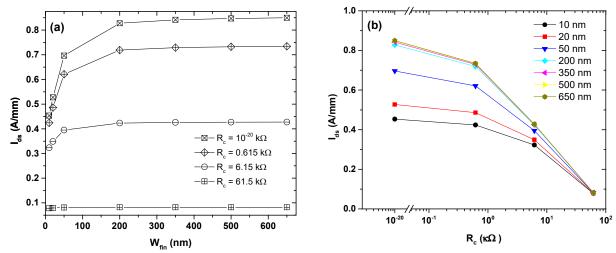

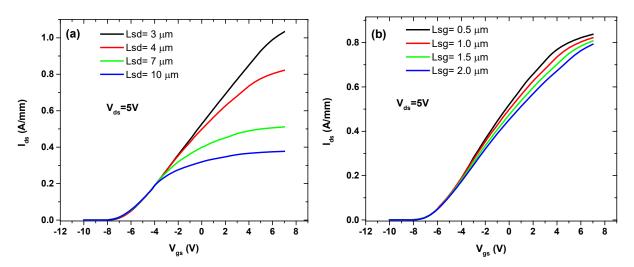

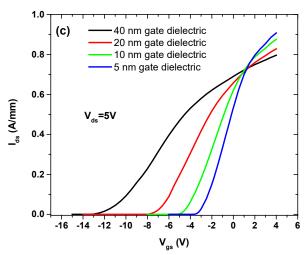

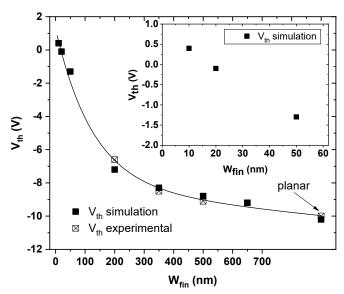

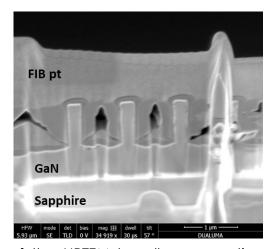

The research on FinFETs was focused on the exploitation of the two-dimensional electron gas (2DEG) channel of an AIN/GaN/AIN double barrier heterostructure, which has been proposed and analyzed previously by the lab, for planar High Electron Mobility Transistors (HEMTs). Transistors with metal-oxide-semiconductor (MOS) tri-gate around a fin-shaped channel (MOS-FinHEMTs) were investigated by combining device simulations and experimental device fabrication and characterization. A top-down process was used for the formation of AIN/GaN/AIN nanofins. Single-fin MOS-FinHEMT devices were fabricated for the first time, with fin width (W<sub>fin</sub>) of 200, 350, 500 and 650 nm. Multi-fin MOS-FinHEMT devices, with channel consisting of 70 fins with W<sub>fin</sub> = 200 nm, and conventional planar gate MOS-HEMTs, were also fabricated for comparison. The dependence of the threshold voltage (V<sub>th</sub>) and the maximum drain-source current (I<sub>ds,max</sub>) on the fin width (Wfin), as well as the effects of ohmic contact resistance, gate-drain and source-gate distance and of the Al<sub>2</sub>O<sub>3</sub> gate dielectric thickness (t<sub>ox</sub>), were determined. Fabricated single-fin MOS-FinHEMT devices, with tox= 20 nm, exhibited a positive shift of V<sub>th</sub>, in comparison to a reference planar-gate device, ranging from +0.8 V for W<sub>fin</sub> = 650 nm to +3.4 V for W<sub>fin</sub> = 200 nm, due to lateral depletion of the channel by the gate contacts on the fin sidewalls. Device simulations were used to reproduce the experimental  $V_{th}$  values and also to predict the  $V_{th}$  of devices with narrower fins, down to  $W_{fin}=10$  nm. The boundary for normally-off operation ( $V_{th}=0$  V) was determined for  $W_{fin}=17$  nm that may increase up to 31 nm, if the tensile strain of the top AIN barrier in the fin nanostructure is elastically relaxed. A reduction of maximum drain-source current per top gate width (I<sub>ds,max</sub>/W<sub>g</sub>), with decreasing W<sub>fin</sub> in the range of 200-650 nm, may result from increased ohmic contact resistance. However, for narrower fins, Ids,max/Wg was predicted to decrease significantly with decreasing W<sub>fin</sub>, due to the lateral electron depletion in the

nanofins. The  $I_{ds,max}/W_g$  will also decrease with increasing distance between the source, gate and drain contacts for any  $W_{fin}$ . The  $V_{th}$  and  $I_{ds,max}/W_g$  values were also calculated for  $Al_2O_3$  thickness in the range of 5 to 40 nm.

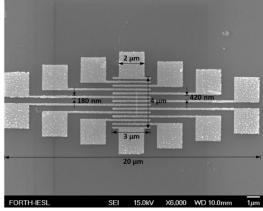

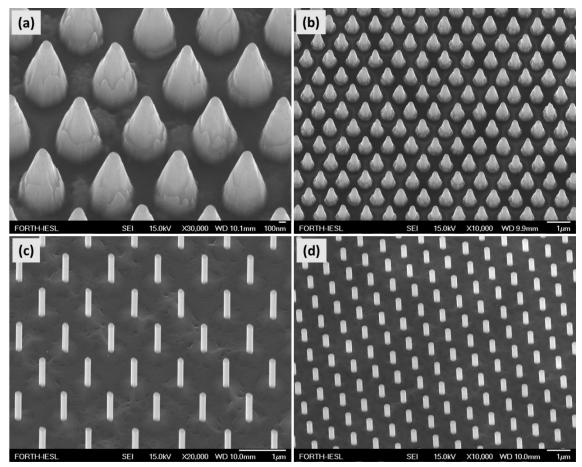

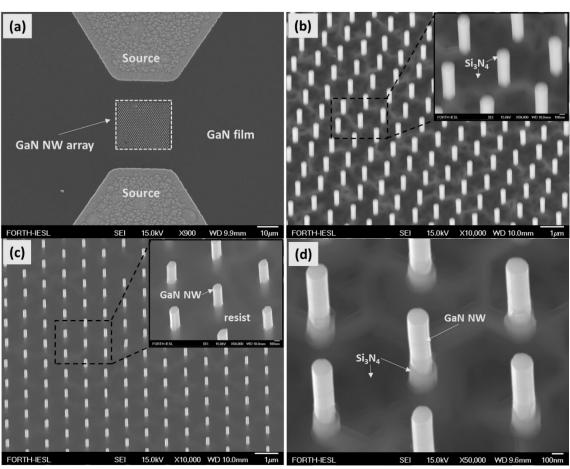

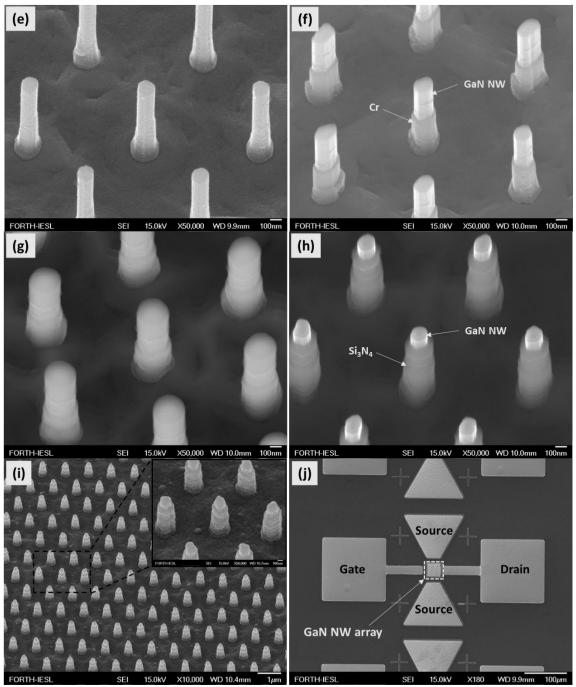

Finally, GaN V-NW FETs with a Schottky barrier gate (V-NW MESFETs) were fabricated for the first time, using a top-down process to form GaN NWs from a PAMBE GaN epilayer on sapphire (0001) substrate. A nanofabrication process with comprehensive design of all processing steps was developed and validated with the demonstration of GaN V-NW MESFETs, consisting of an array of 900 (30x30) GaN NWs with a diameter of 100 nm and all-around gate length of 250 nm. DC I-V characteristics exhibited normally-off operation and threshold voltage of +0.4 V, due to electron depletion region from the all-around Schottky barrier. The I-V characteristics were dominated by the high source and drain access resistances resulting from electron depletion due to Fermi level pinning by surface states at the lateral GaN NW sides. A maximum drain-source current density (J<sub>ds,max</sub>) of 330 A/cm² and maximum transconductance (g<sub>m,max</sub>) of 285 S/cm² were determined from I-V measurements. Optimization of the doping profile in the GaN epilayers, surface passivation and a self-aligned gate process technology could address the high access resistance issue.

Overall, the research carried out within this thesis, on both GaN-based FinHEMTs and V-NW MESFETs has established critical scientific understanding and technological know-how for achieving further progress in the future. Essential insight was gained for the performance capabilities of these devices, as well as the influence of nanoelectronic device design, nanofabrication processes and material parameters.

## **Acknowledgements**

First of all, I would like to express my sincere gratitude to my advisor, Prof. Alexandros Georgakilas, for giving me the opportunity to work on such an interesting and inspiring project, and for his continuous support and guidance throughout my PhD studies. I would like also to thank Dr. George Konstantinidis, the research director of Microelectronics Research Group of IESL/FORTH, for giving me the chance to work at the processing laboratory into the IESL/FORTH clean room facility, as well as for his significant support and help.

I am grateful to all current and former members of the Microelectronics Research Group and Physics Department of University of Crete, for creating a positive work environment and for their valuable contribution and assistance over these years. Many thanks to the growers: Dr. Adam Adikimenakis, Dr. Savvas Eftychis and Dr. Jann Kruse, for providing the PAMBE samples. In particular, to Dr. Adam Adikimenakis for the growth of GaN-based films and selective area growth of GaN nanowires on SiO<sub>2</sub>/GaN/Si patterned substrates by PAMBE, and to Dr. Savvas Eftychis and Dr. Jann Kruse for the spontaneous growth of GaN nanowires and selective area growth of GaN nanowires on SiO<sub>2</sub>/Si patterned substrates by PAMBE. I also want to express my gratitude to the processing laboratory team: Antonis Stavrinidis, Thanassis Kostopoulos and George Stavrinidis for their constant support and training in the clean room activities, and for generating a friendly environment at the processing laboratory. Many thanks to Antonis Stavrinidis also for the e-beam process of devices and the great collaboration we had during these processes.

I have especially to thank Katerina Tsagaraki for taking SEM images in every device fabrication step and for XRD characterization of the samples. I am also grateful to Dr. Fabrice Iacovella for taking part of the SEM images for the fabrication of vertical GaN nanowire MESFETs. Without their help, this work would have not been possible. Many thanks to Maria Kayambaki for her assistance and technical support in the electrical characterization laboratory and to Maria Androulidaki for the PL characterization of the samples. Additionally, I would like to acknowledge Dr. George Deligeorgis, as he always made himself available whenever I needed his help or suggestion. I would also like to express my gratitude to Michalis Sfendourakis and Nikos Papadakis, the technical staff of the group. They did more than just maintaining equipment.

I am grateful to our collaborators from NCSR Demokritos: Pascal Normand, Panagiotis Dimitrakis and Antonis Olziersky, for their contribution in the preparation of SiO<sub>2</sub>/Si patterned samples. I am also grateful to Dr. Dominique Mailly of the Centre National de la Recherche Scientifique (CNRS), Marcoussis, Paris, France for the preparation of SiO<sub>2</sub>/GaN/Si patterned samples. Many thanks also to our collaborators from MIND-IN2UB, University of Barcelona: G. Martín, S. Estradé and Prof. F. Peiró, for HRTEM characterization of top-down formed vertical GaN nanowires.

I am deeply thankful to colleagues, who have become very good friends of mine over these years: Christos Zervos, Stelios Kazazis, Manos Vassakis, Savvas Germanis,

Pramod Kumar Sharma, Alexandros Tzimis, Athanasios Margiolakis and Manolis Mavrotsoupakis, are only some of them. Finally, special thanks to my family, my parents Kyriako and Ioanna and my sister Maria, for their continuous support.

This research work has been initiated in the project MIS 377284 'Nanowire' of the program THALES, co-financed by the European Union (European Social Fund—ESF) and Greek national funds through the Operational Program "Education and Lifelong Learning" of the National Strategic Reference Framework (NSRF). It was continued by partial support from IESL/FORTH, including the projects 'AENAO' (MIS 5002556), 'INNOVATION-EL' (MIS 5002772) and 'RADAR' (MIS 5032784). The SiO<sub>2</sub>/GaN/Si nanopatterning research work received funding from the EU-H2020 programme under grant agreement No 654360 having benefitted from the access provided by CNRS within the framework of the NFFA-Europe Transnational Access Activity.

# **Table of Contents**

| Abstract                                            | III  |

|-----------------------------------------------------|------|

| Acknowledgements                                    | VI   |

| Table of Contents                                   | VIII |

| Abbreviations                                       | XI   |

| Chapter 1: Introduction                             | 1    |

| 1.1 The roadmap to GaN NWs and nanofins             | 1    |

| 1.2 The roadmap to next generation devices          | 3    |

| 1.3 Motivation and overview of this work            | 4    |

| References                                          | 6    |

| Chapter 2: Properties of III-Nitride semiconductors | 10   |

| 2.1 Structural properties                           | 10   |

| 2.2 Polarity and polarization effects               | 12   |

| 2.3 III-Nitride based heterostructures              | 14   |

| References                                          | 17   |

| Chapter 3: Micro- and nanofabrication techniques    | 19   |

| 3.1 Introduction                                    | 19   |

| 3.2 Photolithography                                | 19   |

| 3.3 Electron beam lithography                       | 20   |

| 3.4 Reactive ion etching                            | 21   |

| 3.5 Chemical vapor deposition                       | 22   |

| 3.6 Atomic layer deposition                         | 23   |

| 3.7 Plasma ashing                                   | 24   |

| 3.8 Electron beam evaporation                       | 24   |

| 3.9 Rapid thermal annealing                         | 25   |

| 3.10 Wet – chemical treatment                       | 26   |

| References                                          | 27   |

| Chapter 4: Fundamentals of device characteristics   | 29   |

| 4.1 Introduction                                    | 29   |

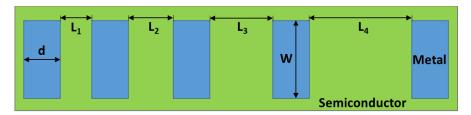

| 12 Transmission line model structures               | 20   |

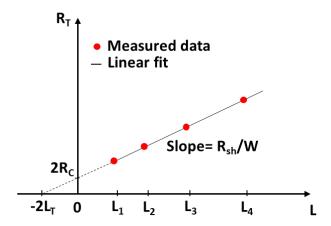

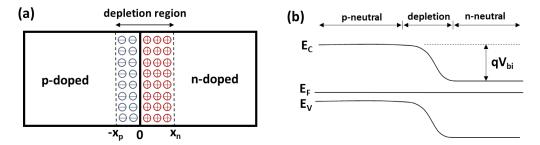

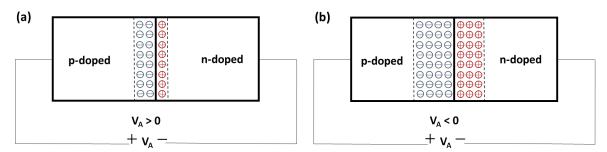

| 4.3 p-n junction diode                                                    | 31 |

|---------------------------------------------------------------------------|----|

| 4.3.1 Thermal equilibrium                                                 | 31 |

| 4.3.2 Forward and reverse bias                                            | 34 |

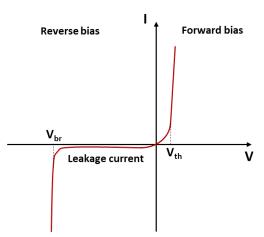

| 4.3.3 Current-Voltage characteristics                                     | 34 |

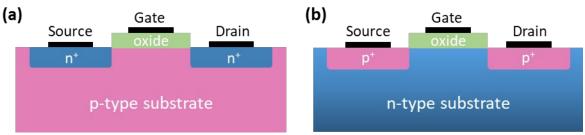

| 4.4 Metal oxide semiconductor field effect transistor                     | 35 |

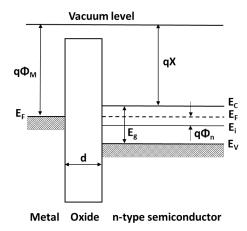

| 4.4.1 Metal-oxide-semiconductor capacitor                                 | 35 |

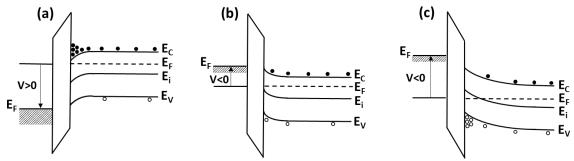

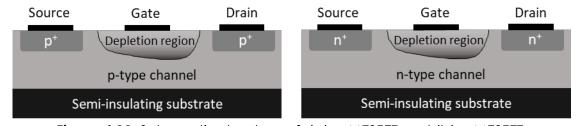

| 4.4.2 Operational characteristics of Si MOSFETs                           | 37 |

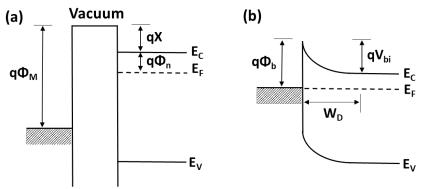

| 4.5 Metal semiconductor field effect transistor                           | 39 |

| 4.5.1 Schottky junctions                                                  | 39 |

| 4.5.2 Operational characteristics of MESFETs                              | 40 |

| 4.6 High electron mobility transistor                                     | 41 |

| 4.7 Current-Voltage DC characteristics of transistors                     | 41 |

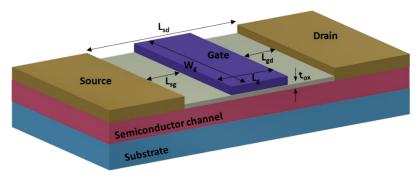

| 4.7.1 Geometrical parameters of transistors                               | 42 |

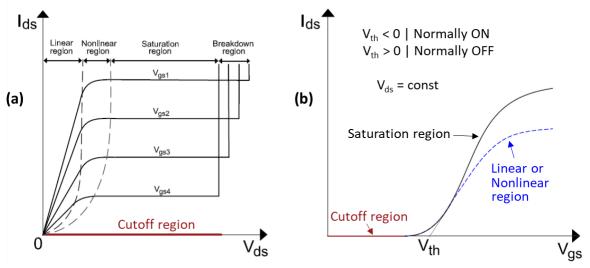

| 4.7.2 Output and transfer I-V characteristics                             | 42 |

| References                                                                | 44 |

| Chapter 5: Growth and formation of GaN NWs and fins                       | 46 |

| 5.1 Introduction                                                          | 46 |

| 5.2 Spontaneous growth of GaN NWs                                         | 46 |

| 5.3 Selective area growth of GaN NWs and fins                             | 47 |

| 5.3.1 GaN growth on SiO <sub>2</sub> /Si patterned substrates             | 48 |

| 5.3.2 GaN growth on SiO <sub>2</sub> /GaN/Si patterned substrates         | 50 |

| 5.3.3 Top-down formation of GaN NWs and GaN-based Fins                    | 51 |

| References                                                                | 54 |

| Chapter 6: Bottom-up GaN nanowire devices                                 | 56 |

| 6.1 Introduction                                                          | 56 |

| 6.2 Surface depletion effects in GaN NWs                                  | 56 |

| 6.3 Horizontal NW-devices of individual GaN nanowires                     | 59 |

| 6.3.1 Suspension of GaN nanowires onto the SiO <sub>2</sub> /Si substrate | 60 |

| 6.3.2 Fabrication of horizontal GaN nanowire devices                      | 61 |

| 6.3.3 Results and discussion                                              | 66 |

| 6.4 Vertical p-Si/n-GaN NW heterojunction diodes                          | 70 |

| 6.4.1 Fabrication of p-Si/n-GaN NW heterojunction diodes                  | 70 |

| 6.4.2 Results and discussion                                              | 71 |

| References                                                   | 73  |

|--------------------------------------------------------------|-----|

| Chapter 7: Top-down AIN/GaN/AIN MOS-FinHEMTs                 | 75  |

| 7.1 Introduction and motivation                              | 75  |

| 7.2 Polarization effects in AIN/GaN/AIN heterostructures     | 76  |

| 7.3 Epitaxial growth and material characterization           | 78  |

| 7.4 Device fabrication                                       | 79  |

| 7.5 DC characterization of devices                           | 81  |

| 7.6 Simulations of devices                                   | 83  |

| 7.6.1 Scaling the fin width                                  | 85  |

| 7.6.2 Effect of S/D contact resistance                       | 88  |

| 7.6.3 Effects of contact distances and oxide thickness       | 90  |

| 7.7 Comparative study and overall discussion                 | 92  |

| 7.8 Conclusions                                              | 95  |

| References                                                   | 96  |

| Chapter 8: Top-down GaN vertical NW MESFETs                  | 100 |

| 8.1 Introduction and motivation                              | 100 |

| 8.2 Formation of top-down GaN vertical NWs                   | 101 |

| 8.3 HRTEM characterization of GaN NW arrays                  | 103 |

| 8.4 Fabrication of GaN Vertical-NW MESFETs                   | 105 |

| 8.5 Results and discussion                                   | 109 |

| 8.6 Conclusions                                              | 113 |

| References                                                   | 114 |

| Chapter 9: Conclusions and future perspectives               | 118 |

| 9.1 Conclusions                                              | 118 |

| 9.2 Future perspectives                                      | 121 |

| References                                                   | 123 |

| Appendix: Publications                                       | 124 |

| A.1 PUBLICATIONS IN JOURNALS                                 | 124 |

| A.2 PUBLICATIONS IN PROCEEDINGS OF INTERNATIONAL CONFERENCES | 125 |

| A.3 PRESENTATIONS IN INTERNATIONAL CONFERENCES               | 126 |

#### **Abbreviations**

ALD Atomic layer deposition

Al Aluminum

AlGaN Aluminum gallium nitride

AlN Aluminum nitride Al<sub>2</sub>O<sub>3</sub> Aluminum oxide

APCVD Atmospheric pressure chemical vapor deposition

Au Gold

BHF Buffered hydrofluoric acid

Cr Chromium

CVD Chemical vapor deposition

d<sub>crit</sub> Critical diameter

d<sub>eff</sub> Effective diameter

DI Deionized

Energy band-gap e-beam Electron beam

EBL Electron beam lithography

FET Field-effect transistor

FIB Focused-ion beam

Fin-shaped channel field-effect transistor

FWHM Full width at half maximum

gm Transconductance

GAA Gate all-around

GaN Gallium nitride

Ge Germanium

g<sub>m,max</sub> Maximum transconductance

HEMT High electron mobility transistor

HRTEM High resolution transmission electron microscopy

HVPE Hybrid vapor phase epitaxy I<sub>ds</sub> Drain to source current

Ids,maxMaximum drain-source currentIds-VdsDC output characteristicsIds-VasDC transfer characteristics

I-V Current-Voltage

InAIN Indium aluminum nitride

InN Indium nitride IR Infrared

IRDS International roadmap for devices and systems

J-V Current density-Voltage KOH Potassium hydroxide

Lg Gate length

LgdGate to drain distanceLsdSource to drain distanceLsgSource to gate distanceLEDLight emitting diode

LGAA Lateral gate-all-around

MESFET Metal semiconductor field-effect transistor

MIS Metal-insulator-semiconductor

ML Monolayer

MOS Metal-oxide-semiconductor

MOSFET Metal oxide semiconductor field-effect transistor

MOVPE Metalorganic vapor phase epitaxy

N<sub>A</sub> Acceptor concentration Donor concentration

n<sub>s</sub> Sheet electron concentration

Ni Nickel NW Nanowire

PAMBE Plasma assisted molecular beam epitaxy

P<sub>PZ</sub> Piezoelectric polarization P<sub>SP</sub> Spontaneous polarization

P<sub>T</sub> Total polarization PL Photoluminescence

PR Photoresist

$\begin{array}{ll} \text{PVD} & \text{Physical vapor deposition} \\ Q_{if} & \text{Fixed positive charge} \\ q\Phi_B & \text{Schottky barrier height} \\ R_C & \text{Contact resistance} \end{array}$

R<sub>crit</sub> Critical radius

R<sub>ext</sub> Extension resistance

R<sub>m/s</sub> Metallization semiconductor resistance

R<sub>sem</sub> Semiconductor resistance

Sheet resistance  $R_{sh}$ Spreading resistance  $R_{sp}$ Total resistance  $R_T$ RF Radio frequency RIE Reactive ion etching Rapid thermal annealing **RTA** SAG Selective area growth SCL Space charge limited

SEM Scanning electron microscope

Si Silicon

$\begin{array}{ccc} Si_3N_4 & Silicon nitride \\ SiO_2 & Silicon dioxide \\ t_{ox} & Oxide thickness \end{array}$

TD Threading dislocation

Ti Titanium

TLM Transmission line model

TMAH Tetramethylammonium hydroxide

UV Ultraviolet

u-GaN undoped GaN

V<sub>bi</sub> Built-in potential

V<sub>ds</sub> Drain to source voltage V<sub>gs</sub> Gate to source voltage

V<sub>th</sub> Threshold voltage V-NW Vertical nanowire

VGAA Vertical gate all-around Wdep Depletion region width

$\begin{array}{lll} W_{\text{fin}} & & \text{Fin width} \\ W_{\text{g}} & & \text{Gate width} \\ X_{\text{s}} & & \text{Electron affinity} \\ Z_{\text{nO}} & & \text{Zinc oxide} \end{array}$

$\Delta E_{C}$  Conduction band offset  $\Delta E_{V}$  Valence band offset

ε<sub>r</sub> Dielectric constant or permittivity

μ mobility

ρcSpecific contact resistivityσintInterface sheet chargeΦMMetal work function2-DTwo-Dimensional

2DEG Two dimensional electron gas

3-D Three-Dimensional

# Chapter 1

#### Introduction

Gallium Nitride (GaN) and related III-Nitride semiconductors exhibit fundamental advantages, such as wide direct band gap, excellent electron transport properties, high breakdown voltage and high thermal conductivity [1-2]. The large spontaneous and piezoelectric polarization effects in III-Nitrides [1–2] can be exploited for the formation of a high density two-dimensional electron gas (2DEG) channel at an Al<sub>1-x</sub>Ga<sub>x</sub>N/GaN [3] or In<sub>1-x</sub>Al<sub>x</sub>N/GaN [4] heterointerface. In addition, GaN is a promising candidate to replace silicon (Si) for next-generation n-channel transistors of digital integrated circuits [5]. Device simulations of Chowdhury N. et al. [5] predict that n-type GaN nanowire (NW) field-effect transistors (FETs) with gate length of 5 nm would outperform Si and other semiconductors, due to the relatively higher electron effective mass and lower permittivity of GaN. These devices will operate at fully ballistic transport regime [5]. Chowdhury N. et al. [5] determined that if the transistors are tuned for the same off current then GaN will provide the lowest threshold voltage (V<sub>th</sub>) and thus highest on current for the same supply voltage (Vcc). This is attributed to reduction of the source to drain direct tunneling by the relatively higher effective mass and better short-channel characteristics due to the lower permittivity of GaN [5]. It is also worth mentioning that the 2014 Nobel Prize in physics was awarded jointly to Isamu Akasaki, Hiroshi Amano and Shuji Nakamura, acknowledging their work on III-Nitrides for efficient blue Light Emitting Diodes (LEDs) [6].

#### 1.1 The roadmap to GaN NWs and nanofins

The earliest mention of synthesis of GaN is traced back to 1932 by Johnson W. C. et al. [7], through a direct reaction between gallium and ammonia. Maruska H. P. and Tietjen J. J. [8] reported in 1969 the first epitaxial growth of GaN film on sapphire substrate by Hybrid Vapor Phase Epitaxy (HVPE). Poor crystal quality and high background electron concentration were observed. The first high-quality Metalorganic Vapor Phase Epitaxial (MOVPE) growth of GaN film on sapphire substrate, was reported by Amano H. et al. [9] in 1985, using an AlN buffer layer. This group also reported [10] in 1989, the first p-type doped GaN film by MOVPE, using Mg for doping and a low-energy electron-beam irradiation (LEEBI) treatment for lowering the resistivity and remarkable enhancement of the Photoluminescence (PL) efficiency [10]. They also used this process to develop a p-n GaN junction LED [10], which enabled the fabrication of Nitride-based optoelectronic devices [11].

Since the late 1990s, the pioneering work of the groups of Kishino K. [12] and Calleja E. [13] triggered the scientific interest to self-assembled (spontaneously) grown GaN nanowires (NWs). Spontaneous growth of GaN NWs [12–13] is a random process with

large deviations in shape and size of NWs, which was the main drawback for most device applications (e.g. vertical NW FETs). Therefore, a position-controlled growth was needed. The first selective area growth (SAG) of arbitrary shape GaN structures with Molecular Beam Epitaxy (MBE), was reported in 2000 by Gupta V.K. et al. [14], using a SiO<sub>2</sub> mask deposited on a GaN film, previously grown on a sapphire substrate. Two years later, Kawasaki K. et al. [15] used this technology for the formation of vertical SAG GaN NWs by MBE using a SiO<sub>2</sub> mask with circular openings. It took few years for new publications of SAG of NWs [16] and for the exploitation of this technique in the formation of GaN nanofins [17]. Kishino K. et al. [17] used a Ti mask that fully covered a Si substrate, while nanostripe window openings were patterned on the metallic mask with conventional nanofabrication techniques.

Nowadays, GaN NWs and nanofins are promising elemental building blocks in nanoelectronic and nanophotonic applications [18–21], due to their reduced dimensionality and high aspect ratio that could enhance the miniaturization of devices and lead to high device density, decreased power consumption and high operation frequency [18–21]. SAG technology [14–17, 22, 23] is increasingly employed to combine the high crystal quality of spontaneously grown GaN NWs with precise dimensioning and positioning, critical parameters for the fabrication of devices (e.g. vertical GaN NW transistors). However, the understanding of growth mechanisms and optimization of the patterned mask in SAG GaN technology is still under discussion in the literature [22–23]. Dielectric or metallic masks [14–17, 22, 23] are used and studied in order to eliminate the nucleation on the mask outside of the patterned window areas, while the influence of unmasked growth substrate is also investigated, with bare Si and GaN pseudosubstrates to be widely used [14–17, 22, 23]. In contrast to the case of SAG of GaN NWs, only few works for SAG of GaN nanofins are reported [17, 23], indicating that apart from the significant achievements reported in early years, further research efforts are needed.

The complexity of SAG techniques, combined with poor results [22–23], motivated the investigation of top-down approaches in order to improve the material quality of the formed GaN nanostructures [24], which is maybe the main drawback of these techniques. Top-down approaches for the formation of GaN-based NWs and nanofins are based on three processing steps: nanopatterning by electron-beam lithography (e-beam), reactive-ion etching (RIE) and/or anisotropic wet-chemical etching [25–32]. They have been used, since the early 2010s, for the formation of GaN [19, 27, 30] and Al<sub>1-x</sub>Ga<sub>x</sub>N/GaN [19, 30–32] nanofins for fabrication of transistor devices (FinFETs). A post RIE wet chemical-etching treatment (TMAH- or KOH-based) is widely used to remove the plasma damage and to smooth the lateral surface of the RIE-formed nanofins [19, 30, 32]. This wet chemical treatment was recently employed by Jo Y.-W. et al. [25] for the formation of top-down GaN NWs and the first demonstration of GaN-based vertical NW FETs [25]. Up to now, there has been a limited amount of experimental work on n-type GaN vertical NW (V-NW) FETs [25–29].

#### 1.2 The roadmap to next generation devices

Moore's law [33] held true for over 50 years as the way to explain ongoing improvements in transistor scaling, associated with doubling the number of transistors every two years in a dense integrated circuit. The prospects for low power FETs for logic in the next 20 years, are described in the 2018 "International Roadmap for Devices and Systems (IRDS)" [34–35] and predict that Moore's law will keep alive.

According to IRDS [34–35] the scaling of devices is divided into three time periods. The first generation, the "geometrical scaling" lasted from 1975 to 2002 and includes reduction of the physical dimensions of planar transistors in conjunction with improved performance. The next generation was named "equivalent scaling" started at 2003 and will last up to 2024. The goal in this period is the reduction of horizontal dimensions in conjunction with the use of new materials and physical effects. New vertical structures will replace the planar ones. The future generation was named "3D Power Scaling" by the IRDS to include all the challenges facing the semiconductor and electronics industries in the next 15 years. In this period (2025-2040), vertical device structures will dominate offering heterogeneous integration in conjunction with reduced power consumption. In particular, lateral nanowire FET devices – corresponding to the Lateral Gate-All-Around (LGAA) technology – will be introduced in 2022 and will initially co-exist with the last period of the (Tri-Gate) FinFET technology. Vertical NW GAA (VGAA) technology is expected to start in 2027 and will dominate until 2034 together with 3D integration [34–35].

III-V NWs are anticipated to be used for n-channel MOSFETs from 2022, together with strained Si and Ge [34–35]. The use of III-V channels is considered necessary to deliver high performance logic chips with low power consumption [36]. However, the need for a careful holistic optimization is also anticipated, taking into account both the channel material parameters and the parameters and architecture of devices [34–35].

Up to date, FinFETs and vertical NW GAA (VGAA) technology have already gained significant attention, in consequence with the IRDS roadmap predictions, due to the enhanced electrostatic control of the gate on the channel that results to significant improvement of leakage current and current on/off ratio, in comparison to planar gate devices [25–32]. Intel and IBM lead the way in FinFET technology. Intel has been manufacturing silicon FinFETS in volume since 2011 starting with its 22nm Ivy Bridge and later Haswell micro-architecture processors using a bulk silicon approach [37]. The 14 nm micro-architecture processors became Intel's 2nd generation Si FinFET technology [38] with improved performance and reduced leakage power. On the other hand, IBM has taken a more experimental approach using silicon-on-insulator (SOI) substrates to simplify the manufacturing process and allow lower voltage operation. The FinFET process technology developed for IBM server processors at the 14-nm node [39] offers deeptrench embedded dynamic random access memory (eDRAM), multiple work-function FinFET devices and a hierarchical 17-level metal back-end of line. In 2015, IBM announced the fabrication of 7-nanometer node FinFETs [40] using silicon-germanium channels.

Beyond tri-gate devices, GAA technologies are promising candidates to extend the gate length and gate pitch scaling beyond what is possible with FinFETs. In 2017, IBM and its research alliance partners GlobalFoundries and Samsung have developed a process to build 5 nanometer (nm) chips [41] using a new gate all- around architecture that employs stacked silicon nanosheets, providing for better leakage control at smaller scales. At 2018 IEEE International Electron Devices Meeting (IEDM), IMEC reported significant progress in process enabling the introduction of GAA transistors with vertically stacked Ge NWs and nanosheets [42]. The VGAA nanowire technology instead of stacked NW technology is another promising way for ongoing device optimization. The earliest mention of Si NW VGAA transistor is traced back to 1988 by the inspiring work of the group of Masuoka F. [43]. This technology could be considered as the ultimate scaling of Si nanoelectronic FETs and further advancement should involve a new channel material. However, it took more than 15 years for new publications of NW VGAA transistors using a Si [44] or ZnO [45] NW channel. The first III-V (InAs) NW VGAA transistor was reported in 2006 [46], while the first demonstration of GaN NW VGAA transistor was reported recently in 2015 [25] by a top-down approach, which combines conventional nanofabrication techniques and wet etching.

The transition from low power (digital) to high power FET devices can be easily achieved by increasing the number of nanofins or lateral/vertical nanowires in FinFETs and nanowire FETs, respectively. Thus, the channel of these devices consisting of parallel connections of several fins or nanowires. Recently, Zhang Y. et al. [47] have demonstrated a GaN-based multi-fin channel FinFET device with breakdown voltage of over 1200 V, extremely high ON current of over 25 kA/cm² and low OFF current below 10-4 A/cm² at 1200 V. Therefore, V-NW transistors and FinFETs are promising nanoelectronic structures for both low power and high power device applications.

#### 1.3 Motivation and overview of this work

At University of Crete, the MIS 377284 project: "Spontaneous growth, properties and devices of III-V semiconductor nanowires" (Nanowire), of the THALES program, was initiated in Fall 2012, to create fundamental understanding and develop a new NW device technology. A very ambitious target of the project was the development of GaN vertical NW FET (V-NW FET) device technology and this has been the core activity of the present PhD thesis. The last 4 years, GaN V-NW FET technology has gained significant research attention for fabrication of next generation devices, in consequence with the IRDS roadmap predictions that V-NW FET technology is expected to follow the FinFET technology and to dominate until 2034 together with 3D integration for fabrication of nanoelectronic structures. Fabrication and physical analysis of horizontal NW devices was also carried out in order to determine and understand the fundamental GaN NW properties. The spontaneously grown n-GaN NWs on p-Si (111) substrates were utilized in fabrication of p-Si/n-GaN NW heterojunction diodes, indicating a promising candidate for integrating GaN NW solar cells and light emission devices on Si substrates. Finally, research on GaN-based FinHEMTs, processed by a double barrier AlN/GaN/AlN

heterostructure, was undertaken as a technologically and scientifically intermediate device structure, bringing the know-how and understanding of planar GaN HEMTs with GaN NW transistors.

The manuscript of this dissertation is subdivided as follows: Chapter 2 briefly covers the essential background on III-Nitride semiconductors. Their fundamental structural properties and the role of polarity/polarization effects in formation of III-Nitride based heterostructures, are discussed. Chapter 3 describes the principal micro- and nanofabrication techniques used in this work, including photolithography, e-beam lithography, reactive ion etching, chemical vapor deposition, atomic layer deposition, plasma ashing, electron beam evaporation, rapid thermal annealing and wet chemical treatment. Chapter 4 focuses on the basic device operation and electrical DC characteristics of all kinds of devices fabricated in this thesis, including TLMs, p-n diodes, MOSFETs, MESFETs and HEMTs. A conventional planar geometry is assumed. Chapter 5 briefly presents the experimental techniques used in this work for spontaneous growth or top-down formation of GaN-based NWs and nanofins. Chapter 6 focuses on the evaluation and understanding of size effects on the conductivity of bottom-up grown GaN NWs on Si (111) substrates and the fabrication of GaN-based vertical NW diodes grown on p-Si (111) substrates by PAMBE. Chapter 7 demonstrates experimental and modeling insights for scaling the channel width of fin-shaped AIN/GaN/AIN MOS-FinHEMTs. Chapter 8 presents an innovative concept of fabrication of Schottky barrier gate normally-off GaN vertical NW MESFETs by a top-down approach. Comprehensive description of all fabrication steps and the DC characteristics of the fabricated devices, are reported. Finally, **Chapter 9** concludes the results obtained in this work and provides an outlook to future research work.

#### References

- [1] D. Ueda, "Properties and Advantages of Gallium Nitride", Chapter 1 in "Power GaN Devices Materials, Applications and Reliability", Springer, 2017.

- [2] S. M. Sze and K. K. Ng, "Physics of Semiconductor Devices", 3rd ed., Wiley, 2006.

- [3] J. P. Ibbetson, P. T. Fini, K. D. Ness, S. P. DenBaars, J. S. Speck and U. K. Mishra, "Polarization effects, surface states, and the source of electrons in AlGaN/GaN heterostructure field effect transistors", Appl. Phys. Lett., vol. 77, no. 2, p. 250, 2000.

- [4] J. Kuzmik, "Material and device issues of InAlN/GaN heterostructures", ASDAM 2012 Conf. Proc., p. 45, 2012.

- [5] N. Chowdhury, G. Iannaccone, G. Fiori, D. A. Antoniadis and T. Palacios, "GaN nanowire n-MOSFET with 5 nm channel length for applications in digital electronics", IEEE Electron Device Lett., vol. 38, no. 7, p. 859, 2017.

- [6] "2014 Nobel Prize", Available online: https://www.nobelprize.org/prizes/physics/2014/summary/.

- [7] W. C. Johnson, J. B. Parson and M. C. Crew, "Nitrogen Compounds of Gallium. III", J. Phys. Chem., vol. 36, p. 2651, 1932.

- [8] H. P. Maruska and J. J. Tietjen, "The preparation and properties of vapor-deposited single-crystal-line GaN", *Appl. Phys. Lett.*, vol. 15, no. 10, p. 327, 1969.

- [9] H. Amano, N. Sawaki, I. Akasaki and Y. Toyoda, "Metalorganic vapor phase epitaxial growth of a high quality GaN film using an AlN buffer layer", *Appl. Phys. Lett.*, vol. 48, no. 5, p. 353, 1986.

- [10] H. Amano, M. Kito, K. Hiramatsu and I. Akasaki, "P-type conduction in Mg-doped GaN treated with low-energy electron beam irradiation (LEEBI)", *Jpn. J. Appl. Phys.*, vol. 28, no. 12 A, p. L2112, 1989.

- [11] M. Razeghi and M. Henini, "Optoelectronic Devices: III Nitrides", Elsevier Science Ltd, 2005.

- [12] M. Yoshizawa, A. Kikuchi, N. Fujita, K. Kushi, H. Sasamoto and K. Kishino, "Self-organization of GaN/AlGaN multi-layer nano-columns on (0001) Al<sub>2</sub>O<sub>3</sub> by RF molecular beam epitaxy for fabricating GaN quantum disks", *J. Cryst. Growth*, vol. 189, no. 1, p. 138, 1998.

- [13] M. A. Sanchez-Garcia, E. Calleja, E. Monroy, F.J. Sanchez, F. Calle, E. Munoz and R. Beresford, "The effect of the III/V ratio and substrate temperature on the morphology and properties of GaN- and AIN-layers grown by molecular beam epitaxy on Si(111)", J. Cryst. Growth, vol. 183, pp. 23, 1998.

- [14] V. K. Gupta, K. L. Averett, M. W. Koch, B. L. Mcintyre and G. W. Wicks, "Selective area growth of GaN using gas source molecular beam epitaxy", *J. Electron. Mater.*, vol. 29, no. 3, p. 322, 2000.

- [15] K. Kawasaki, I. Nakamatsu, H. Hirayama, K. Tsutsui and Y. Aoyagi, "Formation of

- GaN nanopillars by selective area growth using ammonia gas source molecular beam epitaxy", J. Cryst. Growth, vol. 243, pp. 129, 2002.

- [16] S. D. Hersee, X. Sun and X. Wang, "The controlled growth of GaN nanowires", Nano Lett., vol. 6, no. 8, pp. 1808, 2006.

- [17] K. Kishino, T. Hoshino, S. Ishizawa and A. Kikuchi, "Selective-area growth of GaN nanocolumns on titanium-mask-patterned silicon (111) substrates by RF-plasma-assisted molecular-beam epitaxy", *Electron. Lett.*, vol. 44, no. 13, 2008.

- [18] Y. Li, F. Qian, J. Xiang and C. M. Lieber, "Nanowire electronic and optoelectronic devices", *Mater. Today*, vol. 9, no. 10, p. 18, 2006.

- [19] K. S. Im, H. S. Kang, J. H. Lee, S.J. Chang, S. Cristoloveanu, M. Bawedin and J. H. Lee, "Characteristics of GaN and AlGaN/GaN FinFETs", *Solid. State. Electron.*, vol. 97, p. 66, 2014.

- [20] J. C. Johnson, H. J. Choi, K. P. Knutsen, R. D. Schaller, P. Yang and R. J. Saykally, "Single gallium nitride nanowire lasers", *Nat. Mater.*, vol. 1, no. 2, p. 106, 2002.

- [21] X. Liu, Y. Long, L. Liao, X. Duan and Z. Fan, "Large-Scale Integration of Semiconductor Nanowires for High-Performance Flexible Electronics", ACS Nano, vol. 6, no. 3, p. 1888, 2012.

- [22] J. E. Kruse, L. Lymperakis, S. Eftychis, A. Adikimenakis, G. Doundoulakis, K. Tsagaraki, M. Androulidaki, A. Olziersky, P. Dimitrakis, V. Ioannou-Sougleridis, P. Normand, T. Koukoula, Th. Kehagias, Ph. Komninou, G. Konstantinidis and A. Georgakilas, "Selective-area growth of GaN nanowires on SiO<sub>2</sub>-masked Si (111) substrates by molecular beam epitaxy", J. Appl. Phys., vol. 119, no. 22, 2016.

- [23] A. Roshko, M. Brubaker, P. Blanchard, T. Harvey and K. A. Bertness, "Selective area growth and structural characterization of GaN nanostructures on si(111) substrates", *Crystals*, vol. 8, no. 9, 2018.

- [24] M. Conroy, H. Li, V. Z. Zubialevich, G. Kusch, M. Schmidt, T. Collins, C. Glynn, R. W. Martin, C. O'Dwyer, M. D. Morris, J. D. Holmes and P. J. Parbrook, "Self-Healing Thermal Annealing: Surface Morphological Restructuring Control of GaN Nanorods", Cryst. Growth Des., vol. 16, no. 12, p. 6769, 2016.

- [25] Y. W. Jo, D. H. Son, D. G. Lee, C. H. Won, J. H. Seo, I. M. Kang and J. H. Lee, "First demonstration of GaN-based vertical nanowire FET with top-down approach", *Proc. 73rd Annu. Device Res. Conf.*, p. 35, 2015.

- [26] F. Yu, D. Rümmler, J. Hartmann, L. Caccamo, T. Schimpke, M. Strassburg, A. E. Gad, A. Bakin, H.-H. Wehmann, B. Witzigmann, H. S. Wasisto and A. Waag, "Vertical architecture for enhancement mode power transistors based on GaN nanowires", *Appl. Phys. Lett.*, vol. 108, no. 21, p. 213503, 2016.

- [27] Z. Hu, W. Li, K. Nomoto, M. Zhu, X. Gao, M. Pilla, D. Jena and H. G. Xing, "GaN vertical nanowire and fin power MISFETs", proc. 75th Annual Device Res. Conf. (DRC), 2017.

- [28] D. H. Son, Y. W. Jo, J. H. Seo, C. H. Won, K. S. Im, Y. S. Lee, H. S. Jang, D. H. Kim, I. M.

- Kang and J. H. Lee, "Low voltage operation of GaN vertical nanowire MOSFET", Solid. State. Electron., vol. 145, p. 1, 2018.

- [29] G. Doundoulakis, A. Adikimenakis, A. Stavrinidis, K. Tsagaraki, M. Androulidaki, F. Iacovella, G. Deligeorgis, G. Konstantinidis and A. Georgakilas,, "Nanofabrication of normally-off GaN vertical nanowire MESFETs", *Nanotechnology*, vol. 30, no. 28, p. 285304, 2019.

- [30] K. S. Im, C. H. Won, Y. W. Jo, J. H. Lee, M. Bawedin, S. Cristoloveanu and J. H. Lee, "High-Performance GaN-Based Nanochannel With/Without AlGaN/GaN Heterostructure", vol. 60, no. 10, p. 3012, 2013.

- [31] E. Ture, P. Brückner, B. J. Godejohann, R. Aidam, M. Alsharef, R. Granzner, F. Schwierz, R. Quay and O. Ambacher, "High-Current Submicrometer Tri-Gate GaN High-Electron Mobility Transistors with Binary and Quaternary Barriers", *IEEE J. Electron Devices Soc.*, vol. 4, no. 1, p. 1, 2016.

- [32] G. Doundoulakis, A. Adikimenakis, A. Stavrinidis, K. Tsagaraki, M. Androulidaki, G. Deligeorgis, G. Konstantinidis and A. Georgakilas, "Experimental and modeling insight for fin-shaped transistors based on AIN/GaN/AIN double barrier heterostructure", Solid. State. Electron., vol. 158, p. 1, 2019.

- [33] G. M. Moore, "Cramming more components onto integrated circuits", *Electronics*, vol. 38, no. 8, 1965.

- (34) "International Roadmap for Devices and Systems, 2018 Edition, Executive Summary", Available online: https://irds.ieee.org/images/files/pdf/2018/2018IRDS\_ES.pdf.

- [35] "International Roadmap for Devices and Systems, 2018 Edition, More Moore", Available online: https://irds.ieee.org/images/files/pdf/2018/2018IRDS\_MM.pdf.

- [36] J. A. Del Alamo, "Nanometre-scale electronics with III-V compound semiconductors", *Nature*, vol. 479, no. 7373, p. 317, 2011.

- [37] "Intel, IBM Dueling 14nm FinFETS", R. C, Johnson, EE | TIMES (2014), Available online: https://www.eetimes.com/document.asp?doc\_id=1324343#.

- [38] "Intel 14 nm Technology" Available online: https://www.intel.com/content/www/us/en/silicon-innovations/intel-14nm-technology.html.

- [39] S. R. Stiffler, R. Ramachandran, W. K. Henson, N. D. Zamdmer, K. McStay, G. L. Rosa, K. M. Boyd, S. Lee, C. Ortolland and P. C. Parries, "Process technology for IBM 14-nm processor designs featuring silicon-on-insulator FinFETs", IBM J. Res. Dev., vol. 62, p. 111, 2018.

- [40] "IBM Leapfrogs Intel to 7nm", R. C, Johnson, EE | TIMES (2015), Available online: https://www.eetimes.com/document.asp?doc id=1327087.

- [41] "IBM Clears Path to 5nm with Silicon Nanosheets", T. Trader, HPCwire, (2018), Available online: https://www.hpcwire.com/2017/06/05/ibm-clears-path-5nm-beyond-finfet/.

- [42] "Imec Report Progress In Enabling GAA Transistors", Siliconsemiconductor, (2018) Available online: https://siliconsemiconductor.net/article/105944/Imec\_Report\_Progress\_In\_Enabling\_GAA\_Transistors.

- [43] H. Takato, K. Sunouchi, N. Okabe, A. Nitayama, K. Hieda, F. Horiguchi and F. Masuoka, "High performance CMOS surrounding gate transistor (SGT) for ultra high density LSIs", Technical Digest International Electron Devices Meeting, p. 222, 1988.

- [44] V. Schmidt, H. Riel, S. Senz, S. Karg, W. Riess and U. Gösele, "Realization of a silicon nanowire vertical surround-gate field-effect transistor", *Small*, vol. 2, p. 85, 2006.

- [45] H. T. Ng, J. Han, T. Yamada, P. Nguyen, Y. P. Chen and M. Meyyappan, "Single crystal nanowire vertical surround-gate field-effect transistor", *Nano Lett.*, vol. 4, no. 7, p. 1247, 2004.

- [46] T. Bryllert, L. Samuelson, L. E. Jensen and L. Wernersson, "Vertical high mobility wrap-gated InAs nanowire transistor", 63rd Device Res. Conf. Dig. IEEE, p. 157, 2005

- [47] Y. Zhang, M. Sun, D. Piedra, J. Hu, Z. Liu, Y. Lin, X. Gao, K. Shepard and T. Palacios, "1200 V GaN Vertical Fin Power Field-Effect Transistors", *IEEE Int. Electron Devices Meet.*, p. 9.2.1, 2017.

# Chapter 2

# **Properties of III-Nitride semiconductors**

#### 2.1 Structural properties

III-V semiconductors are compound materials containing elements from group III (B, AI, Ga and In) and V (N, P, As, Sb) of the Periodic Table of Elements. III-Nitrides is the family of III-V materials with the group V element being nitrogen (N). They can form binary (i.e. AIN, GaN, InN), ternary (i.e.  $In_XGa_{1-X}N$ ,  $In_XAI_{1-X}N$ ,  $AI_XGa_{1-X}N$ ) and quaternary (i.e.  $In_XAI_YGa_{1-X-Y}N$ ) compounds [1–2]. III-Nitrides exhibit advantageous features for electronic and optoelectronic applications [3–5]. Their direct band gap (Eg) covers an energy range of 0.65 eV (infrared) to 6.2 eV (deep ultraviolet), which contains the whole visible spectrum (photon energy of 1.77 to 3.10 eV). The energy band gap values for AIN, GaN and InN are 6.2 eV [4], 3.4 eV [4] and 0.65 eV [6], respectively. Ternary and quaternary compounds have band gaps among the above values. For ternary III-Nitrides ( $A_XB_{1-X}N$ ) the band gap can be calculated using the following formula [2]:

$$E_g(A_x B_{1-x} N) = x \cdot E_g(AN) + (1-x) \cdot E_g(BN) - x \cdot (1-x) \cdot b$$

(2.1)

where b is the bowing coefficient, which corrects the simple linear relation involving the A and B species [7]. For Al<sub>x</sub>Ga<sub>1-x</sub>N the bowing parameter takes the value of 1.0 eV as estimated over the entire composition range [7].

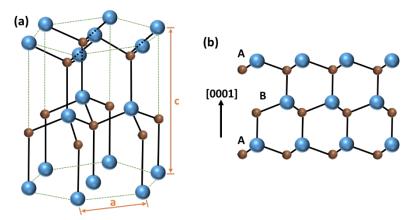

**Figure 2.1:** Schematics showing the hexagonal wurtzite crystal structure of III-Nitride semiconductors: (a) unit lattice cell, and (b) stacking sequence of (0001) monolayers.

The III-Nitride semiconductors commonly can have either a wurtzite (hexagonal) or a zincblende (cubic) crystal structure [2]. The wurtzite crystal structure is the dominant and most thermodynamically stable, whereas the zincblende structure is a metastable phase and can result from growing nitrides on cubic structures [1].

The wurtzite structure has a hexagonal unit cell and is composed of two interpenetrating hexagonal close-packed (hcp) sublattices (Fig. 2.1 (a)) of the III and N elements that are shifted the distance of an III-N bond along the [0001] axis (c-axis) [1–2]. Each group III atom is bonded to four N atoms with covalent-ionic bonds and conversely, each N atom is bonded to four group III atoms, as shown in Fig. 2.1 (a). The layer stacking along the [0001] direction follows an ABAB sequence (Fig. 2.1 (b)) of two monolayers (MLs) A and B (i.e. each ML consists of an atom layer of Ga and N for GaN). The hexagonal structure is described by two lattice constants a and c (Fig. 2.1 (a)), where a is the side length of the hexagon on the (0001) basal plane (or c-plane) and c is the height of the hexagonal prism (Fig. 2.1 (a)), and by the internal dimensionless parameter u, which is the interatomic distance in the basic unit cell [5]. In an ideal wurtzite crystal structure the two lattice constants would have a ratio c/a = 1.633 [5]. In practice, the wurtzite cell is not perfect and the c/a ratio slightly differs from the ideal case. The lattice parameters at room temperature for GaN, AlN and InN semiconductors, are listed in Table 2.1 [4].

| TABLE 2.1. The lattice parameters values of the wurtzite GaN, AlN and InN |

|---------------------------------------------------------------------------|

| semiconductors [4].                                                       |

|     | a <sub>o</sub> (Å) | $c_o$ (Å) | и     | $c_o/a_o$ |

|-----|--------------------|-----------|-------|-----------|

| GaN | 3.189              | 5.185     | 0.376 | 1.6259    |

| AlN | 3.112              | 4.982     | 0.380 | 1.6010    |

| InN | 3.540              | 5.705     | 0.377 | 1.6116    |

The lattice parameters for ternary and quaternary compounds are calculated according to the Vegard's law and in case of a ternary alloy  $(A_XB_{1-X}N)$  are given by [2]:

$$a(A_X B_{1-X} N) = x \cdot a(AN) + (1-x) \cdot a(BN)$$

(2.2)

$$c(A_X B_{1-X} N) = x \cdot c(AN) + (1-x) \cdot c(BN)$$

(2.3)

where AN and BN are the corresponding binary components and x the mole fraction.

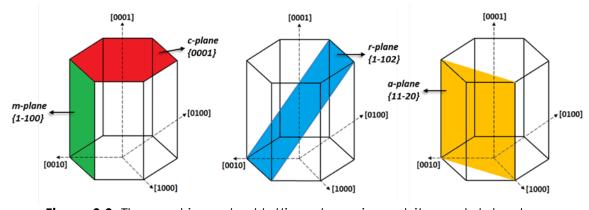

Figure 2.2: The most important lattice planes in wurtzite crystal structure.

The main planes of the wurtzite crystal structure as illustrated in Fig. 2.2, are the c-plane or basal-plane, the m-plane, the r-plane and the a-plane, which are indexed as {0001}, {1-100}, and {11-20}, respectively, according to the Miller-Bravais notation {hkil} [5].

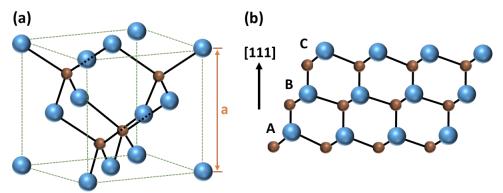

**Figure 2.3:** Schematics showing the cubic zincblende: (a) crystal structure and (b) stack sequence, of III-Nitride semiconductors.

The zincblende structure has a cubic unit cell and is composed of two interpenetrating face-centered cubic (fcc) sublattices of the III and N atoms, shifted by ¼ of the cubic cell's diagonal (Fig. 2.3(a)). Each atom is tetrahedrically coordinated with four atoms of other type, and vice versa. In zincblende structures, there is a 60° rotation along the [111] direction that causes an ABCABC sequence (Fig. 2.3(b)). Hence, the hexagonal planes along the [111] direction for the zincblende structure and along the [0001] direction for the wurtzite structure are rotated 60° with respect to each other. The cubic structure is described by a lattice parameter (a), which is the cell side length (Fig. 2.3(a)). The lattice parameters at room temperature for zincblende GaN, AlN and InN are 4.49, 4.37 and 4.98 Å, respectively [8].

#### 2.2 Polarity and polarization effects

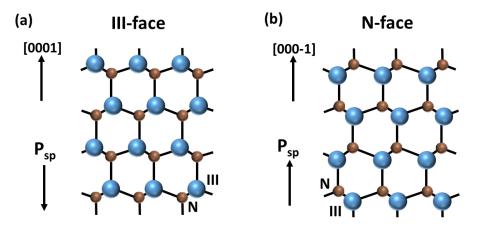

Wurtzite and zincblende crystal structures are both noncentrosymmetrical with polar axes [9]. Hence, for wurtzite Nitride structures the two opposite directions ([0001] and [000-1]) parallel to c-axis are not equivalent. This inherent property is called polarity [9]. The [0001] direction, the positive direction of c-axis, conventionally defined as the vector going from the metallic III-atom (anion) towards the N-atom (cation). The [000-1] direction is going from the N-atom towards the III-atom. The growth direction defines the polarity of a thin film with the wurtzite structure, which is Metal III-polar or III-face (Fig. 2.4(a)) and N-polar or N-face (Fig. 2.4(b)) for epitaxial growth towards the [0001] and [000-1] direction, respectively [9].

The properties of epitaxial III-Nitride semiconductor material are affected by its polarity. Reports have revealed significant differences in electrical, optical, structural and chemical properties by varying the polarity of epitaxial III-Nitride layers [10–12]. A

comparison of epitaxial grown GaN films with Ga- and N-face polarity resulted to reduced Schottky barrier [10], higher PL efficiency [11] and rougher surface morphology [11] for the N-face GaN films compared to the Ga-face ones. Moreover, an aqueous solution of Potassium Hydroxide (KOH) etches only the N-face GaN films, while the Ga-face GaN films remain unperturbed [12]. The deposition method, the substrate treatments, the nucleation conditions and layers, and the choice of substrate are critical parameters as they can vary the polarity of III-Nitride thin films and surfaces [13–16].

**Figure 2.4:** Schematics showing the (a) III-face and (b) N-face directions in the III-N wurtzite cell. The spontaneous polarization  $P_{sp}$  vector is shown for both cases.

Polarization in wurtzite III-Nitrides is an attractive inherent material property, which can impact the device operation considerably. The total polarization  $P_T$  is the sum of the intrinsic spontaneous polarization  $P_{SP}$  and the strain induced piezoelectric polarization  $P_{PZ}$  [9]:

$$P_T = P_{SP} + P_{P7}$$

(2.4)

The partially ionic nature of the III-N bonds, due to the large difference in electronegativity between the N and group-III (metal) atoms, induces positive and negative charges (dipole moments) along each III-N bond [9]. The lower crystal symmetry of the wurtzite structure compared to the zincblende one and the deviation of the c/a ratio from the ideal value, result to the existence of a spontaneous polarization  $P_{sp}$  field along the polar axis, caused by the overall uneven distribution of the dipole moments along the c-axis. This polarization exists under the absence of any external field or internal strain and its positive value direction is along the [000-1] crystal direction, as shown in Fig. 2.4.

The values of  $P_{SP}$  for relaxed GaN, AlN and InN are equal to -0.034 C/m<sup>2</sup>, -0.090 C/m<sup>2</sup> and -0.040 C/m<sup>2</sup> [17], respectively, when the positive polarization value has been defined along the [0001] direction. The  $P_{SP}$  for ternary III-Nitrides can be calculated (in C/m<sup>2</sup>) by [9]:

$$P_{A_{Y}B_{1-Y}N}^{SP} = xP_{AN}^{SP} + (1-x)P_{BN}^{SP} + bx(1-x)$$

(2.5)

where  $P_{AN}^{SP}$  and  $P_{BN}^{SP}$  are the spontaneous polarization of the binary components and b is a characteristic parameter describing the nonlinearity, with typical values of 0.021 C/m<sup>2</sup>, 0.037 C/m<sup>2</sup> and 0.070 C/m<sup>2</sup> [17] for the ternary AlGaN, InGaN and AlInN alloys, respectively.

When biaxial strain is applied to the crystal, an additional polarization is induced, the piezoelectric polarization  $P_{pz}$ , which is determined along the c-axis by [9]:

$$P_{PZ} = 2\frac{a - a_0}{a_0} \left( e_{31} - e_{33} \frac{C_{13}}{C_{33}} \right)$$

(2.6)

where  $a_0$  is the equilibrium basal-plane lattice constant, a is the actual (strained) basal-plane lattice constant,  $e_{31}$  and  $e_{33}$  are the piezoelectric coefficients, and  $C_{13}$  and  $C_{33}$  are the elastic constants. In wurtzite III-Nitrides the term  $[e_{31}$ -  $e_{33}$  ( $C_{13}$ - $C_{33}$ )] of Eq. (2.6) is negative as  $e_{31}$  takes always negative values and  $e_{33}$ ,  $C_{13}$  and  $C_{33}$  take always positive values. Hence the piezoelectric polarization  $P_{pz}$  is negative for tensile ( $a > a_0$ ) strain and positive for compressive ( $a < a_0$ ) strain in a layer.

#### 2.3 III-Nitride based heterostructures

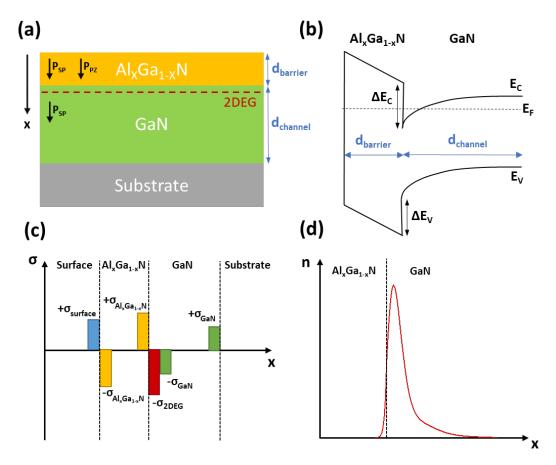

A heterostructure or heterojunction is formed when two different materials are brought in contact, practically by deposition and epitaxial growth methods. In the case of a semiconductor heterostructure/heterojunction the two semiconductor layers usually differ in energy band-gap ( $E_g$ ) and electron affinity ( $X_s$ ) [18]. The interface between these two semiconductors is called heterointerface. The deposition/growth of a semiconductor with larger bandgap (e.g.  $Al_xGa_{1-x}N$ ) on a semiconductor with lower bandgap (e.g. GaN) is the basic heterostructure for formation of a High Electron Mobility Transistor (HEMT). For n-channel HEMTs, as shown in Fig. 2.5(a), the semiconductor with the higher conduction band and the semiconductor with the lower conduction band (in an equilibrium band diagram) are called barrier and channel layer, respectively.

The band lineup at the heterointerface induces discontinuities at the conduction and valence band, the conduction band ( $\Delta E_C$ ) and valence band ( $\Delta E_V$ ) offsets, respectively [18]. Figure 2.5(b) illustrates a typical band diagram of an  $Al_xGa_{1-x}N/GaN$  based heterostructure. The conduction band ( $\Delta E_C$ ) offset and the polarization induced interface sheet charges ( $\sigma_{int}$ ) at the  $Al_xGa_{1-x}N/GaN$  heterointerface result to the formation of a two dimensional electron gas (2DEG) at an approximately triangular potential well (Fig. 2.5(b)). The origin and basic physics of this 2DEG will be discussed below.

**Figure 2.5:** (a) The layers of the heterostructure, the polarization vectors and the interfacial location of 2DEG, (b) Energy band diagram at thermal equilibrium, (c) Distribution of interfacial charges and (d) Profile of electron concentration of the polarization-induced 2DEG, in an  $Al_xGa_{1-x}N/GaN$  based structure with Ga-face polarity.

The existence of spontaneous  $P_{SP}$  and strain induced piezoelectric polarization  $P_{PZ}$  in III-Nitrides were described in Section 2.2. At the interface of two III-Nitride materials with different total polarization  $P_T$  (Eq. 2.4), a sheet of static charge ( $\sigma_{int}$ ) is formed at the interface, which is calculated in the [0001] direction by [5]:

$$\sigma_{\rm int} = P_T^{top\ layer} - P_T^{bottom\ layer}$$

(2.7)

If Eq. 2.7 takes a positive value, free electrons compensate this charge and form a 2DEG, when the band structures of these materials at the interface allows also this to happen (Fig. 2.5(b)). For an Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN heterointerface Eq. 2.7 takes the form:

$$\sigma_{\text{int}} = P_T^{Al_x Ga_{1-x}N} - P_T^{GaN} = P_{SP}^{Al_x Ga_{1-x}N} + P_{P_Z}^{Al_x Ga_{1-x}N} - P_{SP}^{GaN} - P_{PZ}^{GaN}$$

(2.8)

where Eq. 2.4 was applied for the total polarization. The  $P_{PZ}^{GaN}$  is zero since the channel layer is assumed to be strain-free. The Al<sub>x</sub>Ga<sub>1-x</sub>N is grown pseudomorphically on Ga-face polarity GaN under in-plane tensile strain [9]. This results to a piezoelectric polarization in the Al<sub>x</sub>Ga<sub>1-x</sub>N layer in addition to the spontaneous polarization, which will have the same sign and will add up (Fig. 2.5(a)). Figure 2.5(c) illustrates the charge distribution profile in an Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN based structure with Ga-face polarity.

The profile of electron concentration of polarization-induced 2DEG for pseudomorphic Ga-face  $Al_xGa_{1-x}N/GaN$  and  $Al_xIn_{1-x}N/GaN$  heterostructures is shown in Fig. 2.5(d). The sheet electron concentration ( $n_s$ ) of the 2DEG is given approximately by [17]:

$$n_{s} = \frac{\sigma_{\text{int}}}{q} - \frac{\varepsilon_{0} E_{F}}{q^{2}} \left( \frac{\varepsilon_{r,barrier}}{d_{barrier}} + \frac{\varepsilon_{r,GaN}}{d_{GaN}} \right) - \frac{\varepsilon_{0} \varepsilon_{r,barrier}}{q^{2} d_{barrier}} \left( q \Phi_{B} + \Delta - \Delta E_{C} \right)$$

(2.9)

where q is the elementary charge,  $\varepsilon_0$  is the dielectric constant of the vacuum,  $\varepsilon_{r,barrier}$  and  $\varepsilon_{r,GaN}$  are the relative dielectric constants of the constituent layers,  $E_F$  is the position of the Fermi level with respect to the GaN conduction band at the GaN-substrate interface,  $q\Phi_B$  is the Schottky barrier height of the top gate contact (or the surface potential),  $\Delta$  is the magnitude of the depth of the quantum well in the conduction band below the Fermi level,  $\Delta E_C$  is the conduction band offset and  $d_{barrier}$  and  $d_{GaN}$  are the thicknesses of the barrier and the channel layer, respectively.  $\Delta$  is calculated as a function of  $n_s$  by [17]:

$$\Delta = E_0 + \frac{\pi \hbar^2}{m_{GaN}^*} n_s$$

(2.10)

with  $E_0$  the lowest subband level of 2DEG, which is given by [17]:

$$E_0 = \left[ \frac{9\pi\hbar q^2}{8\varepsilon_0 \sqrt{8m_{GaN}^*}} \frac{n_s}{\varepsilon_{GaN}} \right]^{\frac{2}{3}}$$

(2.11)

where  $m_{Ga^{N}}^{*}$  is the electron effective mass of GaN and  $\hbar$  is the h-bar Planck's constant.

#### References

- [1] J. Pankove and T. D. Moustakas, "Gallium-Nitride (GaN) II", in "Semiconductors and Semimetals", 1st ed., vol. 53, Academic Press, 1998.

- [2] Y. Hao, J.-F. Zhang, and J.-C. Zhang, "Properties of Group III Nitride Semiconductor Materials", in "Nitride Wide Bandgap Semiconductor Material and Electronic Devices", 1st ed., CRC Press, 2016.

- [3] B. Gil, "III-Nitride Semiconductors and their Modern Devices", Oxford University Press, 2013.

- [4] O. Ambacher, "Growth and applications of group III-nitrides", J. Phys. D. Appl. Phys., vol. 31, p. 2653, 1998.

- [5] H. Morkoç, "Handbook of Nitride Semicnductors and Devices", Wiley-VCH, 2008.

- [6] J. Wu, W. Walukiewicz, W. Shan, K. M. Yu, J. W. Ager III, S. X. Li, E. E. Haller, H. Lu and W. J. Schaff, "Temperature dependence of the fundamental band gap of InN", J. Appl. Phys., vol. 94, no. 7, p. 4457, 2003.

- [7] F. Yun, M. A. Reshchikov, L. He, Th. King, H. Morkoç, S. W. Novak and L. Wei, "Energy band bowing parameter in Al<sub>x</sub>Ga<sub>1-x</sub>N alloys", *J. Appl. Phys.*, vol. 92, no. 8, p. 4837, 2002.

- [8] R. B. Araujo, J. S. De Almeida and A. F. Da Silva, "Electronic properties of III-nitride semiconductors: A first-principles investigation using the Tran-Blaha modified Becke-Johnson potential", J. Appl. Phys., vol. 114, no. 18, p. 183702, 2013.

- [9] C. Wood and D. Jena, "Polarization Effects in Semiconductors", Springer, 2008.

- [10] U. Karrer, O. Ambacher, and M. Stutzmann, "Influence of crystal polarity on the properties of Pt/GaN Schottky diodes", Appl. Phys. Lett., vol. 77, no. 13, p. 2012, 2000.

- [11] D. Huang, M. A. Reshchikov, P. Visconti, F. Yun, A. A. Baski, T. King, H. Morkoç, J. Jasinski, Z. Liliental-Weber and C. W. Litton, "Comparative study of Ga- and N-polar GaN films grown on sapphire substrates by molecular beam epitaxy", J. Vac. Sci. Technol. B Microelectron. Nanom. Struct., vol. 20, no. 6, p. 2256, 2002.

- [12] D. Li, M. Sumiya, S. Fuke, D. Yang, D. Que, Y. Suzuki and Y. Fukuda, "Selective etching of GaN polar surface in potassium hydroxide solution studied by x-ray photoelectron spectroscopy", J. Appl. Phys., vol. 90, no. 8, p. 4219, 2001.

- [13] E. S. Hellman, "The polarity of GaN: A critical review", MRS Internet J. Nitride Semicond. Res., vol. 3, no. July 1998, p. 1, 1998.

- [14] J. Jasinski, D. N. Zakharov, and L. Berkeley, "GaN grown in polar and non-polar directions", *Opto-Electronics Rev.*, vol. 12, no. 4, p. 339, 2004.

- [15] S. Mikroulis, A. Georgakilas, A. Kostopoulos, V. Cimalla, E. Dimakis, and P. Komninou, "Control of the polarity of molecular-beam-epitaxy-grown GaN thin films by the surface nitridation of Al<sub>2</sub>O<sub>3</sub> (0001) substrates", *Appl. Phys. Lett.*, vol. 80, no. 16, p.

- 2886, 2002.

- [16] A. Georgakilas, K. Aretouli, and K. Tsagkaraki, "Method for Heteroepitaxial Growth of III Metal-Face Polarity III-Nitrides on Substrates with Diamond Crystal Structure and III Nitride Semiconductors", Patent, No PCT/EP2013/058560, 2003.

- [17] O. Ambacher, J. Majewski, C. Miskys, A. Link, M. Hermann, M. Eickhoff, M. Stutzmann, F. Bernardini, V. Fiorentini, V. Tilak, B. Schaff and L. F. Eastman, "Pyroelectric properties of Al(In)GaN/GaN hetero- and quantum well structures", J. Phys. Condens. Matter, vol. 14, no. 13, p. 3399, 2002.

- [18] S. M. Sze and K. K. Ng, "Physics of Semiconductor Devices", 3rd ed. Wiley, 2006.

# Chapter 3

# Micro- and nanofabrication techniques

#### 3.1 Introduction

Microfabrication and nanofabrication refer to the design and manufacture of devices with dimensions in the range of micrometers and nanometers, respectively. These techniques are widely developed for applications in semiconductor industry into clean room environments. The fabrication of next generation GaN-based nanoscale devices requires the combination of several micro- and nanofabrication techniques in a complicated process flow [1–2].

This chapter describes the principal micro- and nanofabrication techniques used in this work, including photolithography, e-beam lithography, reactive ion etching, chemical vapor deposition, atomic layer deposition, plasma ashing, electron beam evaporation, rapid thermal annealing and wet – chemical treatment. This research infrastructure is available at the laboratory of the Microelectronics Research Group (MRG) of IESL/FORTH and Physics Department/ University of Crete, at Heraklion, Crete into a Class 1000 clean room facility of the Physics Department.

#### 3.2 Photolithography

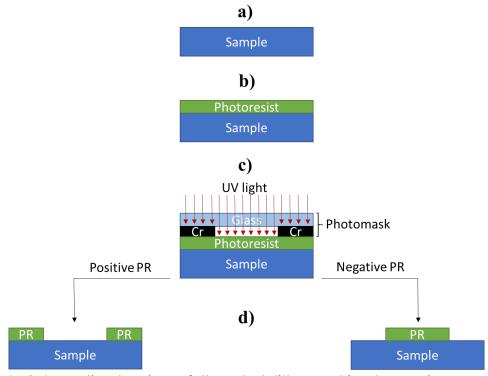

Photolithography is a microfabrication technique that is used to transfer desired patterns onto a sample/substrate and enables the fabrication of discrete semiconductor devices, as well as complex integrated circuits. It generally requires an ultraviolet (UV) light source to transfer the geometric pattern from a photomask to a light-sensitive photoresist [3].

The photolithographic process flow steps are shown schematically in Fig. 3.1. In the first step, the sample is subjected to a wet chemical treatment to clean its surface from ions, native oxides and organic contaminants (Fig. 3.1(a)). Afterwards, a light-sensitive photoresist is spun onto the sample surface and baked on a hotplate to drive off excess photoresist solvents (Fig. 3.1(b)). The spinning speed and the photoresist viscosity will determine the final thickness of the photoresist film. All these parameters (spinning speed/time, hotplate temperature/time) are critical for the photolithographical process and are provided in datasheet by the manufacturer of the photoresist [4]. Then, the photomask is aligned with the sample and the photoresist is exposed to UV light under the clear/transparent (glass) regions of the photomask, while under opaque (Cr coated) regions the sample remains unexposed (Fig. 3.1(c)). There are three different exposure techniques: contact, proximity and projection printing [5]. Figure 3.1(c) shows the contact exposure technique used in this work, in which the photoresist is brought into physical contact with the glass photomask during the exposure. In proximity technique,

a small gap is maintained between the sample and the photomask, while in projection technique there is a larger gap as an image of the pattern of the photomask is projected onto the photoresist [5]. UV exposure changes the chemical structure of the exposed photoresist layer depending on the type of photoresist: positive or negative. In positive photoresists, UV-exposed regions break down and become soluble in a subsequent development stage, while in negative photoresists exposed areas become crosslinked/polymerized and remain intact after a developing solution (Fig. 3.1(d)). Negative resists require an additional bake before the pattern's development stage [4].

**Figure 3.1:** Schematic drawing of the photolithographic steps using a positive or negative photoresist (PR).

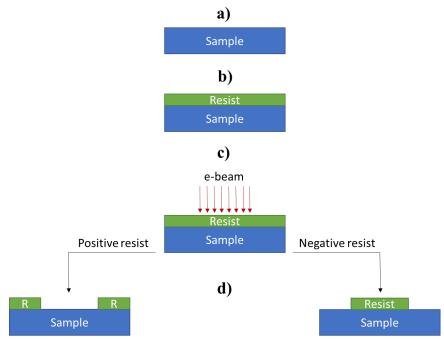

#### 3.3 Electron beam lithography

Electron beam lithography (EBL) is a powerful nanolithography technique that uses a focused electron beam (e-beam) to write patterns instead of the electromagnetic radiation used in the case of conventional photolithography technique. The EBL working principle is very similar to photolithography and is shown schematically in Fig. 3.2. In the first step, the sample is cleaned by a wet chemical treatment to remove surface ions, native oxides and organic contaminants (Fig. 3.2(a)). Afterwards, an electron beam resist is spin-coated over the surface of the sample and baked on a hotplate (Fig. 3.2(b)) to remove its solvents. Then, the highly focused e-beam is moving over the sample to write out a pattern, designed with suitable CAD tools, without the need of photomask (Fig. 3.2(c)). The e-beam changes the solubility of the resist and enables the selective removal

of either the exposed (positive resist) or non-exposed (negative resist) regions of the resist in the pattern's development stage (Fig. 3.2(d)).

**Figure 3.2:** Schematic drawing of the e-beam lithography steps using a positive or negative resist.

The main advantage of EBL over photolithography is the higher resolution because of the shorter wavelength of electrons compared to photons. As the resolution is not limited by the diffraction effect, state of the art EBL systems can achieve resolutions of few nanometers [6]. The absence of photomasks also gives flexibility to draw the desired complex patterns directly on samples by using a CAD software. Another key advantage of EBL is the ability to control energy and e-beam dose during resist exposure. However, EBL has some disadvantages that have to be mentioned. The main drawback is the poor time and cost efficiency of this technique. EBL is slower than the optical lithography and more expensive, as a complex vacuum system is included. Moreover, a limitation in resolution is caused by forward and back-scattering of the e-beam inside the resist and substrate, respectively [6–7].

#### 3.4 Reactive ion etching

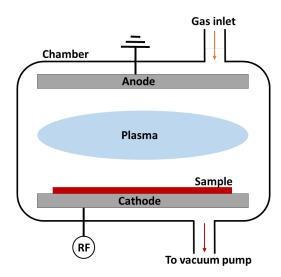

Reactive ion etching (RIE) is a plasma dry etching technology used to etch, in the presence of reactive ions, various materials (including semiconductors, dielectrics, metals, polymers and photoresists) from areas identified by a lithography process [8]. A typical parallel plate RIE system consists of two electrode plates (anode and cathode), within a cylindrical vacuum chamber (Fig. 3.3) [8]. Samples are placed on a wafer platter situated on the lower electrode (cathode) of the chamber (Fig. 3.3). Gases are initiated

through the showerhead in the top electrode (anode) and then activated by applying RF power at 13.56 MHZ to the cathode, while the anode is grounded (Fig. 3.3). The oscillating electric field ionizes the gas molecules by stripping them of electrons, creating a plasma [9]. A negative DC bias is induced at the sample substrate by the free electrons, which accelerates the plasma ions towards the sample surface. The ions strike the sample surface vertically, where they react to form volatile species that are removed by the vacuum system and thus enable the etching mechanism.

Figure 3.3: Schematic diagram of a reactive ion etching (RIE) plasma system.

#### 3.5 Chemical vapor deposition

Chemical vapor deposition (CVD) is a process used to produce a wide range of solid thin-films (dielectrics, metals) and nowadays is commonly used to synthesize high-quality 2-D materials [10–11]. The main idea of this procedure involves the reaction or decomposition of vapor phase volatile precursors over a heated substrate, placed in a reaction chamber. Gas flow through the reaction chamber removes volatile by-products that are frequently produced [10–11].

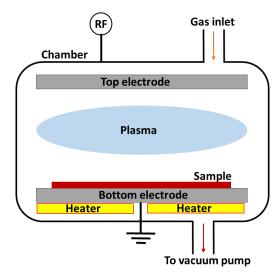

There are several types of CVD technologies, including plasma enhanced chemical vapor deposition (PECVD), low pressure chemical vapor deposition (LPCVD), metal organic chemical vapor deposition (MOCVD) and atmospheric pressure chemical vapor deposition (APCVD), differing generally in the means by which chemical reactions are initiated. The PECVD method, which has been used in this work, utilizes plasma to provide the required energy in order the chemical reactions to take place on the substrate's surface. This has the advantage of lower deposition temperatures, critical in many applications to avoid device damage. Deposition is achieved by introducing the reactant gases into the process chamber [10–11] through the showerhead of a top electrode (Fig. 3.4). An RF potential is applied to the top electrode to generate the plasma, while the bottom parallel electrode is grounded (Fig. 3.4). The capacitive

coupling between the electrodes excites the reactant gases into a plasma, which induces chemical reactions and results in the reaction product being deposited on the substrate. The substrate, which is placed on the grounded electrode, is typically heated to 250 – 350 °C, depending on the specific film requirements.

**Figure 3.4:** Schematic diagram of a plasma enhanced chemical vapor deposition (PECVD) system.

#### 3.6 Atomic layer deposition

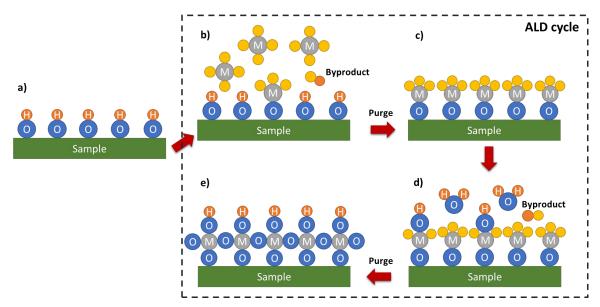

Atomic layer deposition (ALD) is an advanced surface-controlled CVD technique [12], based on the sequential use of a gas phase chemical process that allows the precisely controlled (atomic layer by atomic layer) deposition of thin films (e.g. high k dielectrics). The majority of ALD processes use two chemicals called precursors. The surface of the sample is exposed alternatively to each one of these precursors and through the repeated exposure and formation of atomic layers, the desired thin film thickness is deposited [12].

Figure 3.5 shows the schematic of the sequential, self-limiting surface reactions during ALD process for a metal-oxide deposition. The surface of the sample has to be hydroxyl (-OH) group terminated (Fig. 3.5(a)) in order to serve as the initial nucleation site for reaction with ALD precursors. Then the sequential ALD process is started by introducing to the reactor a pulse of a metal containing volatile precursor (Fig. 3.5(b)), which reacts with active sites on the sample surface in a self-limiting way. A purge step with a carrier gas (typically  $N_2$  or Ar) removes excess precursor and reaction products (byproducts) forming the first ALD layer (Fig. 3.5(c)). Afterwards, a pulse of an oxygen containing volatile precursor (typically  $H_2O$ ) is introduced (Fig. 3.5(d)), which reacts with the first chemisorbed precursor, again in a self-limiting way. A second purge step with the carrier gas removes excess precursor and byproducts forming the second ALD layer, with the surface prepared (-OH terminated) to react with another pulse of the first precursor (Fig.

3.5(e)). By carrying out a certain number of ALD cycles, the targeted film thickness can be obtained.

Figure 3.5: Schematic illustration of a typical ALD process cycle.

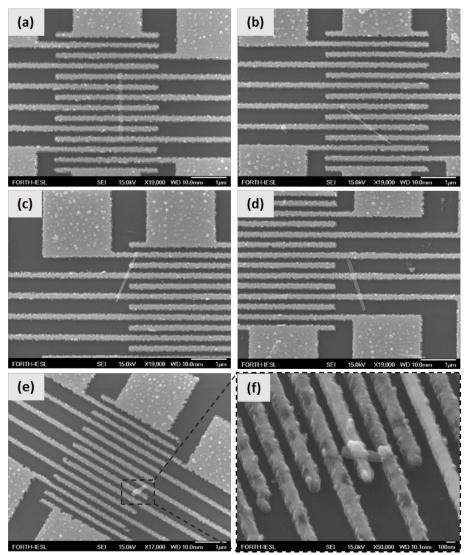

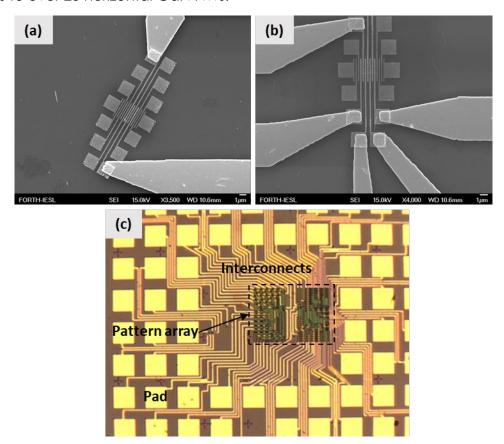

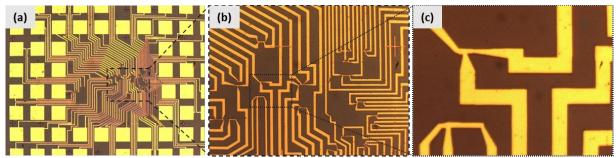

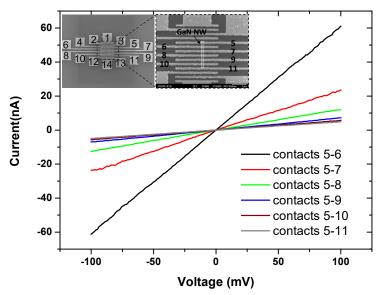

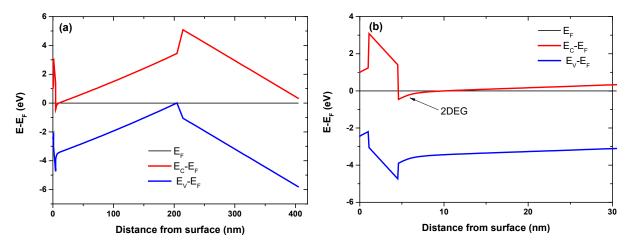

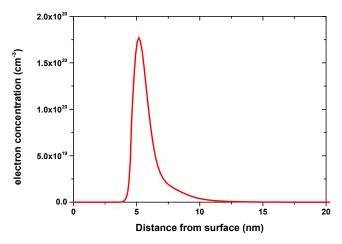

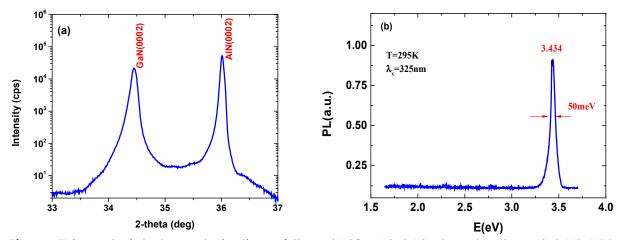

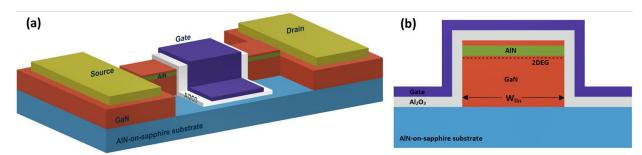

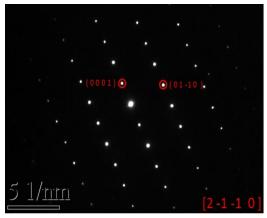

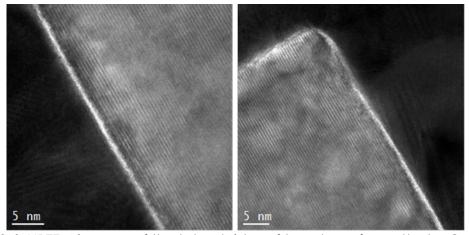

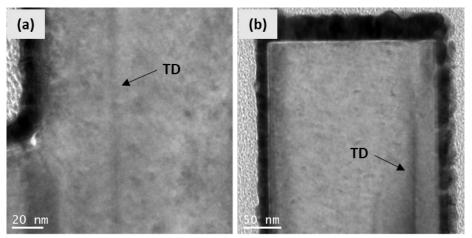

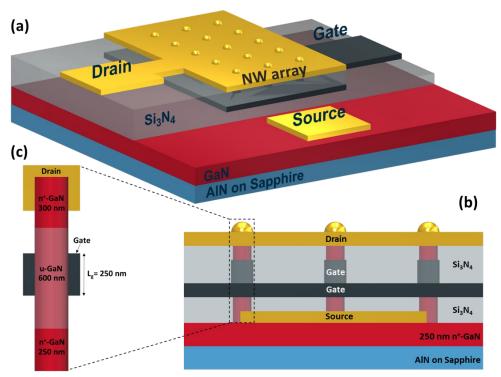

#### 3.7 Plasma ashing