University of Crete

Department of Physics, Greece

# EXPERIMENTAL AND THEORETICAL STUDY OF 3C-SILICON CARBIDE NANOWIRE FIELD EFFECT TRANSISTORS

## Konstantinos I. ROGDAKIS

Thesis presented for the Ph.D. degree with co-supervision

**Directors of thesis:** Edwige BANO for Grenoble INP and Panagiotis TZANETAKIS for Universite of Crete **Co-supervisor:** Konstantinos ZEKENTES

## **JURY**

| M.  | Thierry OUISSE          | President                               |

|-----|-------------------------|-----------------------------------------|

| M   | Charalambos DIMITRIADIS | External Examiner,                      |

| M.  | Hariton POLATOGLOU      | External Examiner,                      |

| Mme | Edwige BANO             | ,Director of thesis Grenoble INP        |

| M.  | Konstantinos ZEKENTES   | ,Co-supervisor University of Crete      |

| M.  | Panagiotis TZANETAKIS   | ,Director of thesis Universite of Crète |

| M.  | Nikolaos FLYTZANIS      | ,Examiner                               |

| M.  | Marco PALA              | ,Examiner                               |

## Experimental and theoretical study of 3C-Silicon Carbide nanowire field effect transistors

Copyright 2010

by

Konstantinos I. Rogdakis

## **Table of contents**

|    | List of abbrev | viations                                                     | p. 6  |

|----|----------------|--------------------------------------------------------------|-------|

|    | Abstract in Fi | rench                                                        | p. 8  |

|    | Abstract in E  | nglish                                                       | p. 9  |

|    | Abstract in G  | ireek                                                        | p. 10 |

|    | Summary        |                                                              | p. 11 |

|    | Acknowledge    | ements                                                       | p. 15 |

|    | Citations to p | published work                                               | p. 17 |

|    |                |                                                              |       |

| 1. | Chapter one    | : Bibliography review on nanowire growth and related devices |       |

|    | 1.1 Introducti | ion                                                          | p. 20 |

|    | 1.2 One-dime   | ensional material growth and basic properties                | p. 23 |

|    | 1.2.1          | Vapor phase synthesis                                        | p. 24 |

|    | 1.2.2          | Thermal evaporation                                          | p. 27 |

|    | 1.2.3          | Template-assisted Synthesis and alignment                    | p. 29 |

|    | 1.2.4          | Alternative nanowire fabrication techniques                  | p. 30 |

|    | 1.2.5          | Heterostructures of nanowires                                | p. 34 |

|    | 1.2.6          | Properties of semiconductor nanowires                        | p. 35 |

|    | 1.3 Nanowire   | e-based transistors                                          | p. 37 |

|    | 1.3.1          | General characteristics                                      | p. 37 |

|    | 1.3.2          | Device operation mode                                        | p. 44 |

|    | 1.4 3C-SiC na  | anowires: Growth, properties and applications                | p. 47 |

|    | 1.4.1          | Introduction                                                 | p. 47 |

|    | 1.4.2          | Growth of 3C-SiC nanowires                                   | p. 47 |

|    | 1.4.3          | 3C-SiC nanowire FETs                                         | p. 52 |

|    | 1.4.4          | Other application of 3C-SiC nanowires                        | p. 53 |

|    | 1.5 Reference  |                                                              | n 55  |

| 2. | Chapter two           | : Modeling of electrical transport in 3C-SiC and Si nanow                  | ire FETs |

|----|-----------------------|----------------------------------------------------------------------------|----------|

|    | 2.1 Introducti        | on                                                                         | p. 58    |

|    | 2.2 Presentati        | on of the simulation scheme                                                | p. 59    |

|    | 2.2.1                 | Self-consistent solution                                                   | p. 59    |

|    | 2.2.2                 | Non equilibrium Green's Function formalism: Ballistic and transport regime | •        |

|    | 2.2.3                 | Mode space approach                                                        | p. 66    |

|    | 2.2.4                 | Scattering processes                                                       | p. 70    |

|    | 2.2.5                 | Drift diffusion model: Diffusive transport regime                          | p. 74    |

|    | 2.2.6                 | Device geometry and parameters                                             | p. 75    |

|    | 2.3 Simulation        | n results- Ballistic transport                                             | p. 77    |

|    | 2.3.1                 | Introduction                                                               | p. 77    |

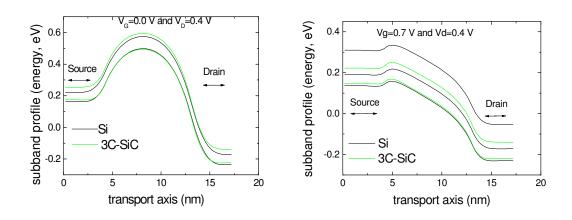

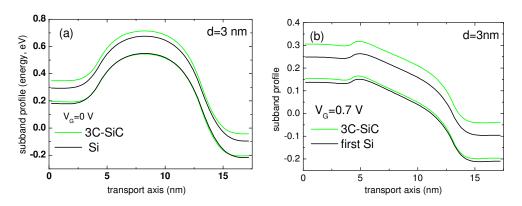

|    | 2.3.2                 | Subbands profile                                                           | p. 78    |

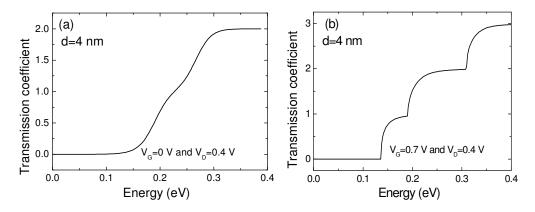

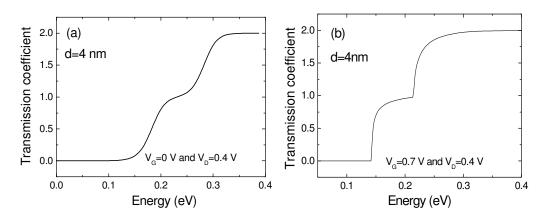

|    | 2.3.3                 | Transmission coefficient                                                   | p. 80    |

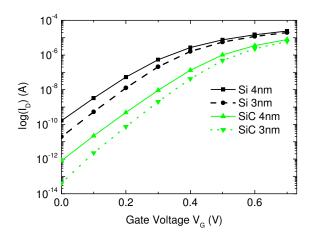

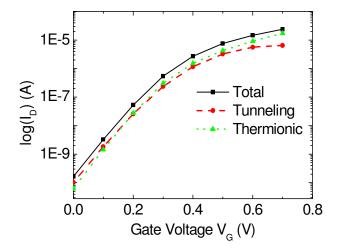

|    | 2.3.4                 | Transfer characteristics                                                   | p. 81    |

|    | 2.4 Simulation        | n results- Dissipative transport                                           | p. 85    |

|    | 2.4.1                 | Introduction                                                               | p. 85    |

|    | 2.4.2                 | Drift-diffusion results                                                    | p. 85    |

|    | 2.4.3                 | Quasi-ballistic transport results                                          | p. 87    |

|    | 2.5 Conclusio         | ons                                                                        | p. 93    |

|    | 2.6 Reference         | es                                                                         | p. 94    |

| 3. | Chapter thre          | ee: 3C-SiC nanowire growth                                                 |          |

|    | 3.1 Introductionp. 98 |                                                                            |          |

|    | 3.2 Growth of         | f 3C-SiC nanowires                                                         | p. 98    |

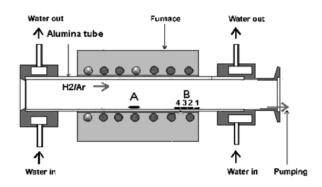

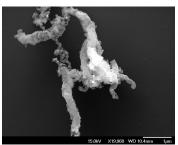

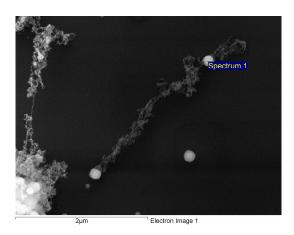

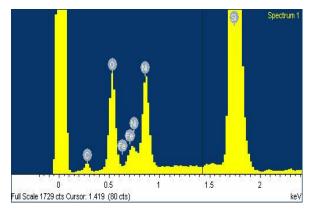

|    | 3.2.1                 | CNT and Si nanowire conversion to 3C-SiC nanowire                          | p. 98    |

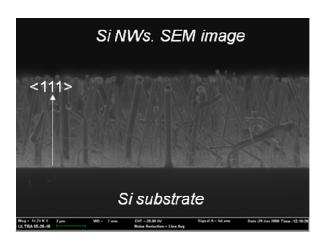

|    | 3.2.2                 | Si NW conversion to 3C-SiC nanowire                                        | p. 102   |

| 4. | Chapter four: Experimental 3C-SiC and Si nanowire FETs          |                                                               |  |

|----|-----------------------------------------------------------------|---------------------------------------------------------------|--|

|    | 4.1 Introductionp. 106                                          |                                                               |  |

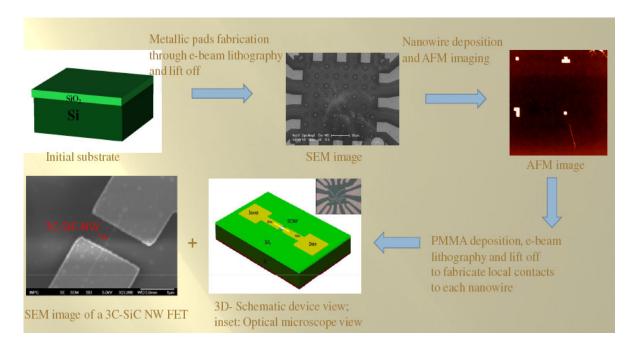

|    | 4.2 Nanowire transistor fabricationp. 107                       |                                                               |  |

|    | 4.2.1                                                           | Nanowire solution preparationp. 107                           |  |

|    | 4.2.2                                                           | Substrate preparationp. 108                                   |  |

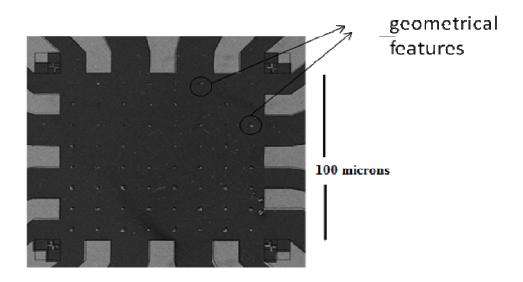

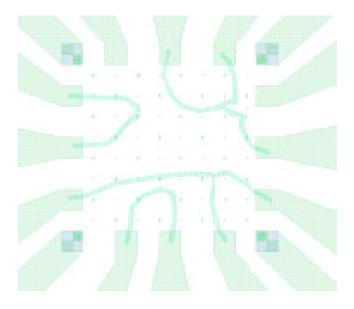

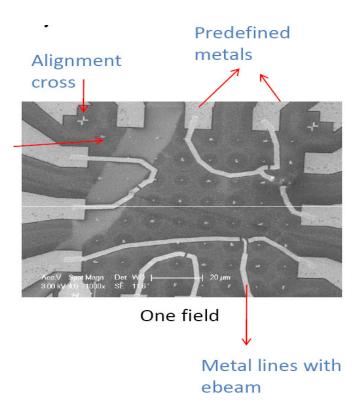

|    | 4.2.3                                                           | Metallic contacts fabrication; e-beam lithographyp. 109       |  |

|    | 4.2.4                                                           | Device annealing and nanowire surface cleaningp. 112          |  |

|    | 4.3 Electrical                                                  | characterizationp. 113                                        |  |

|    | 4.3.1                                                           | 3C-SiC NWFET with ohmic contactsp. 113                        |  |

|    | 4.3.2                                                           | 3C-SiC NWFET with rectifying behaviour contactsp. 115         |  |

|    | 4.3.3                                                           | Self heating annealing effectp. 118                           |  |

|    | 4.3.4                                                           | Conclusionsp. 119                                             |  |

|    | 4.4 Simulatio                                                   | n of device fabrication process and electrical behaviorp. 120 |  |

|    | 4.4.1                                                           | 3C-SiC nanowire FETsp. 120                                    |  |

|    | 4.4.2                                                           | Ion implanted Si nanowire p-FETsp. 128                        |  |

|    | 4.5 Reference                                                   | p. 139                                                        |  |

|    |                                                                 |                                                               |  |

| 5. | Chapter four: Conclusions and prospective for future workp. 141 |                                                               |  |

#### List of abbreviations

3C-SiC 3 Cubic Silicon Carbide

CMOS Complementary Metal-Oxide- Semiconductor

MOSFET Metal-Oxide- Semiconductor Field-Effect Transistor

CNTs Carbon Nanotubes

NWs Nanowires

GAA Gate-All Around

VLS Vapor-Liquid-Solid

CVD Chemical Vapor Deposition

MBE Molecular Beam Epitaxy

CBE Chemical Beam Epitaxy

FEOL front-end-of-line

BEOL back-end-of-line

FEDs Field Emission Displays

SNAP Superlattice NAnowire Pattern

TEM Transmission Electron Microscopy

UHV Ultra High Vacuum

OAG Oxide-Assisted Growth

NWL Nanowire Lithography

SOI Silicon on Insulator

NIL NanoImprint Lithography

UV Ultra-Violet

HEMTs High Electron Mobility Transistors

MOCVD Metal Organic Chemical Vapor Deposition

SB Schotkky Barrier

FE Field Emission

SEM Scanning Electron Microscopy

AFM Atomic Force Microscopy

NEGF Non Equilibrium Green's Function

UMS Uncoupled Mode Space

CMS Coupled Mode Space

BTE Boltzmann Transport Equation

SR Surface roughness

rms root mean square

SS Subthreshold Slope

DOS Density of States

PH Phonon

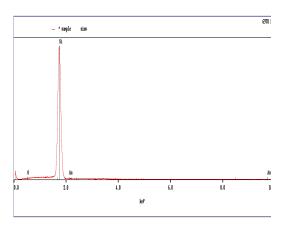

XRD X-ray Diffraction

PL Photoluminescence

EELS Electron Energy Loss Spectroscopy

EDS Electron Diffraction Spectrum

RTA Rapid Thermal Annealing

EBL Electron-Beam Lithography

SAED Selective Area Electron Diffraction

#### **Abstract in French**

Récemment, la croissance et la caractérisation de nanostructures à une dimension (nanofils, nanotiges, nanotubes) de semiconducteurs à large bande interdite sont largement étudiées à cause de leurs applications potentielles en nanoélectronique, capteurs, batteries et cathodes à émission de champ. L'approche nanofil autorise une géométrie coaxiale de canal / diélectrique de grille, ce qui est idéal pour la réduction des dimensions et le contrôle électrostatique. Parmi les matériaux à large bande interdite, le SiC-3C présente de fortes valeurs de conductivité thermique, champ de claquage, vitesse de dérive des électrons, module de Young et dureté mais également une excellente stabilité chimique et physique. Par conséquent, on s'attend à ce que les nanofils à une dimension en SiC-3C, réalisés par la technique "top-down" ou "bottom-up", génèrent une nouvelle famille de dispositifs haute performance offrant des avantages supplémentaires par rapport à la technologie « classique » Si.

Ce manuscrit est divisé en 3 parties principales. Le premier chapitre donne une vision générale de la croissance des nanofils, de leurs propriétés et des dispositifs associés. L'étude théorique est présentée dans le deuxième chapitre, dans lequel est détaillé le fonctionnement des transistors à effet de champ à base de nanofil SiC-3C ou nanoFET (Field Effect Transistors, FETs) en régime de transport balistique ou en régime de diffusion. Plus précisément, des simulations numériques de nanoFETs à géométrie «gate-all-around » (GAA) à base de nanofils SiC-3C et Si sont présentées. Une description entièrement quantique du transport est adoptée pour les très courtes dimensions. Une résolution self-consistante des équations de Poisson et Schrödinger dans le formalisme des fonctions de Green hors équilibres (non equilibrium Green's functions, NEGF) a été utilisée. Une comparaison directe entre les performances des dispositifs Si et SiC-3C donne quelques éclaircissements sur les différentes propriétés de transport des deux matériaux. Dans le troisième chapitre, la réalisation et la caractérisation électrique des nanoFETs SiC-3C sont présentées. La dernière partie de ce manuscrit est dédiée à la simulation des caractéristiques électriques des nanoFETs élaborés (SiC-3C et Si) en utilisant le logiciel Silvaco. Un ajustement précis des données expérimentales permet d'obtenir la densité de porteurs dans le canal et leur mobilité, d'estimer la qualité de l'interface nanofil/diélectrique, et d'étudier l'effet de la diminution de la concentration de porteurs, de la hauteur de barrière Schottky au niveau des contacts et de la qualité de l'interface sur les performances des dispositifs.

#### **Abstract in English**

Recently, the growth and characterization of one-dimensional (1D) nanostructures (nanowires, nanorods, nanotubes) of wide-band-gap semiconductors have been extensively studied due to their potential for applications in nanoelectronics, sensors, batteries, and field emission displays (FEDs). The nanowire (NW) approach allows for a coaxial gate-dielectric channel geometry that is ideal for further downscaling and electrostatic control. Among the wide band-gap materials, 3C-SiC exhibits high values of thermal conductivity, breakdown electric field, electron drift velocity, Young's modulus and hardness as well as excellent chemical and physical stability. Therefore, 3C-SiC semiconductor nanowires, grown either with top-down or bottom-up techniques, are expected to generate a new family of high-performance nanowire devices as an add-on to mainstream Si technology.

This thesis is divided into three main parts. In the first chapter, an introduction to nanowire growth, properties and devices is presented. Our theoretical work follows in chapter two, where a study of 3C-SiC nanowire-based FETs (NWFETs) operating either in ballistic or in dissipative transport regime is indicated. More precisely, we introduce numerical simulations of gate-all-around (GAA) 3C-SiC and Si NWFETs using a full quantum self-consistent Poisson-Schrödinger algorithm within the non-equilibrium Green's functions (NEGF) formalism. A direct comparison between Si and 3C-SiC device performances sheds some light on the different transport properties of the two materials. In the third and forth chapter, the nanowire growth, the fabrication and the electrical characterization of 3C-SiC NWFETs is presented. The last part of the thesis is devoted to the simulation of the electrical behaviour of the experimental NWFETs (both 3C-SiC and Si NWFETs) by using the Silvaco simulation tool. The accurate fitting of the experimental data, allows us to calculate the nanowire carrier concentration and mobility, and estimate the nanowire/dielectric interface quality as well as to study the effect of carrier concentration lowering, Schottky barriers height at contacts and the interface quality on the device's performance.

## Περίληψη

Η ανάπτυξη και ο χαρακτηρισμός νανοδομών μιας διάστασης (1-Δ) όπως νανονήματα, νανοκολόνες ή νανοσωλήνες ημιαγωγών υψηλού χάσματος έχουν πρόσφατα εκτενώς μελετηθεί εξαιτίας των πιθανών εφαρμογών τους στη νανοηλεκτρονική, σε αισθητήρες, μπαταρίες και οθόνες εκπομπής πεδίου. Η χρήση νανονημάτων επιτρέπει ομοκεντρική γεωμετρία διηλεκτρικού πύλης και καναλιού του τρανζίστορ η οποία είναι ιδανική για την περαιτέρω σμίκρυνση των διαστάσεων της διάταξης και καλύτερο ηλεκτροστατικό έλεγχο των φορέων. Ανάμεσα στους ημιαγωγούς υψηλού χάσματος, το καρβίδιο του πυριτίου (3C-SiC) έχει μεγάλο συντελεστή θερμικής αγωγιμότητας, μεγάλη τιμή ηλεκτρικού πεδίου κατάρρευσης και μέτρου ελαστικότητας, μεγάλη ταχύτητα ολίσθησης ηλεκτρονίων καθώς και εξαιρετική χημική και φυσική σταθερότητα. Επομένως, νανονήματα 3C-SiC, κατασκευασμένα ακολουθώντας τεχνικές είτε από «πάνω προς τα κάτω» ή από «κάτω προς τα πάνω», αναμένεται να δημιουργήσουν μια νέα οικογένεια ηλεκτρικών διατάξεων οι οποίες θα χρησιμοποιηθούν ως πρόσθετες/επέκταση στην υπάρχουσα τεχνολογία πυριτίου.

Η παρούσα διδακτορική διατριβή χωρίζεται σε τρία κύρια μέρη. Στο πρώτο κεφάλαιο παρουσιάζεται μια εισαγωγή στην κατασκευή γενικά νανονημάτων και στις βασικές ιδιότητές τους καθώς και σε διατάξεις βασισμένες σε αυτά. Η θεωρητική μας μελέτη εν συνεχεία ακολουθεί στο δεύτερο κεφάλαιο, όπου τρανζίστορ βασισμένα σε νανονήματα 3C-SiC λειτουργούν είτε στην βαλλιστική περιοχή ή στην περιοχή όπου υπάρχει σκέδαση φορέων. Πιο συγκεκριμένα, παρουσιάζουμε αριθμητικές προσομοιώσεις τρανζίστορ περιμετρικής πύλης βασισμένα σε νανονήματα 3C-SiC και πυριτίου (Si) χρησιμοποιώντας έναν κβαντικό αλγόριθμο βασιζόμενο σε αυτό-συνεπή λύση των εξισώσεων Poisson και Schrödinger υπό τον φορμαλισμό εξισώσεων Green εκτός ισορροπίας (NEGF). Μια άμεση σύγκριση ανάμεσα σε διατάξεις 3C-SiC και πυριτίου επισημαίνει τις βασικές διαφορές των δύο ημιαγωγών όσον αφορά στην ηλεκτρική τους συμπεριφορά. Το τρίτο και τέταρτο κεφάλαιο αναφέρονται στην ανάπτυξη των νανονημάτων, στην κατασκευή των τρανζίστορ και στον ηλεκτρικό χαρακτηρισμό τους. Στο τελευταίο μέρος της διδακτορικής διατριβής παρουσιάζουμε την προσομοίωση των πειραματικών μας αποτελεσμάτων χρησιμοποιώντας το λογισμικό προσομοίωσης Silvaco. Η ακριβής προσομοίωση μας επιτρέπει να υπολογίσουμε τη συγκέντρωση και την ευκινησία των φορέων στα νανονήματα, και επίσης να εκτιμήσουμε την ποιότητα της διεπιφάνειας ανάμεσα στα νανονήματα και το διηλεκτρικό υλικό, καθώς και να εντοπίσουμε την επίδραση της μείωσης της συγκέντρωσης των φορέων, του ύψους φραγμού στις επαφές πηγής και απαγωγού καθώς και της ποιότητας της διεπιφάνειας στην απόδοση του τρανζίστορ.

## Summary

Low-dimensionality materials and especially one-dimensional (1D) have stimulated great interest due to their importance in basic scientific research and potential technological applications. Their low dimensionality -associated with new quantum size effects- has provided new ways to develop nanoscale electronics, optoelectronics and in general nanostructures. On the other hand, Silicon Carbide (SiC) is widely investigated due to its physical properties like the wide band-gap, the high breakdown field strength, the high value of thermal conductivity, the high saturation carrier drift velocity and the stability in high temperature as well as in corrosive environments. The combination of these properties with the advantages of nanowires can result in devices operating at high temperature (and/or high operating voltage) with unique performance.

Before the realization of the present thesis, only one experimental study on SiC NW FETs had been reported presenting a poor device performance. Moreover, none theoretical study concerning the electrical transport properties of 3C-SiC nanowires had been performed. Therefore, the main aim of the present thesis was to perform a complete experimental and theoretical study of SiC NWFETs.

The first thesis chapter is a bibliography review and it is divided into three main parts (section 1.2, 1.3 and 1.4). After a brief introduction (section 1.1), the next two parts (section 1.2 and 1.3) are addressing important steps toward the implementation of semiconductor nanowire devices. The first of these parts (section 1.2) describes various aspects of nanowire growth and of the control of their properties. This is followed by the second part (section 1.3) discussing the development and optimization of new, nanowire-based devices mainly focusing on field effect transistors. We briefly cover the importance of characterizing and extracting important physical properties in order to evaluate and optimize nanowire growth and processing of devices based on them. Potential devices based on nanowires then need to be appropriately characterized, which is briefly described. In part three (section 1.4), we focus on 3C-SiC nanowires growth, properties and their applications. Again, the main device application is a nanowire-based transistor, which is the central subject of focus of this thesis. In section 1.4, we summarize the various published results from other research groups as an introduction to our theoretical and experimental work, which will be presented in chapter 2, 3 and 4.

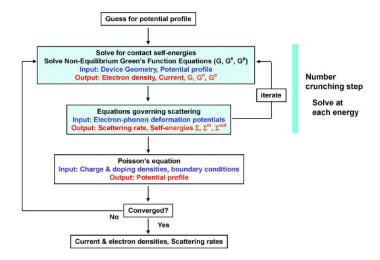

Our theoretical work described in chapter two was started by investigating on a theoretical level the advantages of SiC-based NWFETs. Our SiC calculations are based on an initial code dedicated to Si NWFETs. This code was appropriately modified in order to describe the

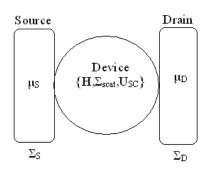

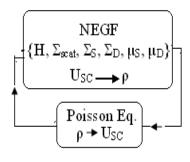

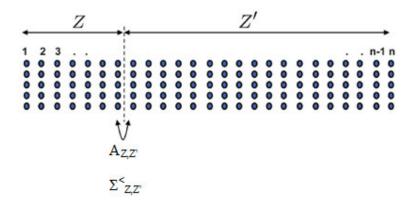

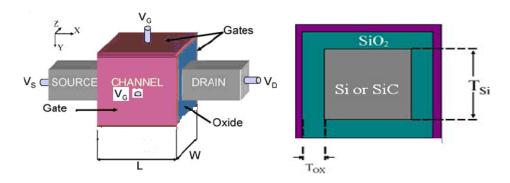

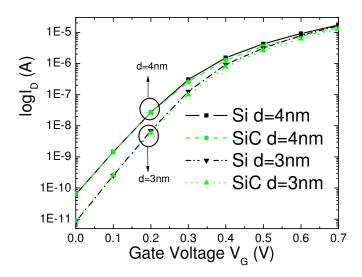

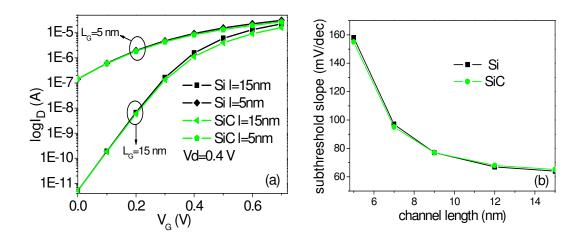

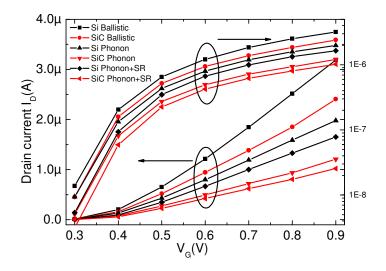

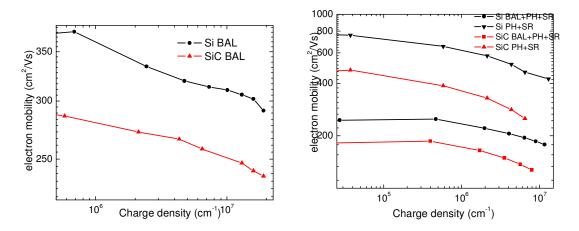

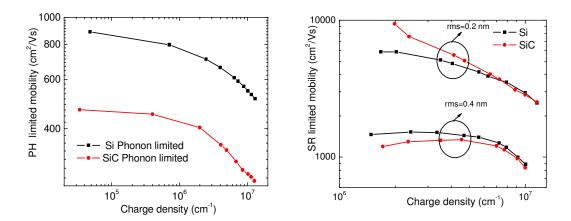

behavior of SiC. This study had as target to reveal which would be the ultimate performance of SiCbased NWFETs once the technology-related issues would be resolved. As the dimensions are scaled down, the increasing importance of physical phenomena like quantum tunneling, reflections through metallic/semiconducting barriers and through channel potential barriers and strong quantum confinement have drawn the interest of a full quantum description of carrier transport. Hence, device numerical simulations based on the self-consistent solution of the Schrödinger and Poisson equations are envisaged in order to correctly model these physical effects and give a valuable analysis and prediction of the device performance (section 2.2). We use three different simulation techniques in order to describe the electrical transport properties of 3C-SiC and Si NWFETs operating at distinct electrical transport regimes. Depending on the channel length  $(L_G)$  a transistor operates in ballistic, quasi-ballistic and diffusive electrical transport regime. When  $L_G < \ell$ , where  $\ell$  is the mean free path in the semiconductor (the distance between two collisions-scattering events), then we do not expect any scattering along the channel (only scattering at the source/channel and drain/channel interfaces), in other words we have ballistic conduction. In this regime, by excluding the effect of scattering, we expect to observe the upper limit of device performance. Mobility theory estimates a mean free path value for Si and 3C-SiC around 10 nm. The experiments predict even shorter lengths, around 2-3 nm due to the presence of acoustic phonon scattering. In ballistic transport regime, we use a Poisson/Schrödinger self consistent solution within the NEGF formalism (section 2.3). Our NWFETs are Triple-gated and have channel length varying from 5 to 15 nm and a cross section side 3 and 4 nanometers.

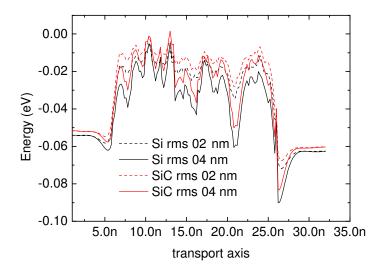

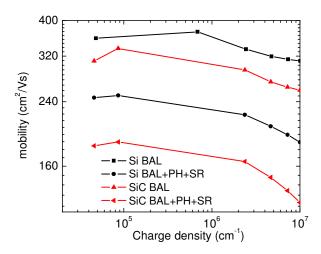

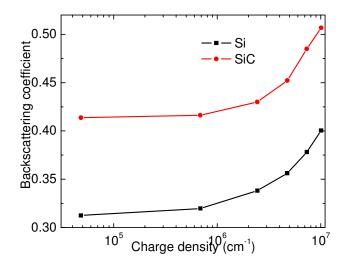

On the other hand, ultimately scaled experimental NWFETs, mainly based on Si nanowires, operate in quasi ballistic regime. When the channel length is comparable with the mean free path, the transport is not pure ballistic. Due to the increased effect of both surface roughness and phonon scattering, we have a deviation from the ideal transport conditions of ballistic carriers. For this dissipative transport regime, we used a similar simulation scheme as for the case of ballistic transport, and moreover we included a quantum treatment of scattering effects (both surface roughness and phonon scattering) (section 2.4.2). For this kind of simulations, we implemented a Gate All Around (GAA) device geometry and we chose the length of the nanowire to be equal to 20 nm and the cross section side at 5 nm.

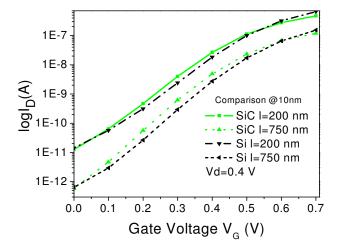

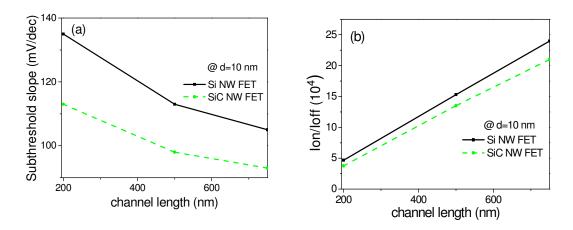

Our experimental 3C-SiC NWs (as they will be presented in chapter three) have length of few micrometers and diameter from 40 to 90 nm. These dimensions are far away from the ballistic transport regime conditions ( $L_G>\ell$ ) allowing us to use a drift-diffusion model to describe this diffusive transport regime. To address this large dimension issue, we solve the continuity equation

self-consistently with the Poisson equation and we calculate the current through the drift diffusion model (which is an approximation of Boltzmann transport equation) (section 2.4.1). The simulated devices have a length from 200-750 nm and cross section side of 10 nm. Again this calculation shows the ultimate performance for the large dimension SiC-based NWFETs. As a general conclusion of our theoretical work, we could say that SiC based devices are quite competitive to Si ones. Despite the slightly worst electrical performance of SiC NW devices, SiC NW could be used to targeted applications such as high temperature or high operating voltages devices.

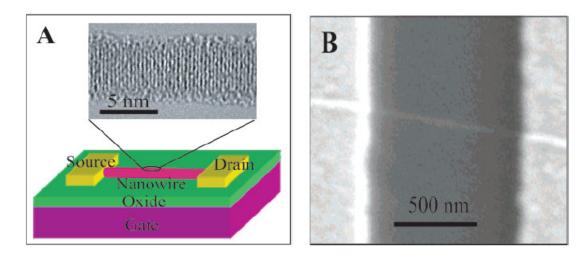

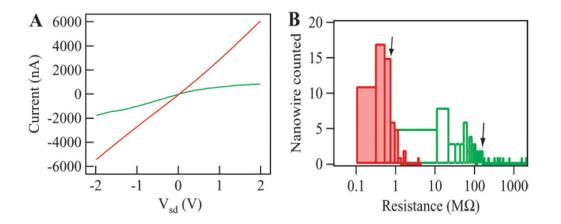

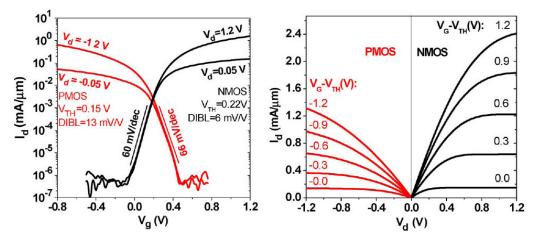

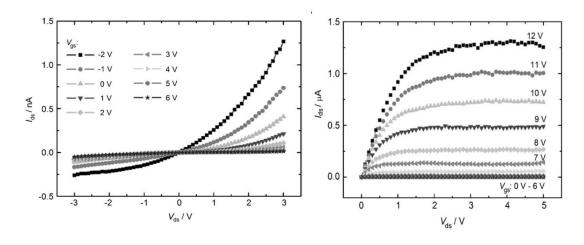

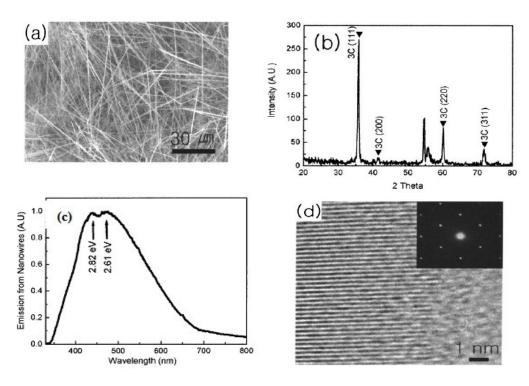

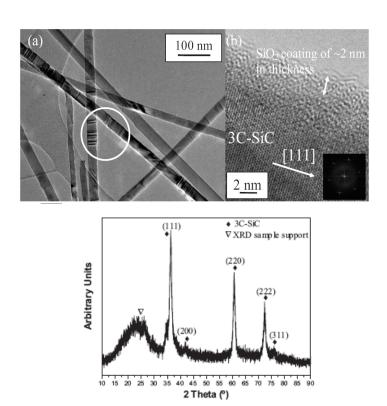

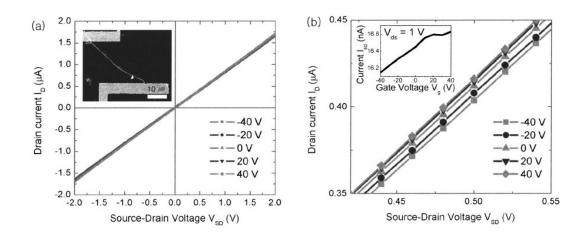

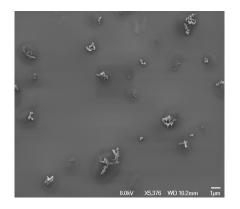

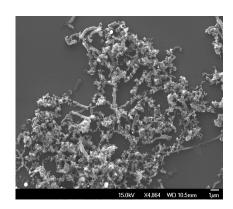

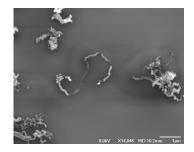

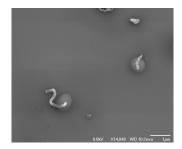

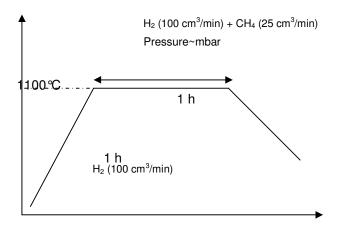

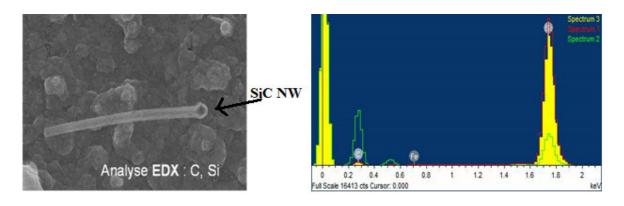

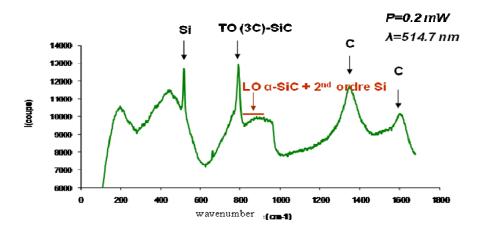

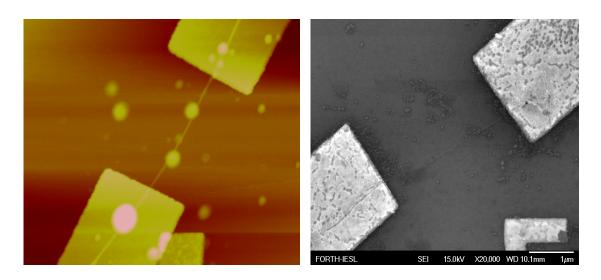

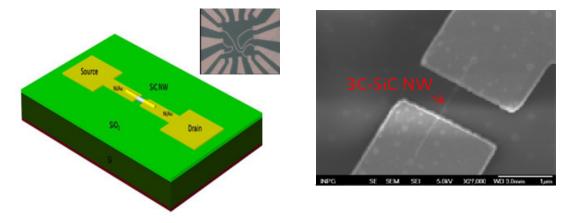

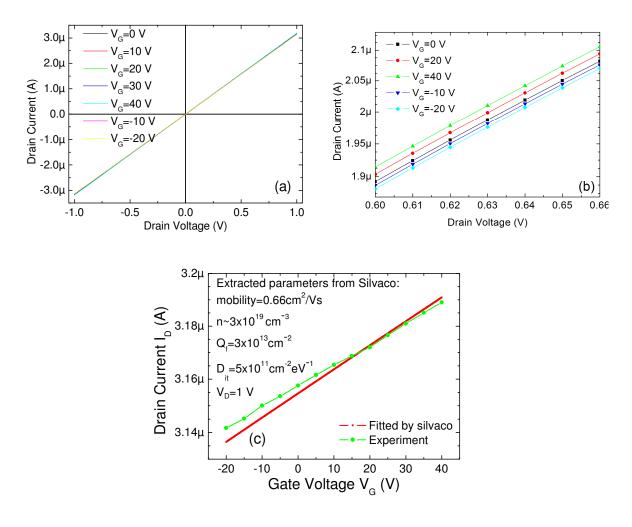

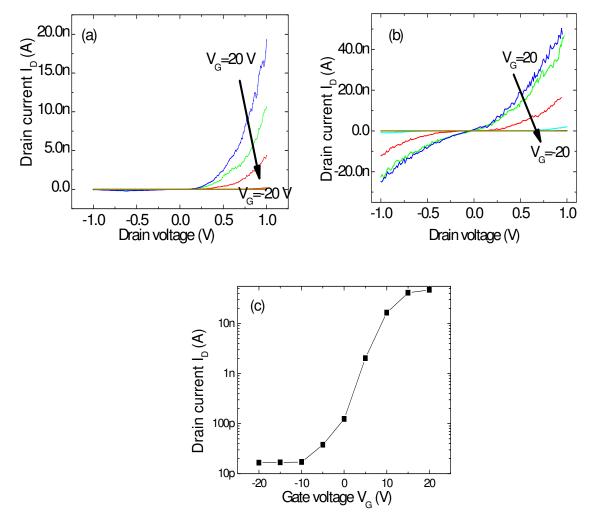

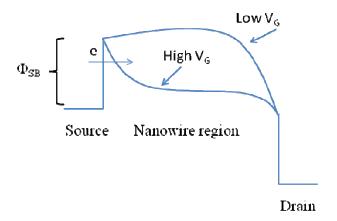

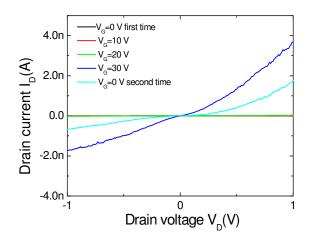

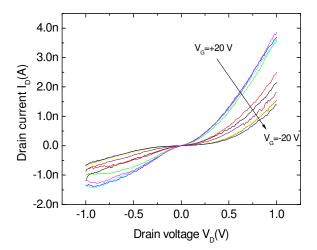

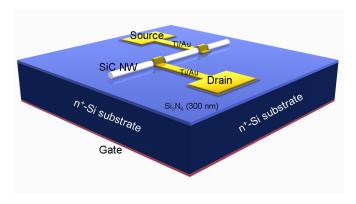

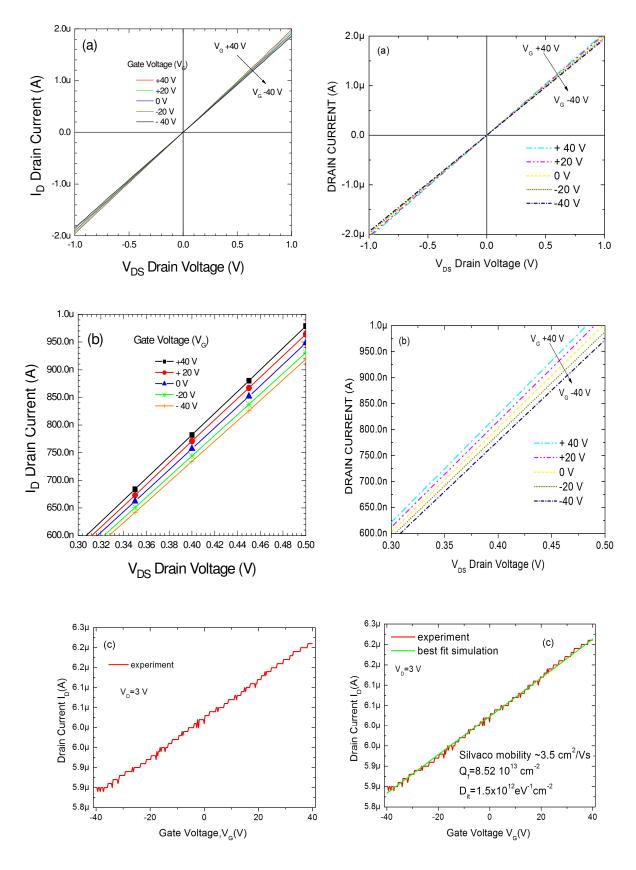

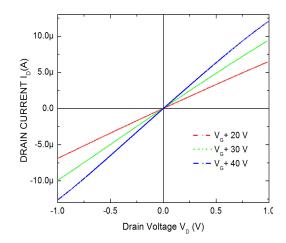

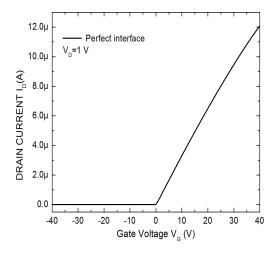

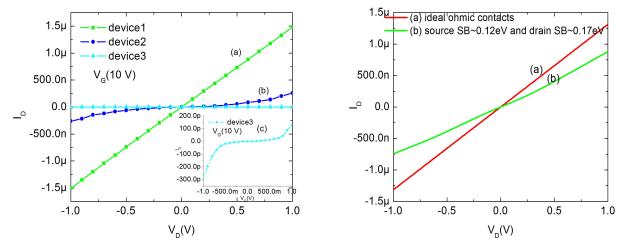

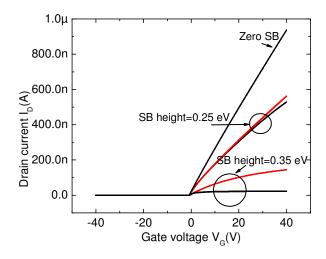

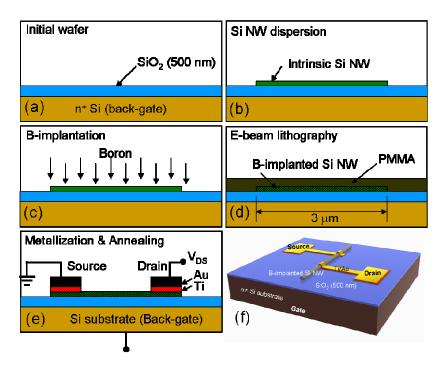

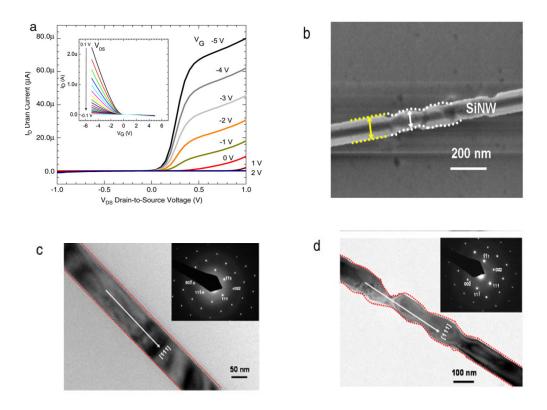

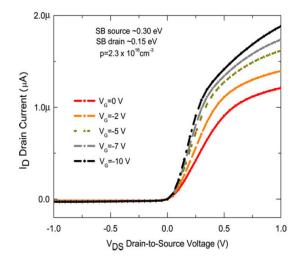

The experimental work is presented in chapter three and four. In chapter three, we present our efforts on SiC nanowire growth (section 3.2) starting either from CNTs or Si NW and converting them to SiC by exposing them in Si or C respectively. In chapter four we describe the process for the transistor fabrication (section 4.2) and finally present the electrical characterization of devices based on SiC nanowires received from our collaborators (section 4.3). We analyzed the behaviour of NWFETs based on two different types of 3C-SiC nanowires, a) nanowire grown without catalyst in a convective furnace and b) nanowires grown in a home-made CVD system based on Vapor Liquid Solid (VLS) method (with catalyst assistance). Structural characterization of the nanowires, which includes SEM, TEM, XRD and Raman spectroscopy, is presented and reveals that both types of nanowires have similar quality in terms of crystal orientation ([111]), defects density, stacking faults etc. The initial substrate of a typical device was a highly doped Si wafer with a dielectric layer on top of it (usually SiO<sub>2</sub>). To electrically contact the nanowires, a two-step electron-beam lithography and a lift-off process were required. Back-gated 3C-SiC NWFETs were fabricated and the electrical characterization revealed electron conduction through the nanowires. Devices with either ohmic or Schottky contacts were observed leading to two different operation modes. Transistors with ohmic-like contacts manifest very weak gating effect and the device switching off is not achievable even for high negative gate voltages due to the high electron concentration along the nanowire. In contrast, the Schottky barrier (SB) at Source (S)/ Drain (D) regions acts beneficially for the FET performance by significantly suppressing the off current. At higher positive gate voltages, the Schottky barriers tend to be transparent leading to high (compared to ohmic case) transconductance and  $I_{ON}/I_{OFF}$  ratio, 3.88 nS and 2.81·10<sup>3</sup>, respectively. In the case of unintentionally highly doped nanowires, where the direct effect of the gate voltage on the accumulated carriers is negligible, SB-NWFET presents improved performance by suppressing the off current and indirectly modulating the drain current through the control of Schottky barriers transparency at source and drain regions. Both types of nanowires led to similar device electrical behaviour. The similar NW quality explains the almost identical performance of the devices based on differently grown 3C-SiC nanowires.

Two-dimensional Silvaco simulation package is incorporated in order to fit the experimental output and transfer characteristics (section 3.5.1). The custom drift diffusion model which was previously described (section 2.4.1), has not been used due to its long required calculation time as well as due to the fact that doping and interface defects could not be included in the simulations. The fitting process allows us to estimate, a) the quality of the nanowire/dielectric interface, b) the carrier concentration and mobility along the nanowire in both types of nanowires, catalyst free grown and catalyst based nanowires. Beside this, the various shapes of experimental I-V characteristics, such as completely linear, non-linear symmetric, non-linear asymmetric were simulated by adjusting the SB at source and drain regions. Possible origins for the different values of SBs from contact to contact are proposed.

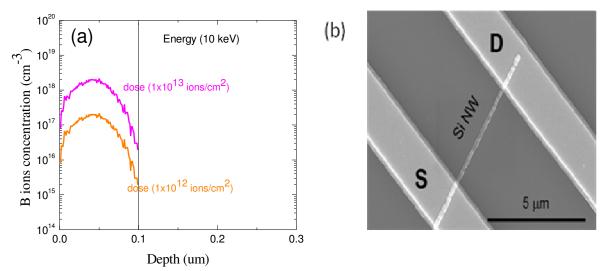

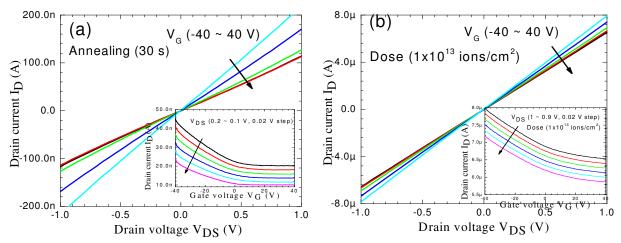

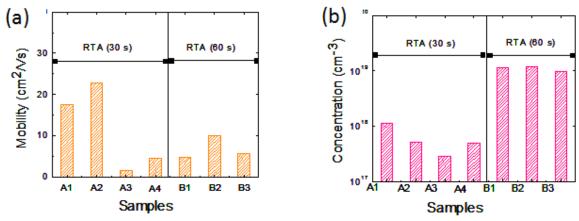

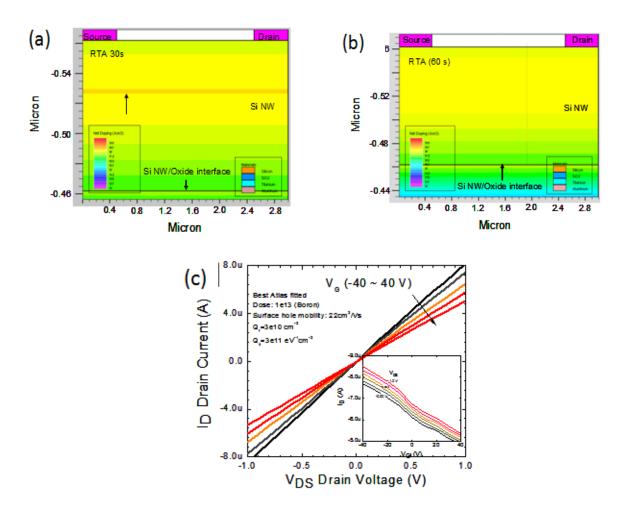

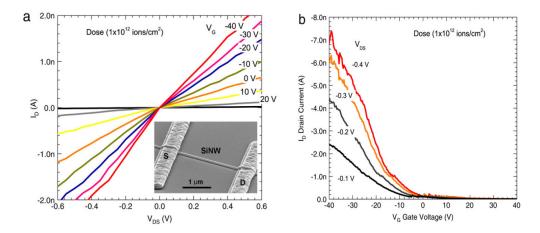

For cross checking our Silvaco-based fitting of experimental results, we also investigated the application of Silvaco simulation tool in Si nanowire FETs (4.4.2). More particularly, experimental FETs based on Boron-implanted Si nanowires were prepared. This subject could be very interesting for SiC NWs since implantation is a common technique of doping and its application could be obligatory in the case of SiC NW fabricated by conversion of Si NWs. These experiments incited us to investigate our SB SiC NWFETs which, as exposed above, presented the best electrical characteristics. Both the process steps of device fabrication and the device operation are simulated using Silvaco simulation tool. Again, an agreement, in terms of electrical characterization, between Silvaco and experiment is observed.

In conclusion, a combined theoretical and experimental study of SiC NW based FETs was presented. Theory predicted that SiC NWFETs are competitive to corresponding Si ones in terms of electrical performance (both in ballistic and quasi-ballistic regime), and therefore experimental SiC NW FETs could be realized and used, as an add on to Si mainstream technology, to some targeted applications such as high temperature and/or high operating voltage FETs. In the experimental part, two different SiC nanowire growth techniques were used. The first route was to convert CNTs to SiC and the other to grow Si NWs and convert them to SiC. Back gated NWFETs, based on nanowires received from our collaborators, were prepared and electrical characterization revealed two distinct device operation modes depending on the nature of the source and the drain contacts (ohmic or Schottky Barrier (SB) like). In the case of unintentionally highly doped nanowires, SB-NWFET presents improved performance by suppressing the off current and indirectly modulating the drain current through the control of Schottky barriers transparency at source and drain regions.

## **Acknowledgments**

My thesis program was accomplished under the co-supervision of the Institut Polytechnique de Grenoble, located at Minatec centre, and the Physics department of University of Crete/ FORTH Institute. Because of the thesis schedule, I was brought in contact and collaborated with numerous people from both laboratories. I am appreciated to numerous people for their valuable assistance along these three years. At this point, I will attempt to acknowledge the contribution of these persons to my work.

There is a well-known Greek dictum, which states that the beginning is the half of everything. Having this in my mind, I would like to mention the valuable assistance of my undergraduate and master dissertation supervisor, Prof. D. Tsoukalas. He mediated between National technical University of Athens (NTUA) and Institut Polytechnique de Grenoble (Grenoble INP) in order to overcome the bureaucracy and be possible to catch the deadline and receive the French fellowship for my PhD elaboration. I would like to thank my two thesis supervisors, Prof. E. Bano from Grenoble INP and Dr K. Zekentes from FORTH Institute, for their continuous assistance and guidance during my whole thesis.

I am greatly appreciated to Dr M. Bescond (L2MP-CNRS), Dr S. Poli (ARCES, University of Bologna) and Dr M. Pala (Grenoble INP) for providing me the initial numerical code dedicated to Silicon nanowires and supervising my simulation results. I would like to thank Dr A. Andriotis (IESL, FORTH) for his valuable comments and corrections on our theoretical work. Without the mediation of Prof L. Montes (Grenoble INP), it would not be possible to have in my possession 3C-SiC nanowires and process them in order to measure their electrical transport properties. Prof L. Montes arranged the collaboration between our group and the group of Prof. D. Cornu (IEM UMR-Université Montpellier 2) and we received the initial quantity of 3C-SiC nanowires. During my stay at FORTH Institute, I performed numerous experiments for Si and 3C-SiC nanowire growth. Most of this work was accomplished in the laboratory of Dr A. Lappas (FORTH Institute). I would like to thank him for allowing my entrance in his lab and assisting me to build the experimental setup. Many experiments for SiC nanowire growth through conversion of Silicon nanowires to SiC nanowires were also performed in Grenoble. I am grateful to Dr T. Baron (CEA-LETI) for providing me vertically grown Silicon nanowires, and to Prof. A. Mantoux for allowing to me to use their home made CVD system for the conversion experiment. The whole process for fabricating the nanowire FETs was performed in the Plateforme Technologique Amont (PTA), Grenoble. I would like to thank the technical director of this lab, Mr T. Haccart, for training me in order to be

able to use the clean room facilities. It would not be possible to be trained in so short time period without the valuable assistance and guidance of Dr G. Katsaros from INAC SPSMS LaTEQS, CEA/France. Finally, I am grateful to Prof. S. K. Lee (NDSL, S. Korea) and his group members for fruitful discussions on device fabrication. I was firstly introduced to nanowire device fabrication processes while I was visiting their group in S. Korea.

I feel indebted to all my colleagues. From Grenoble: Xu Xin, Dr A. Tzormpantzoglou, I. Pappas, Dr Brice Ivira, Dr Bogdan Bercu, Dr N. Camara, N. Mathioudakis and H. Isra. From FORTH: G. Dialynas, C. Koliakoudakis, S. Tsintzos, M. Trichas, F. Kalaitzakis, G. Tsiakatouras and A. Pantazis.

Last but not least, I am grateful to my fiancée Maria and my family. I have no way to thank them for their invaluable presence in my life and especially Maria's patience while I was travelling between France and Greece these 3 years, but to dedicate this dissertation to them.

## **Citations to published work**

### International Journals

- 1. **K. Rogdakis**, E. Bano, L. Montes, M. Mikhael Bechelany, D. Cornu and K. Zekentes, "Schottky barrier 3C-SiC nanowire field effect transistor", *Submitted to Nanotechnology* (2010)

- 2. **K. Rogdakis**, S. Poli, E. Bano, K. Zekentes and M. G. Pala, "Phonon and surface roughness limited mobility of gate-all-around 3C-SiC and Si nanowire FETs", *Nanotechnology* **20** 295202, (2009)

- 3. S. K. Lee, S. Y. Lee, **K. Rogdakis**, C. O. Jang, D. J. Kima, E. Bano, K. Zekentes, "Si Nanowire p-FET with asymmetric source-drain I-V characteristics", *Solid State Communications* **149**, 461-463, (2009)

- 4. S.Y. Lee, C. O. Jang, D. J. Kim, J. H. Hyung, **K. Rogdakis**, E. Bano, K. Zekentes and S. K. Lee, "Fabrication of Ion-implanted Si Nanowire p-FETs", *J. Phys. Chem. C* **112** 13287–13291, (2008)

- 5. **K. Rogdakis** S. Y. Lee, M. Bescond, S. K. Lee, E. Bano and K. Zekentes, "3C-SiC nanowire FET: An experimental and theoretical Approach", *IEEE Transactions on Electron Devices* **55** 1970-1976, (2008)

- K. Rogdakis, M. Bescond, E. Bano and K. Zekentes, "Theoretical comparison of 3C-SiC and Si nanowire FETs in ballistic and diffusive regimes", *Nanotechnology* 18 475715, (2007)

## <u>Refereed Proceedings in International Conferences</u>

- 7. **K. Rogdakis**, E. Bano, L. Montes, M. Mikhael Bechelany, D. Cornu and K. Zekentes, "Field effect transistors based on catalyst-free grown 3C-SiC nanowires", will be published in Materials Science Forum, presented in ICSCRM (2009), Nuremberg, Germany

- 8. **K. Rogdakis**, M. Bescond, E. Bano and K. Zekentes, "Theoretical comparison of 3C-SiC and Si nanowire FETs in ballistic regime", *Materials Science Forum* vols. 600-603 579-582, (2009)- presented in ICSCRM (2007), Otsu, Japan

- 9. **K. Rogdakis**, S. Y. Lee, D. J. Kim, S. K. Lee, E. Bano and K. Zekentes, "Effect of Source and Drain contacts Schottky Barrier on 3C- SiC nanowire FETs I-V characteristics", *Materials Science Forum* vols. 615-617 235-238, (2009) presented in ECSCRM (2008)

- 10. **K. Rogdakis**, S. Poli, E. Bano, K. Zekentes and M. G. Pala, "Backscattering coefficient in 3C-SiC gate-all-around nanowire FETs", will be published in IEEE Xplore library, presented in IEEE NANO conference, (2009)

# Chapter one: Bibliography review on nanowire growth and related devices

## **Table of contents**

| <b>1.1 Introduction</b> p. 20                                  |                                                  |  |  |  |

|----------------------------------------------------------------|--------------------------------------------------|--|--|--|

| 1.2 One-dimensional material growth and basic propertiesp. 23  |                                                  |  |  |  |

| 1.2.1                                                          | Vapor phase synthesisp. 24                       |  |  |  |

| 1.2.2                                                          | Thermal evaporationp. 27                         |  |  |  |

| 1.2.3                                                          | Template-assisted Synthesis and alignmentp. 29   |  |  |  |

| 1.2.4                                                          | Alternative nanowire fabrication techniquesp. 30 |  |  |  |

| 1.2.5                                                          | Heterostructures of nanowiresp. 34               |  |  |  |

| 1.2.6                                                          | Properties of semiconductor nanowiresp. 35       |  |  |  |

| 1.3 Nanowire-based transistorsp. 37                            |                                                  |  |  |  |

| 1.3.1                                                          | General characteristicsp. 37                     |  |  |  |

| 1.3.2                                                          | Device operation modep. 44                       |  |  |  |

| 1.4 3C-SiC nanowires: Growth, properties and applicationsp. 47 |                                                  |  |  |  |

| 1.4.1                                                          | Introductionp. 47                                |  |  |  |

| 1.4.2                                                          | Growth of 3C-SiC nanowiresp. 47                  |  |  |  |

| 1.4.3                                                          | 3C-SiC NWFETsp. 52                               |  |  |  |

| 1.4.4                                                          | Other applications of 3C-SiC nanowiresp. 53      |  |  |  |

| 1.5 Referencesp. 55                                            |                                                  |  |  |  |

## Chapter one: Bibliography review on nanowire growth and related devices

During the last half century, a dramatic downscaling of electronics has taken place, a miniaturization that the industry expects to continue for at least a decade. In this chapter we present efforts to use one dimensional semiconductor nanowires grown either with top-down or bottom-up techniques in order to bring new, high-performance nanowire devices as an add-on to mainstream Si technology. The nanowire approach offers a coaxial gate-dielectric channel geometry that is ideal for further downscaling and electrostatic control, as well as heterostructure-based devices on Si wafers. Devices based on such materials are, however, still in an embryonic stage from an industrial point of view. Whether they will really have an impact on future post- CMOS technology depends on more factors than just superior single-device performance. From the history of the semiconductor industry, we have learned that only those technologies that can be integrated and scaled up for large hierarchical systems will survive and have impact.

This chapter is divided into three main parts (section 1.2, 1.3 and 1.4). After an introduction (section 1.1), the first two parts (section 1.2 and 1.3) are addressing important steps toward the implementation of semiconductor nanowire devices. The first part (section 1.2) describes various aspects of nanowire growth, understanding and ultimately controlling their properties. This is followed by the second part (section 1.3) discussing the development and optimization of new nanowire-based devices mainly focusing on field effect transistors. We briefly cover the importance of characterizing and extracting important physical properties in order to evaluate and optimize nanowire growth and processing. Potential devices that can benefit from being built around nanowires then need to be identified and characterized, which is briefly described. In part three (section 1.4), we present the work published by other groups on 3C-SiC nanowires growth, properties and their applications. Again, the main device application is a nanowire-based transistor, which is the central subject of focus of this thesis.

## 1.1 Introduction

The rapid development of integrated circuit technology is primarily due to MOSFET downscaling trends that have continued to the present day. However, silicon-based MOS

technology is expected to face fundamental limits in the near future, and therefore, new types of nanoscale devices are being aggressively investigated. The manufacture of silicon based chips is based on a, so called, "top down" approach whereby the materials used to make the devices are first deposited on the chip and then structured using optical (or electron-beam) lithography and etching. In this way, a large number of layers can be built up to connect the transistors that are constructed from the topmost part of the single crystal silicon wafer. An alternative to the "top down" method is the use of self-organization in which large complex structures are constructed from smaller building blocks, e.g., molecules. This approach is referred to as "bottom up" and includes molecular self-assembly and the generation of uniform crystalline structures such as carbon nanotubes (CNTs) and nanowires (NWs).

Recently, various semiconductor NW devices have drawn much attention because of their possible use in future electronics and optoelectronics applications. Continued MOSFET scaling has led to the study of non-planar FET geometries that can provide better short channel control than conventional planar FETs. In particular, gate-all-around (GAA) or surround gate FETs with a thin NW channel can provide superior electrostatic characteristics that will allow continued scaling beyond what is possible with planar technology (providing also the possibility of a 3-D chip configuration).

Semiconductor NWs represent unique materials for exploring new emergent phenomena at the nanoscale [1.1]. In the physics of nanoscale structures, quantum effects play an increasingly prominent role. Quantum wires have demonstrated interesting electrical transport properties that are not seen in bulk materials. This is because, in quantum wires, electrons could be quantum-confined laterally and thus could occupy discrete energy levels that are different from the energy bands found in bulk materials. Due to low electron density and low effective mass, the quantized conductivity is more easily observed in semiconductors, e.g., Si and GaAs, than in metals. In addition to the opportunity to describe the new physics demonstrated by nanowires, much effort has been devoted for fabricate high-quality semiconductor nanowires by employing different techniques due to the importance of semiconductor materials to the electronics industry. The most popular technique used to fabricate semiconductor artificial structures with feature sizes in the sub-100 nm range is the ebeam lithography [1.2], which involves tedious processes of photo-resist removal, chemical or ionbeam etching and surface passivation, etc. On semiconductor nanostructures, etching processes always lead to significant surface damage and roughness, and thus surface states are introduced to the nanostructures. Such damage may not be serious for the structures in the micrometer range. However, structures with dimensions in the nanometer range are very sensitive to the surface states or the impurities induced by fabrication processes. One-dimensional (1D) nanostructures formed "naturally" (self-organized growth) without the aids of ex situ techniques, such as chemical etching, are desirable not only in fundamental research but also in future nanodevice design and fabrication. Most bottom-up approaches are statistical by nature and are lacking the fidelity of top-down fabrication. On the other hand, bottom-up approaches for making nanoscale devices circumvent some of the fabrication challenges and the high cost of equipment that are associated with established top-down CMOS processing. Acquiring and maintaining such big-ticket infrastructure that is prone to becoming obsolete at a rapid rate is out of bounds to most universities and even too many corporations. Therefore, there is a great need to focus on bottom-up fabrication methods for NW-based devices since they enable a wider range of academic institutions, laboratories, and corporations to participate and contribute to the growth of NW related electronics devices.

A well-known self-organized growth mechanism for preparing nanowires is the vapor-liquid-solid (VLS) process (also known as metal catalytic growth [1.3]). This technique can produce freestanding crystalline nanowires of semiconductor and metal oxide materials with fully controlled nucleation sites and diameters from pre-formed metal catalysts. Since the 1960s, semiconductor whiskers grown by this technique [1.3] have been extensively studied. In recent years, various new techniques have been developed to realize 1D nanostructures, such as laser-assisted chemical vapor deposition (CVD) [1.4], oxide-assisted CVD (without a metal catalyst) [1.5], thermal CVD [1.6], metal-catalyzed molecular beam epitaxy (MBE) [1.7] and chemical beam epitaxy (CBE) [1.8]. Although the number of various kinds of 1D nanostructures fabricated via different techniques increases dramatically every year, our understanding of the basic process of 1D nanostructure formation has not reached maturity. How to fabricate desired 1D nanomaterials with tailored atomic structures and how to integrate functional nanostructures into devices are still challenging issues for materials scientists. For 1D semiconductor nanomaterials to have wide practical applications, however, many areas require further pursuing. Integration on Si is essential for nanowires to be of interest for large-scale electronic applications.

Among the different materials considered for growing NWs, silicon has been studied extensively due to its compatibility with conventional CMOS technology. Si NWs with diameters as small as one nanometer have been grown successfully. Ge NWs are also of particular interest due to their higher carrier mobility. NW-based transistors have also been demonstrated using a number of other materials, chief among these are ZnO, SnO, SiC, InP, GaN, other III–V compounds, and conducting polymers [1.9]. Quantum confinement effects make modeling of NW transistors a complex problem [1.10]. While there are many studies in the literature on the modeling of NW transistors based on non-equilibrium Green's functions or Monte Carlo approaches, the physics

related to the operation of NW transistors needs to be well articulated so that simple compact models, including ballistic transport and realistic subband parameters, can be developed for circuit design using SPICE-like simulators.

Special field of applications (e.g. amplifiers used in wire-less telecommunications), demands devices with high power and high temperature operation and as a consequence the usage of wideband-gap semiconductors is urgent. Recently, the growth and characterization of one-dimensional nanostructures (nanowires, nanorods, nanotubes) of wideband-gap semiconductors have been studied due to their potential for applications in nanoelectronics, sensors, batteries, and field emission displays (FEDs) [1.11-1.13]. Among the wideband-gap materials, SiC presents high thermal conductivity, high breakdown electric field, high electron drift velocity, high Young's modulus and hardness, high melting temperature, excellent oxidation and corrosion durability, high strength at elevated temperatures, good thermal shock resistance and excellent chemical and physical stability (table 1.1). The native oxide is silicon dioxide, which makes SiC more compatible with Si technology. SiC NWs combine the above properties of 1D material with that of SiC and electronic devices based on SiC NW are expected to present concrete advantages in terms of dissipated power, stability and high voltage operation in comparison to their Si (Ge) counterparts.

Si GaAs 4H-SiC 6H-SiC 3C-SiC GaN Diamant  $E_g(eV)$ 1.1 1.4 3.36 3.02 2.4 3.4 5.5 V<sub>sat</sub> (cm s<sup>-1</sup>)  $1 \, 10^7$  $2 \, 10^7$  $2 \, 10^7$  $0.8 \ 10^7$  $2.5 \ 10^7$  $1.5 \ 10^7$  $2.7 \cdot 10^7$  $E_c(V m^{-1})$  $0.4 \ 10^6$  $0.4 \ 10^6$  $4\ 10^{6}$  $4 \, 10^6$  $3 \ 10^6$  $5 \, 10^6$  $10^{7}$  $\mu$  (cm<sup>2</sup>/Vs) 1000 900 1100 6000 800 370 2200  $\sigma_{\text{therm}} (WK^{-1} \text{ cm}^{-1})$ 1.5 0.5 4.9 4.9 4.9 1.3 20

Table 1.1 Properties of SiC compared to other semiconductors.

## 1.2 One-dimensional material growth and basic properties

Most semiconductor NWs are produced using the VLS growth method that has been generalized and expanded to a host of semiconductor materials by Lieber's group. VLS NWs require a metal nanoparticle to seed NW growth, and NWs are often prepared as a powder or as a

surface-supported film. While some parameters, such as the concentration of dopants or the NW length, are difficult to be controlled, novel materials, such as core-shell or branched NWs, can be prepared. In the first part of this section, we will review the bottom up nanowire growth methods, which are based on VLS mechanism, the oxide assisted growth (OAG) and the template assisted method. Both the alumina-template and the VLS-synthesized NWs can be prepared with an alternating and controllable stoichiometry along the long axis of the NW. After that, we will refer to growth techniques, which follow the top-down process such as, the superlattice nanowire pattern transfer method (SNAP) and nanoimprint. Most NWs are studied for their electronic (or optoelectronic) properties. In the last part, we present the basic properties of nanowires, including electrical, thermal and properties due to their 1D structure and quantum confinement and summarize the general conclusions.

### 1.2.1 Vapor phase synthesis

#### Introduction

Among all vapor-based methods, those employing the VLS mechanism seem to be the most successful in generating large quantities of nanowires with single crystalline structures. This process was originally developed by Wagner & Ellis to produce micrometer-sized whiskers in the 1960s [1.3], later justified thermodynamically and kinetically, and recently re-examined by Lieber, Yang, and other researchers to generate nanowires and nanorods from a rich variety of inorganic materials [1.14.1.15]. Several years ago, Yang et al. used in situ transmission electron microscopy (TEM) techniques to monitor the VLS growth mechanism in real time [1.18]. A typical VLS process starts with the dissolution of gaseous reactants into nanosized liquid droplets of a catalyst metal, followed by nucleation and growth of single-crystalline rods and then wires. The onedimensional growth is induced and dictated by the liquid droplets. The growth direction should correspond to the lowest energy facet of the crystal being grown. This is the most common case for nanowire growth. The collector (catalyst seed)/crystal interface forms on the close packed low energy planes of the crystal. For example in Diamond and Zinc blende crystal structures these are under most conditions the {111} planes and preferred growth directions are the <111> directions and for Wurtzite crystals the similar <0001> direction is most common. Exceptions to this general trend have been reported. These exceptions can be grouped depending on why the nanowires do not grow perpendicularly to the lowest energy facet [1.16]. For example, the growth direction has a strong diameter dependence that the smallest-diameter nanowires grow primarily along the (110) or (100) direction, whereas larger nanowires grow along the (111) direction [1.15]. There is also the possibility to have a lack of mobility of the collector (catalyst seed). The nanowire then grows in the direction of the original interface [1.17].

## Vapour Liquid Solid mechanism

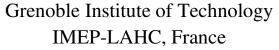

The VLS mechanism is based on metal catalysts. Each liquid droplet serves as a virtual template to limit the lateral growth of an individual wire. The metal clusters play a very important role in determining the final size and position of nanowires grown on the substrate. This feature of VLS growth process provides a method for controlling the size and position of nanowires by controlling the size and position of the metal catalyst. In this paragraph, the main steps of nanowires growth based on VLS mechanism are schematically described. The main steps are described schematically below in figure 1.1:

Figure 1.1 VLS mechanism steps: i) before the metal catalyst deposition, a thermal oxide is developed on the substrate. The oxide  $(SiO_2)$  has mainly an insulating role, ii) the thermal annealing allows the formation of the catalyst seeds. The molecules of the catalyst shrink under high temperature and a catalyst seed appears. iii) The VLS mechanism allows a eutectic melt formation and thus a preferential site for gas absorption. The nanostructure grows by precipitation from the catalyst interface.

The core of the VLS mechanism is the introduction of a liquid-solid interface in vapor phase-based growth, which breaks the symmetry of the isotropic crystal, making it to grow in a 1D structure. A metal particle (Au, Pt, or Ni) is utilized to form a liquid alloy with the material from the substrate or with material supplied in the vapor phase. At a certain temperature, the composition of this alloy will be in equilibrium. When more growth material is supplied at this temperature, the

alloyed particle becomes supersaturated, which results in nucleation and growth. The metal particle will not be consumed during growth and can therefore be seen as a catalyst for 1D growth. The diameter of the wire is dictated by the size of the liquid particle and remains essentially unchanged during the entire growth (this is not true for all cases, see next section: Pressure effect-MBE experiments). The major requirement on the metal in VLS growth is that it must form a liquid solution with the growth material at the growth temperature, and be able to create a super-saturation acting as driving force for crystallization of the nanowire material. This can be achieved if the metal and the growth material form a eutectic compound. The liquidus line ("melting temperature line") will have a minimum at a certain composition in a binary phase diagram for a eutectic compound. This minimum is called the eutectic point.

### Pressure effect- MBE experiments

Until recently, researchers thought that metal seeds size remains essentially unchanged during the entire process of VLS based nanowire growth. Hannon et al. [1.19] reported in situ observations, under an electron microscope, of the growth of silicon nanowires in ultra-clean conditions. They showed that, under the ultra-clean, high-vacuum conditions of their special electron microscope, larger droplets grow at the expense of smaller ones. These smaller droplets then shrink away, preventing any further nanowire growth from them. This effect, known as Ostwald ripening, is named after Wilhelm Ostwald (1909 chemistry Nobel laureate) who explained the effect as resulting from a decrease in total surface energy that occurs when atoms are transferred by diffusion processes from smaller to larger crystals [1.20]. Such an energy-minimizing diffusion transfer requires the efficient transport of atoms between neighbouring gold droplets. This cannot occur through gaseous diffusion above the silicon wafer because of the extremely low vapor pressure of gold; equally, the transport of gold atoms through the bulk of the silicon is also negligible. Hannon et al. argued convincingly that the mode of transport is surface diffusion, which requires not only a high diffusivity of gold on the silicon surface, but also a high solubility of gold on the surface or in a thin surface layer. This would fit with what we know about the growth of silicon nanowires by MBE. This is a technique based on the VLS method, but in which silicon is supplied not as a gas but as a directed beam of atoms. Molecular-beam epitaxy usually requires an ultra-clean environment, and here the transport of silicon as well as that of gold occurs through diffusion on the silicon surface, not through the gas [1.20].

A tiny amount of oxygen, as it is present under most technological growth conditions but not in the ultra-clean, high-vacuum environment used in their experiments might efficiently block the diffusion path of gold on the silicon surface. This would render the gold droplets independent of each other, as has been assumed for the past 40 years. Today, the oxygen content of silicon wafers is exactly specified for the best possible gettering performance. Analogously, the indirect conclusion from the fact that Hannon and colleagues [1.19] observe an effect under highly controlled, low-vacuum conditions that is not observed under less severely controlled conditions could be that a little added oxygen impurity ,although not too much , is beneficial for silicon nanowire growth.

In another study by Schubert et al. [1.20], Si nanowhiskers in the diameter range of 70 to 200 nm were grown on (111)-oriented silicon substrates by MBE. The experimentally observed radius dependence of the growth velocity of the nanowhiskers is opposite to what is known for VLS growth based on CVD and can be explained by ad-atom diffusion on the surface of the whiskers. In the case of the CVD method as we referred previously, small droplets of metals like gold are forming low-temperature eutectic liquids with silicon acting as a seed for the whisker growth. The silicon is preferentially incorporated via the liquid silicon–metal droplet. It is characterized by silicon whisker growth at the whisker/droplet interface by the incorporation of Si atoms coming from the liquid droplet. However, the whisker growth by MBE has a strong surface-related Si diffusion component, which leads to a larger growth rate for nanowhiskers with a smaller radius. This is just opposite to what is well established in the case of CVD-grown nanowhiskers. One has to take into account that they investigated the MBE growth via a gold/silicon eutectic. The use of other metals/silicon eutectic systems might show a different behaviour.

#### 1.2.2 Thermal evaporation

Nanowire production in large quantities is required in order to be realistic the usage of NW devices as alternatives to standard Si technology. Several growth strategies have been proposed to achieve large-scale Si NW growth, most of them still requiring the presence of a metal catalyst to promote 1D nucleation as we already presented in the previous sections. With process temperatures usually exceeding 1000 °C, metal catalysts are mixed to the Si precursor vapor either by thermal evaporation or laser ablation. There is a need, however, to avoid the metal contamination potentially

arising from the residual catalyst particles. Removing the catalyst post growth may require complex and expensive purification treatments.

Nanowires and some interesting morphologies of nanostructures such as nanoribbons, nanotetrapods and comb-like structures can be grown by a simple method of thermal evaporation of solid source materials avoiding the usage of metal catalyst.

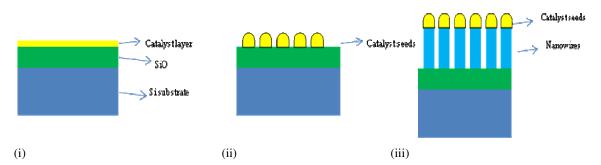

Figure 1.2 A simple experimental setup of the thermal evaporation method for synthesizing ZnO nanostructures. The source material is ZnO or a mixture of ZnO and carbon. Different forms of the ZnO nanostructures, e.g., nanowires and ribbons, grow in different temperature zones.

The growth mechanisms of many nanowires from thermal evaporation (without adding metal catalysts) are poorly understood. There are some special materials containing no metal elements that can also develop into nanowires from their oxide decomposition (setup similar with figure 1.2). Wang et al. [1.21] reported that SiO<sub>2</sub> largely enhanced Si nanowire growth. A model called oxide-assisted growth (OAG) was therefore proposed with evidence from experiments The OAG method provides a viable alternative for metal-free bulk production of Si NWs [1.22]. This method, however, has limitations for the shape control and uniformity of the resulting nanostructures. Thin and crystalline Si NWs are often coupled with partially or fully oxidized structures, resulting in crystalline Si spheres connected into chains by SiO<sub>2</sub> bridges of variable length. The advantages of the OAG technique are (1) its versatility, (2) the use of a relatively cheap experimental setup, (3) the fact that NW bundles of different materials can be easily synthesized without the need of potentially dangerous precursor gases, such as SiH<sub>4</sub> (4) the NWs are highly pure since no metal catalyst is involved and (5) doping of NWs can be easily achieved because the experimental setup for OAG of Si NWs is very similar to that of the laser ablation technique. Doping can be easily realized with the assistance of laser ablation of solid dopant materials during nanowire growth. Si nanowires fabricated by this method showed uniform diameters (about 20 nm) and their lengths were over several hundred micrometers. On the other hand, the high temperatures involved in the process do limit the substrate selection. NWs prepared by this technique are suitable for post growth processing, typically via dispersion in solution. Shape separation of as-grown NW bundles requires further processing. Ideally, one should engineer and optimize the synthesis to achieve 100% yield of the desired nanostructure morphology.

## 1.2.3 Template-assisted synthesis and alignment

The template-assisted synthesis of nanowires is a conceptually simple and intuitive way to fabricate nanostructures [1.23]. These templates contain very small cylindrical pores or voids within the host material, and the empty spaces are filled with the chosen material, which adopts the pore morphology, to form nanowires. In template-assisted synthesis of nanostructures, the chemical stability and mechanical properties of the template, as well as the diameter, uniformity and density of the pores are important characteristics to consider. Templates frequently used for nanowire synthesis include anodic alumina (Al<sub>2</sub>O<sub>3</sub>), nano-channel glass, ion track-etched polymers and mica films. A similar structure could be obtained by the template-mediated electrochemical synthesis of nanowire. The control over the location of the nucleation of nanowires in the electrochemical deposition is determined by the pore positions, which can be precisely controlled by imprint lithography [1.24], and by growing the template on a patterned conductive substrate that serves as a back electrode, different materials can be deposited in the pores at different regions of the template.

Ordering nanowires into useful structures is another challenge in order to harvest the full potential of nanowires for applications. Control of the position of a nanowire in the growth process is important for preparing devices or test structures containing nanowires, especially when involving a large array of nanowires. Post-synthesis methods to align and position nanowires include micro-fluidic channels [1.25], Langmuir–Blodgett assemblies [1.26], and electric-field assisted assembly [1.27]. The first method involves the orientation of the nanowires by the liquid flow direction and by the interaction of the nanowires with the sidewalls of the channel. The second method involves the alignment of nanowires at a liquid-gas or liquid-liquid interface by the application of compressive forces on the interface. The third technique is based on dielectrophoretic forces that pull polarisable nanowires toward regions of high field strength. The nanowires align between two isolated electrodes, which are capacitatively coupled to a pair of buried electrodes biased with an AC voltage. Once a nanowire shorts the electrodes, the electric field is eliminated, preventing more nanowires from depositing.

### 1.2.4 Alternative nanowire fabrication techniques

One critical step for the integration of nanowire devices in standard CMOS technology is the well position control and alignment. The NWs need to be organized into the desired device setting and that remains a challenge. Thus, the majority of NW studies have focused on single or few-device demonstrations, albeit often with spectacular resulting science. In this section, we will present alternative techniques for nanowire fabrication using this time top-down processes.

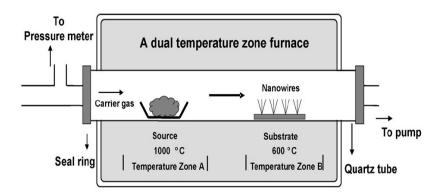

The superlattice nanowire pattern transfer method, or SNAP [1.28], provides an alternative to the aforementioned material growth methods, with its own unique advantages. Namely, SNAP can be harnessed to produce large arrays of virtually any type of NW; the only limitation is that the material from which the NWs are made must begin as a thin film. The SNAP technique resides between NW materials growth methods (the template for SNAP NWs is grown) and traditional top-down patterning methods. Figure 1.3 presents a flow diagram of the SNAP process. The process details can be found in [1.28].

Figure 1.3 The SNAP process: (A) A piece of a GaAs/Al<sub>x</sub>Gal<sub>x</sub>As superlattice serves as the master, (B) the superlattice is differentially etched, leaving a comb-like structure, (C) a SEM micrograph of an etched master is shown, (D) metal (typically Pt) is evaporated onto the master, (E) the master is dropped onto a substrate pre-coated with a thin epoxy layer, (F) the interface between the evaporated metal and the superlattice is etched, leaving nanowires on the surface, (G) dry etching translates the metal nanowire array into the supporting substrate. [1.28]

SNAP NWs have other advantages compared to standard methods. First, they inherit their doping levels, stoichiometry, crystallographic orientation, and thickness from the thin film substrate

from which they are made. This means, for example, that p-type and n-type Si NWs can be readily prepared side by side and that pn diodes and other devices are readily obtained. Some NW materials are uniquely available using SNAP, including insulators and certain metals. Second, the width and pitch of an array of SNAP NWs are translated from the precisely controlled film thicknesses and spacing of the superlattice template (figure 1.3a). Arrays containing 10<sup>3</sup> or more non-touching, well-conducting NWs with NW widths as thin as 7±2 nm and at a NW array pitch of 13±2 nm have been prepared. No other method can approach these dimensions with such precision. Third, SNAP NWs may be a millimetre long or longer. Materials grown NWs typically have lengths of 10 μm or less. Long NWs can exhibit unique physics, and they enable the construction of relatively largescale NW circuits. The SNAP process has evolved into a tremendously versatile method that is unmatched in terms of its capability for producing high-quality nanowire arrays. The development of the SNAP process over the past few years was largely driven by the goal of developing an electronics-grade manufacturing approach that operated at macromolecular dimensions. Several benchmarks toward achieving this goal, including the fabrication of ultrahigh density memory, novel de-multiplexing structures, and complementary symmetry nanowire logic circuits, have been achieved.

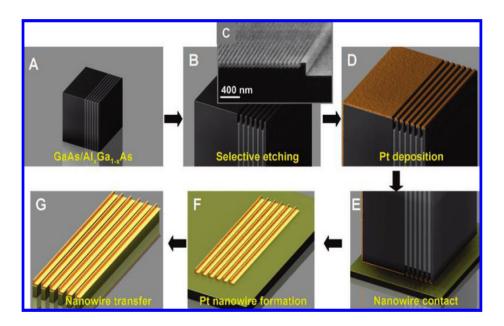

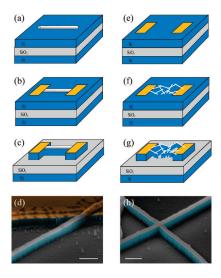

Another approach is the nanowire lithography (NWL) [1.29]. This technique uses chemically synthesized NWs (CS-NWs) or nanotubes as nanomasks to etch conformal one-dimensional (1D) structures into an underlying thin film. Initially, this method was applied to metal films or SiO<sub>2</sub>. Colli et al. in [1.30] showed that SiO<sub>2</sub> NWs are a simple and compatible system to implement NWL on Silicon on Insulator (SOI) films and silicon wafers in general. The process steps are shown in figure 1.4. This unique combination of bottom-up and top-down fabrication allows us to achieve nanoscale features on SOI wafers with minimum processing effort. They demonstrated a variety of device concepts and architectures, from highly conductive NW networks to aligned arrays of vertically stacked NWs, showing that the potential of this approach goes far beyond planar ultra miniaturization, extending to very-large-area pattering and 3D electronics [1.30].

The use of CS-NWs as nanomasks for SOI lithography has in principle several advantages over their direct implementation as active device elements. For example, even by using a poorly conducting network of CS-NWs as mask, the resulting conformal network etched into the underlying wafer would be monolithic, with single-crystalline bulk junctions, allowing maximum performance. In addition, a precise control over the doping concentration and crystallographic direction of CS-NWs is still lacking, while for SOI-NWs these parameters would be accurately

determined by the initial properties of the SOI substrate and the relative orientation of the NWL mask.

Figure 1.4 Complementary fabrication routes for direct-bridge (left) and network-like (right) NW devices using NWL on SOI layers. (a) Dispersion of fully oxidized Si NWs, (b) lithographic patterning of metal contacts, (c) etching of SOI by DRIE to define NW channels, (d) SEM micrograph of the final architecture, Different colours indicate different materials: (gray ) SiO<sub>2</sub>, (blue ) Si, (yellow) metal. Scale bar is 200 nm. (e) Patterning of metal pads on SOI, (f) deposition of SiO<sub>2</sub> NW network from solution by spin casting or ink-jet printing, (g) etching of SOI by DRIE. A monolithic Si network with single-crystalline bulk junctions is carved into the SOI layer. (h) SEM micrograph of a monolithic Si junction with overlapping NW masks. Scale bar is 200 nm. [1.30]

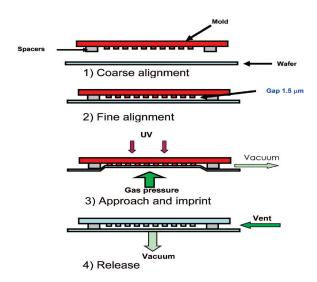

Another fabrication techniques which is not relied on bottom up growth method such as VLS mechanism, is the nanoimprint lithography (NIL) [1.31]. NIL was employed to fabricate crossbar structures with half-pitch down to 17 nm, isolated nanowires with 6 nm line width, and other functional applications for nanoelectronics and nanophotonics. While the resolution of nanoimprint has exceeded that of photolithography, it is still in the nascent phases of development. Fundamentally, nanoimprint is a mechanical contact rather than optical process, and therefore has a different set of challenges: how to preserve alignment and the subsequent overlay during mold approach, how to apply contact force uniformly, and how to prevent air from being trapped between the mask and the substrate (figure 1.5). Conventional approaches to meet those challenges have been to improve the mechanical stability of the system and to use ultra flat templates and doublesided polished wafers; these inevitably add cost that can potentially take away the value advantage of NIL. The mold or template is a 5 in. photo mask. The key enablers of the concept were spacers with precise heights deposited around the imprint areas. These spacers, which are located outside the perimeter of the imprint field (i.e., the streets), spatially offset the wafer from the mask while maintaining the two surfaces within a short distance and close parallelism during the fine alignment phase. These are critical both for keeping the mask and wafer alignment marks simultaneously in focus and for maintaining the alignment during approach and contact. Indeed the precise control of the spacer heights is critical, but this is not a challenge as today's deposition and etching processes easily give features with better than one nanometer thickness uniformity.

Figure 1.5 Schematic diagram of the nanoimprint module work flow. [1.31]

The nanoimprint process is divided into the following steps: (1) coarse alignment, (2) fine alignment, (3) approach and imprint, and (4) release (figure 1.5). Coarse alignment is performed without the mask and substrate in contact with an accuracy of 1  $\mu$ m, after which the mask (more specifically the spacers on the mask) are brought into contact with the substrate. During fine alignment, the spacers slide on the streets of the substrate to keep the mask and substrate exactly parallel with a gap the same as the spacer height. It is important to point out that the sliding occurs only during the fine alignment and its magnitude is <1  $\mu$ m; the spacers are designed to be located in the street area on the substrate, so that no patterns will be destroyed during spacer sliding. In approach and imprint, the air between the wafer and the mask is pumped out and gas pressure can be applied to the backside of the wafer (or the mask). The wafer and the mask are pressed onto each other because one or both bow under the applied pressure, transferring the patterns into the resist. The nanoimprint resist is then cured by exposure to Ultra-Violet (UV) light. To facilitate the release of the mask from the wafer, air is vented into the gap between the wafer and the mask and a vacuum is applied to the backside of the wafer, after which the imprint process is completed.

This approach has the following advantages: (1) there is no local mechanical movement other than wafer bowing during the approach and imprint, thus preserving the alignment during the process, (2) the mask and the substrate are in contact through the spacers during the fine

alignment step, so that the mechanical path between the nanoimprint mask and substrate is minimized for better mechanical stability, (3) the wafer-bowing method ensures that the imprint pressure is uniform and without lateral components in the imprint field, (4) during the imprint process, the centre of the imprint area reaches contact first and then spreads out to the edges, preventing air from being trapped between the mask and substrate and (5) the mold and wafer separation is facilitated simply by releasing the gas pressure.

#### 1.2.5 Heterostructures of nanowires

The preparation of nanowires with a graded composition or with a superlattice structure along their main axis was demonstrated by controlling the gas-phase chemistry as a function of time during the growth of the nanowires by the VLS method. Control of the composition along the axial dimension was also demonstrated by a template-assisted method, for example by the consecutive electrochemical deposition of different metals in the pores of an alumina template. Alternatively, the composition can be varied along the radial dimension of the nanowire, for example, by first growing a nanowire by the VLS method and then switching the synthesis conditions to grow a different material on the surface of the nanowire by CVD. This technique was demonstrated for the synthesis of Si/Ge and Ge/Si coaxial (or core-shell) nanowires, and it was shown that by a thermal annealing process, the outer shell could be formed epitaxially on the inner core.

Radial core/shell heterostructures can be achieved if dissociation of the reactants is promoted at the grown nanowire surface, analogous to the layered growth of planar heterostructures. Compared with NWs in the simple homogeneous form, core/shell heterostructure NWs offer better electrical and optical properties as they can now be tailored through band structure engineering [1.42]. Unlike radial heterostructures in which the shell growth does not involve reaction with the nanocluster catalyst, axial nanowire heterostructures can be obtained by alternative introduction of vapor phase reactants that react with the same nanocluster catalyst. A critical requirement of the axial nanowire heterostructure growth is then that a single nanocluster catalyst can be found which is suitable for growth of the different components under similar conditions [1.42].

#### 1.2.6 Properties of semiconductor nanowires

## Quantum confinement properties

By now, the phenomenon of charge carrier confinement in quantum dots, wires, and wells is familiar to researchers working with nanostructures. Quantum confinement is approximately described by simple particle-in-a-box type models, and its most distinctive signature is the  $1/d^n$  (where d is the diameter and  $1 \le n \le 2$ ) size dependence of the band gap in semiconductors. A recent detailed study of the effect of dimensionality on confinement in InP dots and wires [1.32] concluded that the size dependence of the band gap in wires is weaker than in dots by the amount expected from simple theory. However, the absolute band gap shifts in InP dots ( $\Delta E_g \sim 1/d^{1.35}$ ) and wires ( $\Delta E_g \sim 1/d^{1.45}$ ) did not follow the particle-in-a box prediction (i.e.,  $1/d^2$ ), demonstrating that accurate treatments of confinement require higher-order calculations to account for band structure.

#### Electrical transport regimes