Computer Science Department University of Crete

Network Intrusion Prevention on Multilevel Processing Architectures

Master's Thesis

Konstantinos Xinidis

4th November 2004 Heraklion, Greece

#### Network Intrusion Prevention on Multilevel Processing Architectures

by

Konstantinos Xinidis

Master's Thesis

Department of Computer Science University of Crete

#### Abstract

Network intrusion prevention systems provide an important proactive defense capability against security threats by detecting and blocking network attacks. This task can be highly complex, and softwarebased network intrusion prevention systems are currently not capable of handling high speed links.

This work focuses on the design and implementation of a high-performance, low-cost, flexible, and scalable network intrusion prevention system that combines software-based network intrusion detection engines and a network processor board. The network processor acts as a customized load balancer that cooperates with a set of content-based network intrusion detection engines in processing network traffic. We show that the components of such a system, if designed properly, can achieve high performance, by eliminating redundant processing and communication.

We describe a system architecture and present a prototype built using low-cost, off-the-shelf technology: an IXP1200 network processor evaluation board and commodity PCs. Our evaluation shows that our enhancements reduce the processing load of the network intrusion detection engines by at least 45%. The result is a system that can handle a fully-loaded Gigabit Ethernet link using at most four detection engines.

Keywords: intrusion detection, intrusion prevention, load balancing, network processorsThesis Supervisor: Evangelos P. MarkatosTitle: Associate Professor

#### Ιεραρχικές Αρχιτεκτονικές από Επεξεργαστές για Αποτροπή Εισβολέων σε Δίκτυα.

Κωνσταντίνος Ξυνίδης

Μεταπτυχιαχή Εργασία

Τμήμα Επιστήμης Υπολογιστών Πανεπιστήμιο Κρήτης

#### Περίληψη

Τα συστήματα αποτροπής εισβολέων σε δίκτυα παρέχουν την ικανότητα της πρόληψης και αμυντικής θωράκισης ενάντια σε απειλές ασφάλειας με το να ανιχνεύουν και να παρεμποδίζουν επιθέσεις που προέρχονται από το δίκτυο. Αυτό το έργο μπορεί να γίνει πολύ περίπλοκο, με αποτέλεσμα τα συστήματα αποτροπής εισβολέων σε δίκτυα που χρησιμοποιούν λογισμικό να αδυνατούν, προς το παρόν, να προστατεύσουν δίκτυα υψηλών ταχυτήτων.

Η εργασία αυτή ασχολείται με τον σχεδιασμό και την υλοποίηση ενός συστήματος αποτροπής εισβολέων σε δίκτυα, που χαρακτηρίζεται από υψήλες επιδόσεις, μικρό κόστος, ευελιξία και κλιμάκωση. Το σύστημα αυτό χρησιμοποιεί μηχανές ανίχνευσης εισβολέων υλοποιημένες σε λογισμικό και έναν επεξεργαστή δικτύου. Ο επεξεργαστής δικτύου συμπεριφέρεται σαν ένας ειδικά προσαρμοσμένος κατανεμητής φόρτου ο οποίος λειτουργεί σε συνεργασία με ένα σύνολο από μηχανές ανίχνευσης εισβολέων για να ελέγχει την κίνηση που διέρχεται απο το δίκτυο. Δείχνουμε ότι τα επιμέρους εξαρτήματα ενός τέτοιου συστήματος, εάν έχουν σχεδιαστεί κατάλληλα, μπορούν να επιτύχουν υψηλές επιδόσεις με την εξάλειψη της πλεονάζουσας επεξεργασίας και επικοινωνίας.

Περιγράφουμε την αρχιτεκτονική ενός συστήματος και παρουσιάζουμε ένα πρωτότυπο σύστημα που υλοποιήθηκε χρησιμοποιώντας χαμηλού κόστους και εύκολα προσβάσιμη τεχνολογία: έναν επεξεργαστή δικτύου που ονομάζεται *IXP1200* και οικονομικά PCs. Η αξιολόγηση του συστήματος δείχνει ότι οι βελτιστοποιήσεις μας μειώνουν τον φόρτο των μηχανών ανίχνευσης εισβολέων τουλάχιστον κατά 45%. Το αποτέλεσμα είναι ένα σύστημα που μπορεί να προστατεύσει ένα πλήρως φορτωμένο Gigabit δίκτυο χρησιμοποιώντας το πολύ τέσσερις μηχανές ανίχνευσης εισβολέων.

Επόπτης Μεταπτυχιακής Εργασίας: Ευάγγελος Π. Μαρκάτος

#### Acknowledgments

This work was financially supported by the Institute of Computer Science (ICS) of the the Foundation for Research and Technology - Hellas (FORTH), Heraklion, Greece. Besides ICS-FORTH, i would also like to thank all those people who helped me thoughout this work. First of all, i would like to thank my supervisor, Evangelos P. Markatos who gave me the possibility to work on the subject of network intrusion detection and prevention. I would also like to thank him for his guidance and support thoughout this work. Our discussions helped me understand how brilliant people are thinking and how a problem must be handled in order to be solved. His simple, yet scientific, way of thinking became valuable guide for me during the last few years.

In addition to prof. Evangelos P. Markatos, another person who helped me very much and i was very lucky to work with, is Konstantinos Anagnostakis. I truly believe that Konstantinos is the ideal co-worker. I would like to thank him for helping me stand on my foot when i was desperate during hard to solve problems. Also, his suggestions and observations proved invaluable.

I would also like to thank the rest of the Advanced Computing Systems group at ICS-FORTH for their help. Especially, i would like to thank Manolis Ploumidis for his help on implementing the packet caching technique on the *IXP1200*. Also, i would like to thank Spiros Antonatos, Mihalis Polihronakis, Olga Dokianaki, Thalia Vasiliadou and John Yannakopoulos for their corrections on parts of this thesis report.

I also thank my brothers, my parents and my grand-parents for their love and support all these years: nothing would have been accomplished without their contribution. Thanks are also to my friend Konstantinos Dimitriou for showing me the right way of thinking. His unbelievable way of solving problems showed me that there are people who are extraordinary clever and no matter how much we try, we cannot reach them. I therefore dedicate this work to him.

Στον φίλο μου Κωνσταντίνο Δημητρίου

Κι αν έφυγες απ΄ την ζωή πάντα θα σε θυμάμαι σαν ένα άστρο που ΄λαμπε μα έπεσενε χάμε.

## Contents

| 1 | Intr | oductio | n                                                        | 1  |

|---|------|---------|----------------------------------------------------------|----|

|   | 1.1  | Design  | Challenges                                               | 2  |

|   |      | 1.1.1   | High-Performance                                         | 2  |

|   |      | 1.1.2   | Flexibility and Scalablity                               | 3  |

| 2 | Bacl | kground | 1                                                        | 5  |

|   | 2.1  | Differe | ences Between NIPSes, NIDSes and Firewalls               | 5  |

|   | 2.2  | Introdu | action to Network Intrusion Prevention Systems           | 6  |

|   |      | 2.2.1   | What is an Intrusion?                                    | 6  |

|   |      | 2.2.2   | What is a Network Intrusion Prevention System?           | 6  |

|   |      | 2.2.3   | Basic Functions of a Network Intrusion Prevention System | 8  |

|   |      | 2.2.4   | Protecting the Network Infrastructure                    | 8  |

|   | 2.3  | A Desi  | gn Space for Network Intrusion Prevention Systems        | 10 |

|   |      | 2.3.1   | Useful Definitions                                       | 10 |

|   |      | 2.3.2   | Possible Implementations of a NIPS                       | 11 |

|   | 2.4  | Introdu | action to Network Processors                             | 14 |

|   |      | 2.4.1   | Parallel Processing                                      | 14 |

|   |      | 2.4.2   | Special Purpose Hardware                                 | 15 |

|   |      | 2.4.3   | Structure of Memory Architectures                        | 16 |

|   |      | 2.4.4   | On-Chip Communication Mechanisms                         | 16 |

|   | 2.5                                                             | Introdu                                                                          | action to Load Balancing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                                                                                 |

|---|-----------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                 | 2.5.1                                                                            | Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                                                                                                 |

| 3 | Arcl                                                            | hitectur                                                                         | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19                                                                                                                                 |

|   | 3.1                                                             | Archit                                                                           | ecture of <i>Digenis</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20                                                                                                                                 |

|   |                                                                 | 3.1.1                                                                            | Architecture of the NP-part of <i>Digenis</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21                                                                                                                                 |

|   |                                                                 | 3.1.2                                                                            | Architecture of the PC-part of <i>Digenis</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21                                                                                                                                 |

|   | 3.2                                                             | Descri                                                                           | ption of the Basic Functionality of <i>Digenis</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21                                                                                                                                 |

|   |                                                                 | 3.2.1                                                                            | Definition of a Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21                                                                                                                                 |

|   |                                                                 | 3.2.2                                                                            | Load Balancing Algorithm Used by <i>DigenisNP</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23                                                                                                                                 |

|   | 3.3                                                             | Descri                                                                           | ption of the Plug-ins of <i>Digenis</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25                                                                                                                                 |

|   |                                                                 | 3.3.1                                                                            | A Plug-In for Reducing Redundant Packet Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25                                                                                                                                 |

|   |                                                                 | 3.3.2                                                                            | A Plug-In for Reducing Redundant Packet Inspection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28                                                                                                                                 |

|   | 3.4                                                             | Limita                                                                           | tions of <i>Digenis</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31                                                                                                                                 |

|   |                                                                 | 3.4.1                                                                            | Portscan Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 32                                                                                                                                 |

|   |                                                                 |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                    |

| 4 | Imp                                                             | lementa                                                                          | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33                                                                                                                                 |

| 4 | <b>Imp</b><br>4.1                                               |                                                                                  | <b>Ition</b> nentation of the NP-part of <i>Digenis</i> on the <i>IXP1200</i> Network Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>33</b><br>33                                                                                                                    |

| 4 | -                                                               |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33                                                                                                                                 |

| 4 | -                                                               | Impler                                                                           | nentation of the NP-part of <i>Digenis</i> on the <i>IXP1200</i> Network Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33                                                                                                                                 |

| 4 | -                                                               | Impler<br>4.1.1                                                                  | nentation of the NP-part of <i>Digenis</i> on the <i>IXP1200</i> Network Processor Implementation of the Hash-Based Load Balancing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33<br>34                                                                                                                           |

| 4 | -                                                               | Impler<br>4.1.1<br>4.1.2<br>4.1.3                                                | Implementation of the Plug-in for Reducing Redundant Packet Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul><li>33</li><li>34</li><li>34</li><li>36</li></ul>                                                                              |

| 4 | -                                                               | Impler<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                                       | Implementation of the Plug-in for Reducing Redundant Packet Inspection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>33</li> <li>34</li> <li>34</li> <li>36</li> <li>37</li> </ul>                                                             |

| 4 | 4.1                                                             | Impler<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                                       | nentation of the NP-part of <i>Digenis</i> on the <i>IXP1200</i> Network Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>33</li> <li>34</li> <li>34</li> <li>36</li> <li>37</li> <li>42</li> </ul>                                                 |

| 4 | 4.1                                                             | Impler<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Impler                             | nentation of the NP-part of <i>Digenis</i> on the <i>IXP1200</i> Network Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>33</li> <li>34</li> <li>34</li> <li>36</li> <li>37</li> <li>42</li> </ul>                                                 |

| 4 | 4.1                                                             | Impler<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Impler<br>4.2.1<br>4.2.2           | nentation of the NP-part of Digenis on the IXP1200 Network Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <ul> <li>33</li> <li>34</li> <li>34</li> <li>36</li> <li>37</li> <li>42</li> <li>43</li> </ul>                                     |

| 4 | 4.1<br>4.2<br>4.3                                               | Impler<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Impler<br>4.2.1<br>4.2.2           | nentation of the NP-part of <i>Digenis</i> on the <i>IXP1200</i> Network Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>33</li> <li>34</li> <li>34</li> <li>36</li> <li>37</li> <li>42</li> <li>43</li> <li>43</li> </ul>                         |

|   | 4.1<br>4.2<br>4.3                                               | Impler<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Impler<br>4.2.1<br>4.2.2<br>Impler | nentation of the NP-part of <i>Digenis</i> on the <i>IXP1200</i> Network Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>33</li> <li>34</li> <li>34</li> <li>36</li> <li>37</li> <li>42</li> <li>43</li> <li>43</li> </ul>                         |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>Eval</li> </ul> | Impler<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Impler<br>4.2.1<br>4.2.2<br>Impler | nentation of the NP-part of <i>Digenis</i> on the <i>IXP1200</i> Network Processor          Implementation of the Hash-Based Load Balancing          Implementation of the Plug-in for Reducing Redundant Packet Transmission          Implementation of the Plug-in for Reducing Redundant Packet Inspection          Pseudo-code Description of <i>DigenisNP</i> Implementation of the Plug-in for Reducing Redundant Packet Inspection          Implementation of the Plug-in for Reducing Redundant Packet Inspection          Implementation of the Plug-in for Reducing Redundant Packet Transmission          Implementation of the Plug-in for Reducing Redundant Packet Transmission          Implementation of the Plug-in for Reducing Redundant Packet Inspection          Implementation of the Plug-in for Reducing Redundant Packet Inspection          Implementation of the Plug-in for Reducing Redundant Packet Inspection          Implementation of Additional Configurations | <ul> <li>33</li> <li>34</li> <li>34</li> <li>36</li> <li>37</li> <li>42</li> <li>43</li> <li>43</li> <li>43</li> <li>45</li> </ul> |

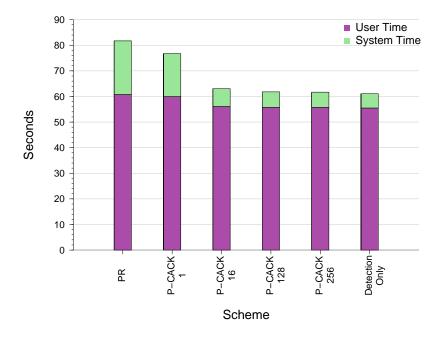

|   |      | 5.1.3         | Performance of <i>DigenisPCs</i>                             | 55 |

|---|------|---------------|--------------------------------------------------------------|----|

|   |      | 5.1.4         | Forwarding Latency of a <i>DigenisPC</i>                     | 59 |

|   |      | 5.1.5         | Forwarding Latency of <i>DigenisNP</i>                       | 62 |

|   |      | 5.1.6         | Memory Requirements                                          | 63 |

|   | 5.2  | Evalua        | tion of the Plug-in for Reducing Redundant Packet Inspection | 63 |

|   |      | 5.2.1         | Experimental Environment                                     | 63 |

|   |      | 5.2.2         | DUCache Hit Ratio                                            | 65 |

|   |      | 5.2.3         | Performance of <i>DigenisNP</i>                              | 67 |

|   |      | 5.2.4         | Performance of <i>DigenisPCs</i>                             | 71 |

| 6 | Rela | ited woi      | rk                                                           | 75 |

| 7 | Con  | clusions      | 5                                                            | 79 |

|   | 7.1  | Future        | Work                                                         | 80 |

|   |      | 7.1.1         | More Sophisticated Reduction of Redundant Inspection         | 80 |

|   |      | 7.1.2         | Structure of the NIDS                                        | 81 |

|   |      | 7.1.3         | HTTP Protocol Decoding on DigenisNP                          | 82 |

|   |      | 7.1.4         | Separating Server-Side and Client-Side Traffic               | 82 |

| 8 | Арр  | endix A       |                                                              | 85 |

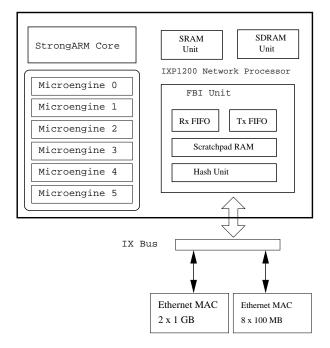

|   | 8.1  | The <i>IX</i> | P1200 Network Processor Overview                             | 85 |

|   |      | 8.1.1         | Microengines                                                 | 86 |

|   |      | 8.1.2         | An Immense Amount of Registers                               | 86 |

|   |      | 8.1.3         | Hardware Multithreading                                      | 87 |

|   |      | 8.1.4         | Hash Unit                                                    | 88 |

|   |      | 8.1.5         | Internal Buses                                               | 89 |

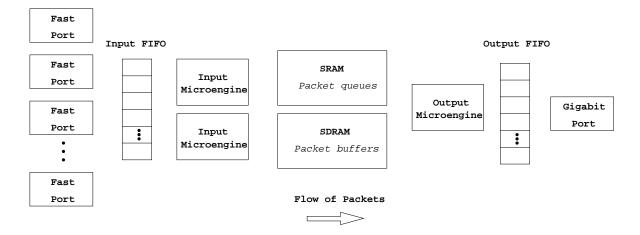

|   | 8.2  | Туріса        | l Packet Data Flow in the <i>IXP1200</i>                     | 89 |

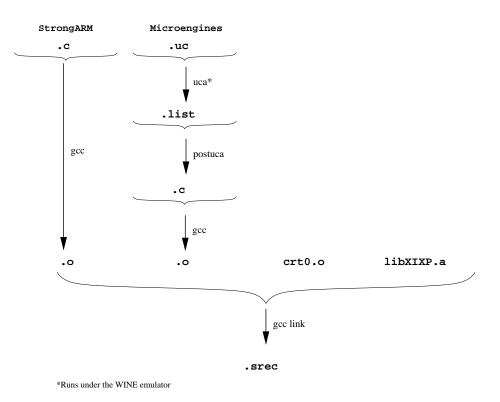

|   | 8.3  | Progra        | mming Languages                                              | 91 |

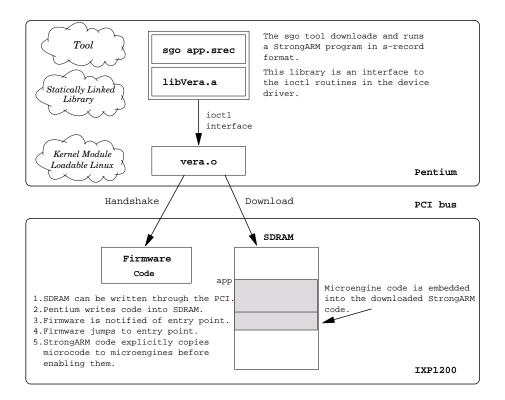

|   | 8.4  | Execut        | tion and Development Environment                             | 91 |

|   |      | 8.4.1         | Simulation Mode                                              | 92 |

|   |      | 8.4.2         | Hardware Mode                                                | 92 |

| 9 Appendix B |     | 97                  |    |

|--------------|-----|---------------------|----|

|              | 9.1 | Ethernet Data Rates | 97 |

## List of Figures

| 2.1 | A Typical Intrusion Scenario.                                                     | 7  |

|-----|-----------------------------------------------------------------------------------|----|

| 2.2 | Single Location Placement.                                                        | 9  |

| 2.3 | Multiple Locations Placement.                                                     | 9  |

| 2.4 | Possible Implementations of a NIPS.                                               | 11 |

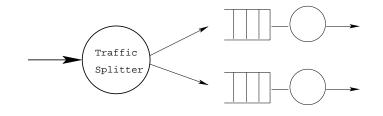

| 2.5 | A Load Balancing System.                                                          | 17 |

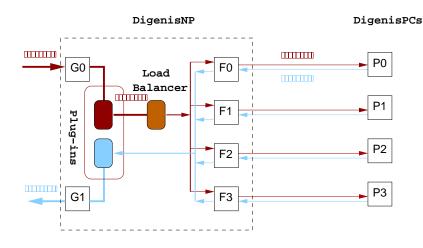

| 3.1 | Digenis Architecture.                                                             | 20 |

| 3.2 | ACK Packet Format.                                                                | 26 |

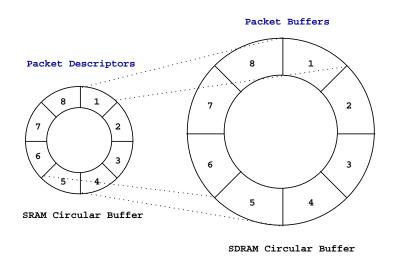

| 4.1 | SRAM and SDRAM Circular Buffers for Fixed-Size Packet Buffers                     | 35 |

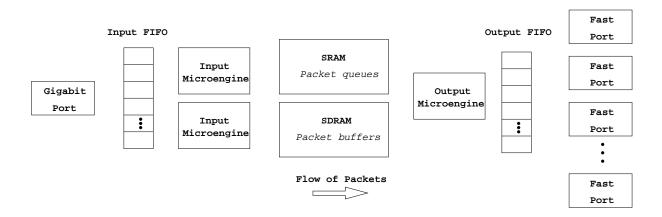

| 4.2 | The Forwarding Pipeline from the Gigabit Ethernet Port to the Fast Ethernet Ports | 38 |

| 4.3 | The Forwarding Pipeline from the Fast Ethernet Ports to the Gigabit Ethernet Port | 38 |

| 4.4 | Pseudo-code Running in Each Context Assigned to Gigabit Ethernet Input Processing | 39 |

| 4.5 | Pseudo-code Running in Each Context Assigned to Fast Ethernet Input Processing    | 40 |

| 4.6 | Pseudo-code of the Scheduler Thread for Gigabit Ethernet Output Processing        | 41 |

| 4.7 | Pseudo-code of the First Fill Thread for Gigabit Ethernet Output Processing       | 42 |

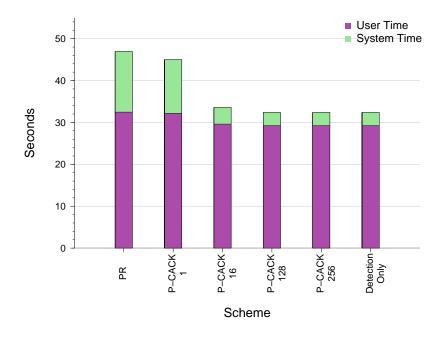

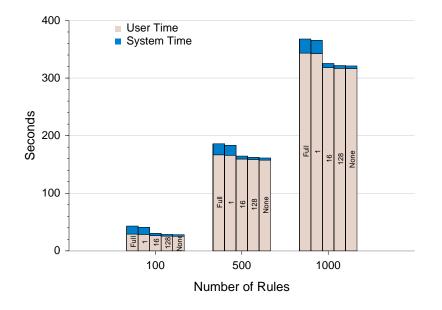

| 5.1 | Processing Cost of the <i>DigenisPC</i> (FORTH.WEB Trace).                        | 54 |

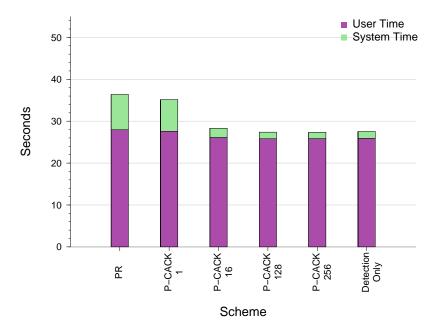

| 5.2 | Processing Cost of the <i>DigenisPC</i> (FORTH.LAN Trace)                         | 55 |

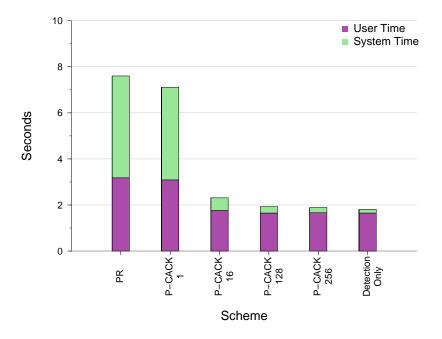

| 5.3 | Processing Cost of the <i>DigenisPC</i> ( <b>IDEVAL</b> Trace).                   | 56 |

| 5.4 | Performance of a <i>DigenisPC</i> using Incremental Number of Synthetic Rules     | 57 |

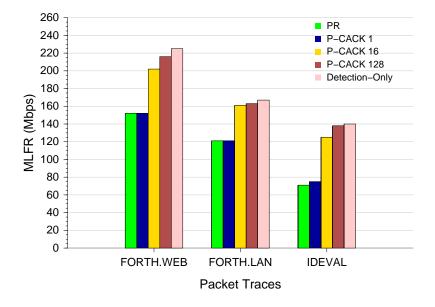

| 5.5 | Maximum Loss Free Rate (MLFR) of a <i>DigenisPC</i> using Default Rule-Set        | 58 |

| 5.6        | Processing Cost of the <i>DigenisPC</i> , with a Slower PC ( <b>FORTH.WEB</b> Trace) | 59       |

|------------|--------------------------------------------------------------------------------------|----------|

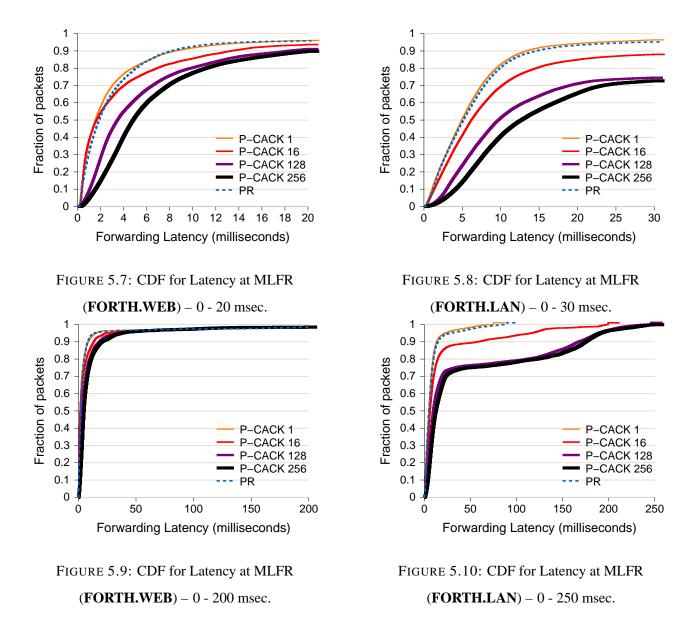

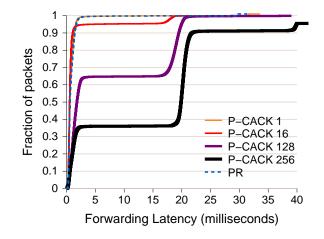

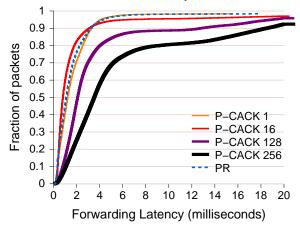

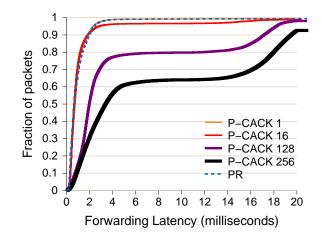

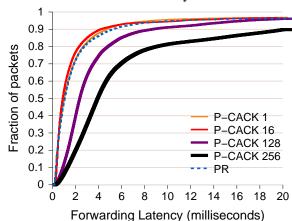

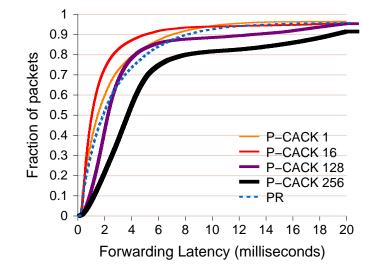

| 5.7        | CDF for Latency at MLFR ( <b>FORTH.WEB</b> ) – 0 - 20 msec                           | 61       |

| 5.8        | CDF for Latency at MLFR ( <b>FORTH.LAN</b> ) – 0 - 30 msec.                          | 61       |

| 5.9        | CDF for Latency at MLFR ( <b>FORTH.WEB</b> ) – 0 - 200 msec                          | 61       |

| 5.10       | CDF for Latency at MLFR (FORTH.LAN) – 0 - 250 msec                                   | 61       |

| 5.11       | CDF for Latency at 20% of MLFR.                                                      | 62       |

| 5.12       | CDF for Latency at 40% of MLFR.                                                      | 62       |

| 5.13       | CDF for Latency at 60% of MLFR.                                                      | 62       |

| 5.14       | CDF for Latency at 80% of MLFR.                                                      | 62       |

| 5.15       | CDF for Latency for all ACK Schemes at the MLFR of the PR Scheme.                    | 63       |

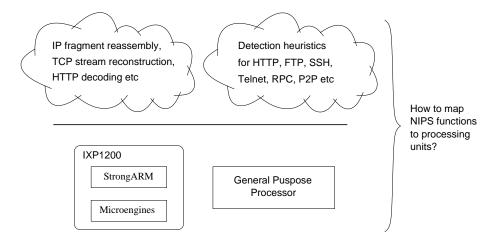

| 7.1<br>7.2 | Mapping of Functions to Processing Units.       Signatures of Snort for RPC Traffic. | 80<br>84 |

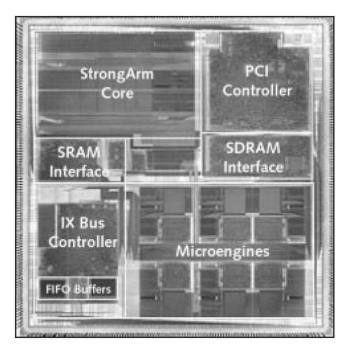

| 8.1        | The IXP1200 chip (Taken from Microprocessor Report, Volume 13, Number 12)            | 86       |

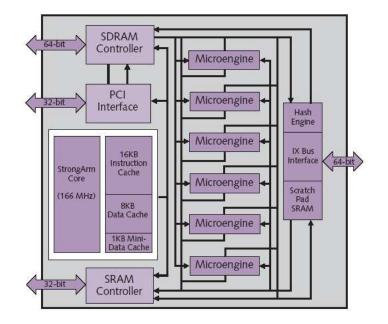

| 8.2        | The IXP1200 Intergrates Seven Microprocessor Cores on One Chip (Taken from Micro-    |          |

|            | processor Report, Volume 13, Number 12)                                              | 87       |

| 8.3        | Typical packet data flow in the <i>IXP1200</i>                                       | 89       |

| 8.4        | Microcode Example.                                                                   | 91       |

| 8.5        | Microengine C Example.                                                               | 92       |

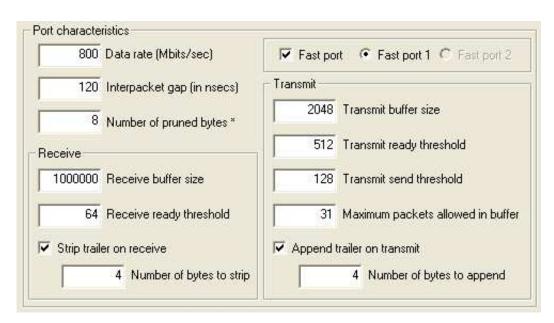

| 8.6        | Configuration of Gigabit Ethernet Port.                                              | 93       |

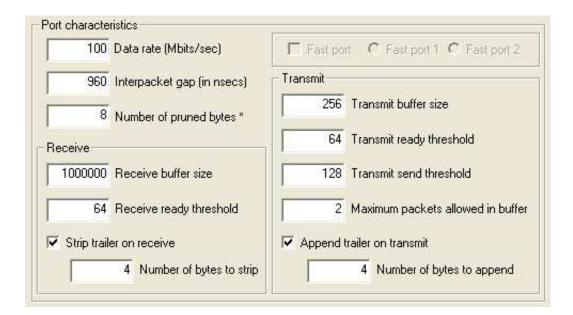

| 8.7        | Configuration of Fast Ethernet Port.                                                 | 93       |

| 8.8        | VERA's IXP1200 Toolchain.                                                            | 94       |

| 8.9        | Running an Executable Image on the <i>IXP1200EEB</i>                                 | 95       |

## List of Tables

| 2.1  | Characteristis of Possible Implementations of a NIPS.                        | 12 |

|------|------------------------------------------------------------------------------|----|

| 3.1  | ACK Packet Size.                                                             | 27 |

| 5.1  | Characteristics of the Packet Traces.                                        | 47 |

| 5.2  | Packet Size Distribution for <b>FORTH.WEB</b> Trace                          | 47 |

| 5.3  | Packet Size Distribution for FORTH.LAN Trace.                                | 47 |

| 5.4  | Packet Size Distribution for IDEVAL Trace.                                   | 47 |

| 5.5  | Utilization(%) of the Microengines, SDRAM and SRAM for 64-byte Packets       | 49 |

| 5.6  | Utilization(%) of the Microengines, SDRAM and SRAM for 512-byte Packets      | 49 |

| 5.7  | Utilization(%) of the Microengines, SDRAM and SRAM for 1024-byte Packets     | 49 |

| 5.8  | Utilization(%) of the Microengines, SDRAM and SRAM for 1518-byte Packets     | 49 |

| 5.9  | Utilization(%) of the Microengines, SDRAM and SRAM for Variable Size Packets | 50 |

| 5.10 | Utilization(%) of the Microengines, SDRAM and SRAM for 64-byte Packets       | 52 |

| 5.11 | FBI Pull Queue Fullness Statistics.                                          | 53 |

| 5.12 | FBI Push Queue Fullness Statistics.                                          | 53 |

| 5.13 | Hash Queue Fullness Statistics.                                              | 54 |

| 5.14 | Synthetic Rule Example.                                                      | 58 |

| 5.15 | Characteristics of the Packet Traces.                                        | 65 |

| 5.16 | Packet Size Distribution for IDEVAL Trace                                    | 65 |

| 5.17 | Packet Size Distribution for NASA.SYNTHETIC Trace.                           | 65 |

| 5.18 | <i>DUCache</i> Hit Ratio for <b>NASA.SYNTHETIC</b> Trace ( <i>DU</i> is Packet)                   | 66 |

|------|---------------------------------------------------------------------------------------------------|----|

| 5.19 | <i>DUCache</i> Hit Ratio for <b>IDEVAL</b> Trace ( <i>DU</i> is Packet)                           | 66 |

| 5.20 | <i>DUCache</i> Hit Ratio for <b>NASA.SYNTHETIC</b> Trace ( <i>DU</i> is <i>HDU</i> )              | 67 |

| 5.21 | <i>DUCache</i> Hit Ratio for <b>IDEVAL</b> Trace ( <i>DU</i> is <i>HDU</i> )                      | 67 |

| 5.22 | Utilization(%) of the Microengines, SDRAM and SRAM for 64-byte Packets                            | 68 |

| 5.23 | Utilization(%) of the Microengines, SDRAM and SRAM for 512-byte Packets                           | 68 |

| 5.24 | Utilization(%) of the Microengines, SDRAM and SRAM for 1518-byte Packets                          | 68 |

| 5.25 | FBI Pull Queue Fullness Statistics (64-byte Packets).                                             | 69 |

| 5.26 | FBI Push Queue Fullness Statistics (64-byte Packets).                                             | 69 |

| 5.27 | FBI Pull Queue Fullness Statistics (1518-byte Packets).                                           | 69 |

| 5.28 | FBI Push Queue Fullness Statistics (1518-byte Packets).                                           | 69 |

| 5.29 | Hash Queue Fullness Statistics (64-byte Packets).                                                 | 70 |

| 5.30 | Hash Queue Fullness Statistics (1518-byte Packets).                                               | 70 |

| 5.31 | Total Processing Time of <i>Snort</i> for <b>NASA.SYNTHETIC</b> Trace ( <i>DU</i> is Packet)      | 72 |

| 5.32 | Total Processing Time of <i>Snort</i> for <b>IDEVAL</b> Trace ( <i>DU</i> is Packet)              | 72 |

| 5.33 | Processing Cost (Seconds) of Fingerprint Generation and Cache Operations (DU is Packet).          | 72 |

| 5.34 | Processing Cost (Seconds) to Analyze All Packets in the Traces Containing Unique                  |    |

|      | Packets.                                                                                          | 73 |

| 5.35 | Total Processing Time of <i>Snort</i> for <b>NASA.SYNTHETIC</b> Trace ( <i>DU</i> is <i>HDU</i> ) | 73 |

| 5.36 | Total Processing Time of <i>Snort</i> for <b>IDEVAL</b> Trace ( <i>DU</i> is <i>HDU</i> )         | 73 |

| 5.37 | Processing Cost (Seconds) of Fingerprint Generation and Cache Operations (DU is HDU).             | 74 |

| 9.1  | Timing for Ethernet Packets.                                                                      | 98 |

| 9.2  | Maximum Packet Rates for Ethernet                                                                 | 98 |

| 9.3  | Maximum Bit Rates for Ethernet.                                                                   | 98 |

# Introduction

The increasing importance of network infrastructure and services along with the high cost and difficulty of designing and enforcing end-system security policies has resulted in growing interest in complementary, network-level security mechanisms, as provided by firewalls and network intrusion detection and prevention systems.

High-performance firewalls are rather easy to scale up to current edge-network speeds because their operation involves relatively simple operations, e.g., matching a set of Access Control List-type policy rules against fixed-size packet headers. Unlike firewalls, network intrusion prevention systems (NIPSes) are significantly more complex and, as a result, are lagging behind routers and firewalls in the technology curve. The complexity stems mainly from the need to analyze not just packet headers but also packet content and higher-level protocols. Moreover, the function of NIPSes needs to be updated with new detection components and heuristics, considering the progress in detection technology as well as the continuously evolving nature of network attacks.

Both complexity and the need for flexibility make it hard to design high-performance NIPSes. Application-Specific Integrated Circuits (ASICs) lack the needed flexibility, while software-based systems are inherently limited in terms of performance. One design that offers both flexibility and performance is the use of multiple software-based systems behind a hardware-based load balancer. Although such a design can scale up to edge-network speeds, it still requires significant resources, in terms of the number of software-based systems, the required rack-space, etc. It is therefore important to consider ways of improving the performance of such systems.

This thesis explores the role that high-speed network processors (NPs) can play in scaling up network intrusion prevention systems. We focus on ways of exploiting the performance and programmability of NPs for boosting network intrusion prevention. We describe the architecture of a high-performance, low-cost, flexible, and scalable NIPS that is composed of network processors and general purpose processors. We present the allocation of operations to components and the trade-offs we faced during designing and prototyping the system.

#### **1.1 Design Challenges**

We faced a number of design challenges in constructing our system with respect to performance, flexibility, and scalability:

#### 1.1.1 High-Performance

The primary metric of interest in the design of a NIPS is throughput. The goal here is to be able to operate at network speeds of at least 1 Gbit/s without packet losses. We assume that we cannot tolerate an undetected attack; therefore, the system must be capable of analyzing all the incoming traffic under the most stringent conditions.

A second important performance goal is minimizing the latency induced by the NIPS. There is a direct relationship between latency introduced by a networking device and the maximum throughput of TCP connections <sup>1</sup>. If the NIPS is to be used at the boundary between an enterprise network and the Internet, latencies in the order of a few milliseconds may be tolerable. If the NIPS is deployed internally, and the network needs to support high-bandwidth local services (such as file sharing, etc.) the latency

<sup>&</sup>lt;sup>1</sup> Recall that  $Throughput = \frac{Window}{RTT}$  where *Window* is the maximum TCP window size (default value is 64 Kbytes) and *RTT* is the round trip time in the network.

#### 1.1. DESIGN CHALLENGES

requirements are even more stringent.

Particularly, there is a critical value for the round trip time (RTT) of a packet in each network. If the latency is below this critical value, TCP throughput is unaffected – it is the line speed of the underlying network which becomes the bottleneck – above this critical value, however, TCP throughput is negatively impacted. The critical value for RTT in a network supporting Gigabit speeds is 0.5 milliseconds. Thus, if we want the throughput of TCP to be unaffected, we must ensure that the imported latency of our NIPS is smaller than 0.5 milliseconds. However, Gigabit Ethernet links, rarely carry only a single TCP connection. Rather, a Gigabit Ethernet link supports hundreds, if not thousands of TCP connections, and this multiplexing mitigates the impact of latency on the overall throughput of the link [16]. In other words, it is possible to import latency greater than 0.5 milliseconds without affecting the throughput of TCP connections.

#### 1.1.2 Flexibility and Scalablity

A NIPS needs to be flexible and scalable, both for scaling up to higher link speeds and more expensive detection functions, as well as for updating the detection heuristics. If the protection of a faster link or a more fine-grained detection is required, it would be desirable to reuse as much as possible of the existing hardware. Clearly, this property does not hold for ASIC-based NIPSes. Besides, it is remarkable that almost all NIPSes providers ignore this dimension [15, 28, 29, 43]. Furthermore, notice that a prerequisite of flexibility is simplicity as extending a complex system may be hard and error-prone. It is therefore desirable for the hard-to-program elements of our system to be as generic as possible.

## **2** Background

In this Chapter we present a summary of the important concepts that this study is based on. We first present the differences between NIPSes, NIDSes and firewalls. Then, we give an introduction to network intrusion prevention systems and to possible implementations of a NIPS. Subsequently, follows a brief description of the architectural characteristics of network processors. Finally, we briefly discuss load balancing and present the requirements that load balancing for network intrusion prevention must satisfy.

#### 2.1 Differences Between NIPSes, NIDSes and Firewalls

It is important not to confuse network intrusion detection (monitoring) with network intrusion prevention. NIDSes detect attacks and provide information about the attacks so that an administrator can perform an inspection and determine if something is not as it ought to be. Since intrusion detection is a passive technology, it can tolerate detection techniques that are not perfect. The worst case scenario is that you have false positives. Network intrusion detection is a passive detection technology, utilizing broad detection methods sufficient to understand and characterize the traffic that is present on a network. Network intrusion prevention, on the other hand, is quite different. Its job is to proactively prevent attacks from entering your network opposed to just detecting those attacks. A NIDS operates beside the network, offline, and analyzes the traffic as it goes by. On the contrary, a NIPS operates inline, inspecting all packets going inbound or outbound. With intrusion prevention, only precise detection/prevention methods can be used to insure that there are little to no false positives and that legitimate traffic is not mistakenly blocked. It is important to understand that both NIDSes and NIPSes have an important role in a network infrastructure. NIPSes are meant to minimize the risk of known attacks and anomalies that can only cause damage to your network. Where a NIDS gives you insight into your networks patterns and behaviors and helps you to gather forensic data over time.

Finally, firewalls on the other hand, while operating inline, just like a NIPS, they do not inspect the payload of the packets. They merely check the headers of the packets and block traffic not destined to a list of permitted ports. Although this is useful in many cases, firewalls are not capable of blocking the biggest part of the known attacks.

#### 2.2 Introduction to Network Intrusion Prevention Systems

#### 2.2.1 What is an Intrusion?

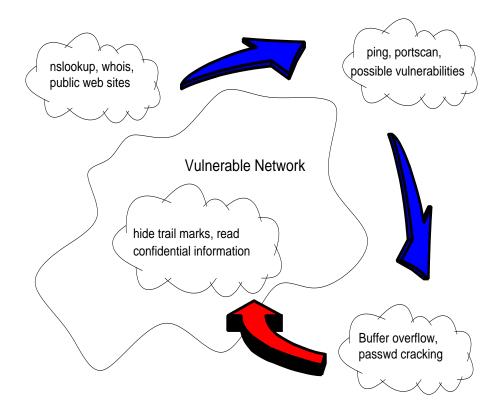

An intrusion is "the act of thrusting in, or of entering into a place or state without invitation, right, or welcome" [45]. In the context of computer systems, intrusion is any unauthorized action in an attempt to compromise a system. Figure 2.1 presents a typical intrusion scenario. For an attacker, the first step is to select the system to attack, which is also known as *outside reconnaisance*. After selecting his victim, the attacker proceeds with *inside reconnaisance*. Particularly, in this step the attacker gathers information about the victim which will help him find possible vulnerabilities or the victim's Achilles' heel. Then, the attacker takes advantage of these vulnerabilities using some exploits and compromises the system. After that, the attacker may have a plethora of options that ranges from stealing confidential information to render unusable the compromised system (e.g erasing hard disks).

#### 2.2.2 What is a Network Intrusion Prevention System?

Network intrusion detection and prevention systems analyze information about the activities performed in a network, looking for evidence of malicious behavior, and block the offending traffic auto-

FIGURE 2.1: A Typical Intrusion Scenario.

matically before it does any damage. The information comes in the form of raw network traffic obtained by monitoring a network link. The collected data are used by NIPSes in two different ways, according to two different approaches: *anomaly detection* and *misuse detection* systems [20].

Anomaly detection systems collect historical data about the activity of a system. Then, given some specifications of the normal behavior of the system, a profile representing the normal operation of the system is constructed. The specifications, for example, may contain the state of the network's traffic load, breakdown, protocol, and typical packet size. During detection, the NIPS tries to identify patterns of activity that deviates from the defined profile (anomalous activity). This approach is based on the notion that attacks tend to look different in some fashion than legitimate computer use. Rather, misuse detection systems take a complementary approach. They are equipped with a number of attack descriptions (or signatures) that are matched against the stream of network data, looking for evidence that a known attack is occurring. Essentially, a misuse detection system looks for a specific attack that has already been documented.

Each of these approaches has its pros and cons. Misuse detection systems can perform detailed analysis of the network data and they usually produce only a few false positives, but they can't detect novel attacks. On the other hand, anomaly detection systems have the advantage of being able to detect previously unknown attacks. This advantage is paid for, in terms of the large number of false positives and the difficulty of training a system with respect to a very dynamic environment.

In this thesis, we concentrate on misuse detection NIPSes. We decided to use misuse detection NIPSes because they are more mature than the anomaly detection NIPSes. In particular, as we have already mentioned, they generate less false positives, and are well understood.

#### 2.2.3 Basic Functions of a Network Intrusion Prevention System

The functionality of a common NIPS can be divided into three different phases: (1) the protocol decoding phase, (2) the detection phase, and (3) the prevention phase. In the first phase, the raw packet stream is seperated into connections representing end-to-end activity of hosts. A connection, in case of IP traffic, can be identified by the source and destination IP addresses, transport protocol and UDP/TCP ports. Then, a number of protocol-based operations are applied to these connections. The protocol handling ranges from network layer to application layer protocols. Some of the operations applied by the protocol-based handling are IP defragmentation, TCP stream reconstruction, identification of the URI in HTTP requests etc. The second phase consists of the actual detection. Here, the packet (or an equivalent higher-level protocol data unit) is checked against a database of detection heuristics representing attack patterns. Then follows the prevention phase. The action of this phase depends on the result of the previous one. If no attack is found, the packets are forwarded to their destination. If malicious activity is observed, then the prevention engine blocks the suspicious traffic by not forwarding the packets belonging to the offending connection(s). Other representative actions of the prevention engine include the rejection of connections by the offending source host for a period of time, or the logging of the offending connections.

#### 2.2.4 Protecting the Network Infrastructure

The reason behind the existence of a NIPS is to protect the network infrastracture. However, as networks evolve, the data volume that a NIPS must process increases. There are two approaches to

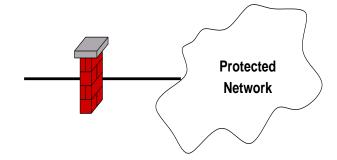

FIGURE 2.2: Single Location Placement.

FIGURE 2.3: Multiple Locations Placement.

analyze this amount of data in real-time: use powerful sensors, <sup>1</sup> or use multiple sensors at the network periphery where the traffic volume is lower [20].

In the first approach (Figure 2.2), the whole traffic is captured at a single location by a muscular NIPS. Obviously, the difficulty with this technique is how to implement such powerful NIPSes. The second approach (Figure 2.3) incorporates the deployment of multiple sensors at the network periphery, close to the hosts which the system must protect. This technique takes advantage of the fact that by moving the inspection to the periphery of the network, a natural partitioning of traffic will occur. Unfortunately, numerous problems stem from this approach. First of all, it is cumbersome to deploy and manage a highly distributed set of sensors. Second, correct sensor positioning can be a challenging task due to the dynamic nature of networks. Last but not least, this approach is unable to provide an integrated, "big picture" view of the network security status. Particularly, attacks that might appear irrelevant in the

<sup>&</sup>lt;sup>1</sup>In this thesis the terms NIPS and sensor are used interchangeably.

context of a single host, might be extremely dangerous when are considered across the network. For all these reasons, we decided to follow the first approach and try to tackle the performance problem that this approach holds.

#### 2.3 A Design Space for Network Intrusion Prevention Systems

Here, we are going to present all the possible network intrusion prevention system architectures and discuss their advantages and disadvantages. To start with, we can categorize the architectures of a NIPS regarding the type of hardware used. In particular four main categories exist: (1) software-based NIPSes implemented on General Purpose Processors (GPPs), (2) software-based NIPSes implemented on network processors, (3) hardware-based NIPSes, frequently implemented using Application Specific Intergarted Circuits (ASICs) or Field Programmable Gate Arrays (FPGAs)<sup>2</sup> and (4) hybrid NIPSes that consist of software- and hardware-based components. Before presenting the characteristics of these four main categories we give a short definition of some keywords that we will use extensively.

#### 2.3.1 Useful Definitions

Because high-performance, flexibility, and scalability are key elements of this thesis, they are defined here.

#### **High-Performance**

A high-performance NIPS is one that is capable of analyzing all the traffic transfered by high-speed network links. To accomplish this goal, a high-performace NIPS must use the available processing capacity as efficiently as possible. It must minimize redundant processing and communication, effectively using the available resources for analyzing the traffic in order to identify intrusion attempts.

#### Flexibility

A NIPS is flexible, if it permits the operator, where the "operator" is someone other than the manufacturer, to put new functionality or upgrade the existing one with minimal effort and cost. For instance, software-based NIPSes are flexible by their nature while hardware-based NIPSes require significant efforts in order to add new functionality.

<sup>&</sup>lt;sup>2</sup>A device that can be reprogrammed at the gate level.

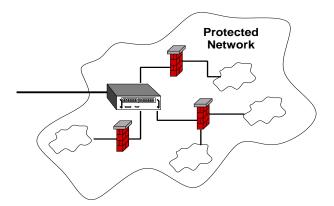

FIGURE 2.4: Possible Implementations of a NIPS.

#### **Scalability**

A NIPS is scalable, if it is capable of scaling up to higher link speeds. If the protection of a faster link or a more fine-grained detection is required, it would be desirable to reuse as much as possible of the existing infrastructure.

#### 2.3.2 Possible Implementations of a NIPS

In Figure 2.4 we present the first three categories regarding performance and flexibility. As we observe, while GPPs provide the most flexible solution, they have relatively poor performance. On the other hand, ASICs have impressive performance characteristics but provide limited flexibility. Somewhere in the middle are the NPs and the FPGAs. An NP is more flexible than an ASIC but is less powerful. Lastly, FPGAs are slower and less flexible compared to NPs. Regarding the hybrid NIPSes, many possible architectures exist and as a result their characteristics vary.

Table 2.1 presents all possible implementations of a NIPS and the characteristics of each implementation. As we observe, there are many possible combinations of the three basic categories. In the next paragraphs we give a short description of each combination and present its advantages and disadvan-

| NIPS Impl. | Flexibility | Performance | Cost per Part |

|------------|-------------|-------------|---------------|

| ASIC       | •           | •           | •             |

| FPGA       | •           | •           | •             |

| NP         | •           | •           | •             |

| GPP        | •           | •           | •             |

| ASIC/GPP   | •           | •           | •             |

| FPGA/GPP   | •           | •           | •             |

| NP/GPP     | •           | •           | •             |

| ASIC/NP    | •           | •           | •             |

| FPGA/NP    | •           | •           | •             |

TABLE 2.1: Characteristis of Possible Implementations of a NIPS.

| ASIC | Application-Specific Integrated Circuit |  |

|------|-----------------------------------------|--|

| FPGA | Field Programmable Gate Array           |  |

| NP   | Network Processor                       |  |

| GPP  | General Purpose Processor               |  |

Lowest

Low

Medium

High

Highest

tages.

**ASIC** As we have mentioned before, an ASIC has the best possible performance but it is not flexible. Moreover, the cost for the manufacturer to produce a unit if it has completed the implementation is small. However, the cost to design hardware is high. On the other hand, the cost for the customer to buy a hardware NIPS is very high and in many cases prohibitive. Thus, the conclusion is that it is expensive both for a manufacturer to design a hardware NIPS and a customer to buy such a NIPS.

**FPGA** An FPGA, has low performance, medium flexibility, and exhibits a high cost both for the manufacturer and the customer. Additionally, the cost to design a NIPS in hardware is high and as a result this solution has not been adopted by any company. Currently, there is research in constructing NIPSes using an FPGA-based approach [27, 24, 9].

**NP** NPs are a hybrid approach between ASICs and GPPs. They provide good performance without sacrifizing flexibility. They are especially tuned for network-based applications, such as a NIPS, and for this reason they are an attractive solution. The cost to buy an NP is relatively high due to the fact that is constructed in low volumes. However, if the NPs are adopted for general network applications their cost will be almost the same as GPPs. Regarding the cost to develop an application on an NP, it is much lower than in the ASIC case but is higher than in the GPP case desribed next. Moreover, note that while NPs exhibit a good performance, this performance is related to operations that are common to network applications such as packet forwarding, packet classification etc. However, NPs are not usualy optimized for performing operations that are present in most NIPSes. In other words, an NP is more effective on performing data-intensive operations. Thus, NPs are commonly used in conjuction with either an ASIC/FPGA or a GPP to implement a fully-functional NIPS.

**GPP** GPPs exhibit the highest possible flexibility and lowest performance. Note that, when we refer that a GPP has low performance, we mean low performance regarding operations that are frequently performed in a network application. In other operations, such as string searching, GPPs have better performance than other solutions like NPs. Unfortunately, a software-based NIPS implemented on a GPP is not capable of monitoring a Gigabit link. However, for lower speed links it is the ideal solution. It is cheap to buy and cheap (and fast) to develop an application on a GPP due to the vast number of existing tools.

**ASIC/GPP-FPGA/GPP** There are NIPSes that try to combine the performance of ASICs with the flexibility of GPPs. These configurations are a good solution that provides high performance and relative good flexibility. However, the presence of the ASIC, provide an upper bound on the flexibility of such a system. In such configurations, probably, the ASIC is responsible for forwarding the packets while the GPPs are executing the detection heuristics. The FPGA/GPP solution is similar with the ASIC/GPP solution but it costs more money and has poorer performance. Thus, it is not adopted by anyone as far as we know.

**NP/GPP** This solution combines the performance and flexibility of NPs with the flexibility of GPPs to build a NIPS with the best tradeoff between performance and flexibility. Unlike the ASIC/GPP case, the presence of the NP does not limit the flexibility of the system while the cost is acceptable, provided

that a small number of NPs is used. In such a configuration, the NP is responsible for performing packet forwarding while the GPPs perform the processor intensive task of packet inspection.