# UNIVERSITY OF CRETE DEPARTMENT OF COMPUTER SCIENCE FACULTY OF SCIENCES AND ENGINEERING

### Memory-Mapped I/O for Fast Storage

by

### **Anastasios Papagiannis**

B.Sc., Computer Science, University of Crete, Greece, 2010M.Sc., Computer Science, University of Crete, Greece, 2013

PhD Dissertation

Presented

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

Heraklion, December 2020

## UNIVERSITY OF CRETE DEPARTMENT OF COMPUTER SCIENCE

#### Memory-Mapped I/O for Fast Storage

PhD Dissertation Presented

by Anastasios Papagiannis

in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

# **APPROVED BY: Author:** Anastasios Papagiannis Supervisor: Angelos Bilas, Professor, University of Crete Committee Member: Manolis Katevenis, Professor, University of Crete Committee Member: Polyvios Pratikakis, Assistant Professor, University of Crete Committee Member: Kostas Magoutis, Associate Professor, University of Crete Committee Member: Dimitrios Nikolopoulos, Professor, Virginia Tech Committee Member: Christos Kozyrakis, Professor, Stanford University Committee Member: George Amvrosiadis, Assistant Research Professor, Carnegie Mellon University Department Chairman: Antonis Argyros, Professor, University of Crete

Heraklion, December 2020

Dedicated to my father Eleftherios, my mother Eleni, and my sister Anna-Maria.

### Acknowledgments

During this amazing trip called PhD, I was fortunate to collaborate with amazing people. First of all, I am grateful to my supervisor Prof. Angelos Bilas. He gave me the space, the time, the resources, and most importantly the guidance to sharpen my technical skills as well as develop my research taste. He was always being there to discuss my ideas and concerns, providing directions and invaluable advises on my research. His mentorship and his interdisciplinary approach were a source of inspiration during my PhD studies.

I am grateful to my thesis committee members Manolis Katevenis, Polyvios Pratikakis, Kostas Magoutis, Dimitrios Nikolopoulos, Christos Kozyrakis, and George Amvrosiadis for their feedback during my defense and for their comments that helped me prepare the final version of this thesis.

Furthermore, I am grateful to my first mentor Dimitrios Nikolopoulos during his years in University of Crete. I did my first steps in research under his supervision during my B.Sc. and M.Sc. studies and I am thankful for the time and energy he put into this work.

I want to thank every single co-author I had all these years: Giorgos Saloustros, Pilar González-Férez and Giorgos Xanthakis. A big thanks also goes to Manolis Marazakis who is always willing to discuss new directions of my research and all the creative brainstorming time we spent together. We worked together, we got rejected together, we resubmitted together. I really enjoyed working with all of you.

After spending a bit more than 10 years in Computer Architecture and VLSI Systems (CARV) lab of the Institute of Computer Science (ICS) in Foundation for Research and Technology-Hellas (FORTH), I feel like I have found a second family there. I met and worked alongside great people in this lab and I want to express my deepest gratitude to Yannis Sfakianakis, Manos Pavlidakis, Stelios Mavridis, Iacovos G. Kolokasis, Nikos Papakonstantinou, Foivos Zakkak, Michalis Vardoulakis, Stella Mikrou, Nikos Batsaras, Thanos

Batzelios, Antonis Chazapis, Christos Kozanitis, and all other past and present members of CARV for preserving the balance between work and real life, making the lab a fun place to be.

I want to express my sincere thanks to Antonis Papaioannou, Vassilis Papakonstantinou, Serafeim Chrisovergis, Ilias Batzelios and all other friends for their support, love, tolerance, and all the great moments we have shared. Additionally I whould like to thank my friends from my hometown Megara, Ilias Moraitis, Akis Stamoulis, Georgios Papadopoulos, Giannis Moustrakas, Giannis Theodosiou, and Nikos Monios for their support all of these years.

I am grateful to my wife Ria Vrouva, for her patience, continuous support, and encouragement during the period of my doctoral thesis' research.

At last but not least, I would like to express my deepest and most sincere gratitude to my parents, Eleftherios and Eleni, and to my little sister Anna Maria, for their love and support throughout all these years. Without your support I would have never been able to complete the dissertation.

I would also like to thank the Institute of Computer Science (ICS) in Foundation for Research and Technology-Hellas (FORTH), which supported me with graduate scholarships throughout my doctoral studies. Funding comes from several European and Greek funded projects that include: CoherentPaaS (FP7-ICT-611068), LeanBigData (FP7-ICT-619606), Vineyard (GA 687628), ExaNeSt (GA 671553), EVOLVE (GA 825061), and Sentitour at Scale (T1EDK-02857). I am pleased to be awarded with the Maria Michael Manasaki legacy's fellowship for the academic year 2018-2019. Finally, I am honored to receive the very competitive Facebook Graduate Fellowship 2019 in the "Compute Storage and Efficiency" research team.

### **Abstract**

Applications typically access storage devices using read/write system calls. Additionally, they use a storage cache to reduce expensive accesses to the devices. Fast storage devices provide high sequential throughput and low access latency. Consequently, the cost of cache lookups and system calls in the I/O path becomes significant at high I/O rates.

In this dissertation, we propose the use of memory-mapped I/O to manage storage caches and remove software overheads in the case of hits. With memory-mapped I/O (i.e. *mmap*), a user can map a file in the process virtual address space and access its data using processor load/store instructions. In this case, the operating system is responsible for moving data between DRAM and the storage devices, creating/destroying memory mappings, and handling page evictions/writebacks. Hits in memory-mapped I/O are handled entirely in hardware through the virtual memory mappings.

First, we design and implement a persistent key-value store that uses memory-mapped I/O to interact with storage devices, and we show the advantages of memory-mapped I/O for hits compared to explicit lookups in the storage cache. Then we show that the Linux memory-mapped I/O path suffers from several issues in the case of data-intensive applications over fast storage devices when the dataset does not fit in memory. These include: (1) the lack of user control for evictions of I/Os, especially in the case of writes, (2) scalability issues with increasing the number of threads, and (3) the high cost of page faults that happen in the common path for misses.

Next, we propose techniques to deal with these shortcomings. We propose a mechanism that handles evictions in memory-mapped I/O based on application needs. To show the applicability of this mechanism, we build an efficient memory-mapped I/O persistent key-value store that uses this mechanism. Subsequently, we remove all centralized contention points and provide scalable performance with increasing I/O concurrency

and number of threads. Finally, we separate protection and common operations in the memory-mapped I/O path. We leverage CPU virtualization extensions to reduce the overhead of page faults and maintain the protection semantics of the OS.

We evaluate the proposed extensions using mainly persistent key-value stores that are a central component for many analytics processing frameworks and data serving systems. We show significant benefits in terms of CPU consumption, performance (throughput and average latency), and predictability (tail latency).

Keywords: Memory-Mapped I/O, Fast Storage, Key-Value Store, mmap

Supervisor: Angelos Bilas

Professor

Computer Science Department

University of Crete

### Περίληψη

Οι εφαρμογές συνήθως προσπελαύνουν τις συσκευές αποθήκευσης χρησιμοποιώντας κλήσεις συστήματος (system calls) για ανάγνωση και εγγραφή. Επιπλέον, χρησιμοποιούν μια κρυφή μνήμη για να μειώσουν τις ακριβές προσπελάσεις στις συσκευές αποθήκευσης. Ωστόσο, συσκευές αποθήκευσης υψηλής ταχύτητας, παρέχουν πλέον πρόσβαση στα δεδομένα σε χαμηλό χρόνο. Κατά συνέπεια, το κόστος των αναζητήσεων στην κρυφή μνήμη (που γίνετε σε λογισμικό) αλλά και των κλήσεων συστήματος γίνεται σημαντικό υπό αυτές τις συνθήκες.

Σε αυτή τη διατριβή, προτείνουμε την διαχείριση της χρυφής μνήμης που χρησιμοποιείται για είσοδο/έξοδο (Ε/Ε) μέσω απειχόνισης των συσχευών στη μνήμη (memory mapped I/O), με στόχο την εξάλειψη του χόστους στις περιπτώσεις ευστοχίας (hits) στην χρυφή μνήμη. Με την απειχόνιση των συσχευών αποθήχευσης στη μνήμη (Linux mmap), ο χρήστης μπορεί να απειχονίσει ένα αρχείο στον χώρο των ειχονιχών διευθύνσεων μιας διεργασίας χαι να αποχτήσει πρόσβαση στα δεδομένα του χρησιμοποιώντας τις εντολές φόρτωσης χαι εγγραφής (load/store) του επεξεργαστή. Σε αυτήν την περίπτωση, το λειτουργιχό σύστημα είναι υπεύθυνο για τη μεταφορά δεδομένων μεταξύ της χυρίας μνήμης χαι των συσχευών αποθήχευσης, τη δημιουργία/χαταστροφή αντιστοιχίσεων ειχονιχής με φυσιχή μνήμη χαι τον χειρισμό της απόρριψης χαι εγγραφής σελίδων της χρυφής μνήμης στις συσχευές αποθήχευσης. Επομένως η διαχείριση των προσβάσεων στην χρυφή μνήμη που είναι εύστοχες (hits) γίνεται εξ ολοχλήρου από το υλιχό μέσω του μηχανισμού για την μετάφραση ειχονιχών διευθύνσεων.

Αρχικά, σχεδιάζουμε και υλοποιούμε ένα σύστημα αποθήκευσης ζευγαριών κλειδιού-τιμής που χρησιμοποιεί την απεικόνιση στη μνήμη για την διαχείριση της κρυφής μνήμης ΕΕ και για να αλληλεπιδρά με τις συσκευές αποθήκευσης. Στην συνέχεια, παρουσιάζουμε τα πλεονεκτήματα του σε σύγκριση με τις αναζητήσεις στην κρυφή μνήμη που είναι υλοποιημένη σε λογισμικό. Δείχνουμε ότι το μονοπάτι στο λειτουργικό σύστημα Linux για την απεικόνιση στη μνήμη των συσκευές αποθήκευσης έχει πολλά προβλήματα στην περίπτωση εφαρμογών με μεγάλες ανάγκες

σε πρόσβαση δεδομένων πάνω από συσκευές γρήγορης αποθήκευσης, όταν το σύνολο των δεδομένων τους δεν χωρά στη κύρια μνήμη. Σε αυτά περιλαμβάνονται: (1) η έλλειψη ελέγχου για την απόρριψη σελίδων, ειδικά κατά την περίπτωση των εγγράφων, (2) η μη επαρκής κλιμάκωση σε συνάρτηση με την αύξηση του αριθμού των νημάτων και (3) το υψηλό κόστος των σφαλμάτων σελίδας που συμβαίνουν κατά την διάρκεια των αστοχιών στην κρυφή μνήμη.

Κατόπιν, προτείνουμε τεχνικές για την αντιμετώπιση αυτών των μειονεκτημάτων. Προτείνουμε έναν μηχανισμό που χειρίζεται την απόρριψη και αντικατάσταση σελίδων μνήμης με βάση τις ανάγκες της εφαρμογής. Για να δείξουμε τη δυνατότητα εφαρμογής του, σχεδιάζουμε και υλοποιούμε ένα σύστημα αποθήκευσης ζευγαριών κλειδιού-τιμής που χρησιμοποιεί αυτόν τον μηχανισμό. Στη συνέχεια, καταργούμε όλα τα κεντρικά σημεία συνωστισμού κατά τον συγχρονισμό στο μονοπάτι της πραγματοποίησης Ε/Ε μέσω απεικόνισης στη μνήμη. Ο σχεδιασμός μας παρέχει κλιμακώσιμη απόδοση με τις συσκευές αποθήκευσης καθώς αυξάνεται ο αριθμός των πυρήνων και νημάτων στους εξυπηρετητές. Τέλος, διαχωρίζουμε την προστασία και τις κοινές λειτουργίες στο μονοπάτι κατά την πρόσβαση σε γρήγορες συσκευές αποθήκευσης μέσω απεικόνισης στη μνήμη. Αξιοποιούμε επεκτάσεις εικονικοποίησης (virtualization extensions) του επεξεργαστή για να μειώσουμε το κόστος των σφάλματων σελίδας (page faults) και να διατηρήσουμε την ισχυρή προστασία μεταξύ χρηστών που παρέχει το λειτουργικό σύστημα.

Αξιολογούμε τις προτεινόμενες επεκτάσεις χρησιμοποιώντας κυρίως συστήματα αποθήκευσης ζευγαριών κλειδιού-τιμής που αποτελούν σημαντικό κομμάτι για πολλά συστήματα επεξεργασίας και εξυπηρέτησης δεδομένων και δείχνουμε σημαντικά οφέλη όσον αφορά την κατανάλωση σε κύκλους του επεξεργαστή, την απόδοση και την προβλεψιμότητα.

Λέξεις κλειδία: Απεικόνιση συσκευών στη μνήμη, Συσκευές αποθήκευσης υψηλής ταχύτητας, Σύστημα αποθήκευσης ζευγαριών κλειδιού-τιμής

> Επόπτης: Άγγελος Μπίλας Καθηγητής Τμήμα Επιστήμης Υπολογιστών Πανεπιστήμιο Κρήτης

### **Bibliographic Notes**

The publications related to this dissertation (ordered by date) are:

- (i) Anastasios Papagiannis, Giorgos Saloustros, Pilar Gonzalez-Ferez, and Angelos Bilas. 2016. *Tucana: design and implementation of a fast and efficient scale-up key-value store*. In Proceedings of the 2016 USENIX Conference on Usenix Annual Technical Conference (USENIX ATC '16). USENIX Association, USA, 537 550.

- (ii) Anastasios Papagiannis, Giorgos Saloustros, Pilar Gonzalez-Ferez, and Angelos Bilas. 2018. *An Efficient Memory-Mapped Key-Value Store for Flash Storage*. In Proceedings of the ACM Symposium on Cloud Computing (**ACM SoCC '18**). Association for Computing Machinery, New York, NY, USA, 490 502.

- (iii) Anastasios Papagiannis, Giorgos Xanthakis, Giorgos Saloustros, Manolis Marazakis, and Angelos Bilas. 2020. *Optimizing Memory-mapped I/O for Fast Storage Devices*. In Proceedings of the 2020 USENIX Conference on Usenix Annual Technical Conference (USENIX ATC '20). USENIX Association, USA

- (iv) Anastasios Papagiannis, Giorgos Saloustros, Giorgos Xanthakis, Giorgos Kalaentzis, Pilar Gonzalez-Ferez, and Angelos Bilas. 2020. Kreon: An Efficient Memory-Mapped Key-Value Store for Flash Storage. ACM Transactions on Storage (ACM TOS) (accepted)

- (v) Anastasios Papagiannis, Manolis Marazakis, and Angelos Bilas. 2020. *Memory-Mapped I/O on Steroids.* (under review)

More specifically, Chapter 2 is based on (i). Chapter 3 based on (ii) & (iv), Chapter 4 based on (iii), and finally Chapter 5 based on (v).

### **Contents**

| Ac | knov    | vledgm   | ients                               | ix   |

|----|---------|----------|-------------------------------------|------|

| Ał | ostrac  | t        |                                     | xi   |

| Ał | ostrac  | t in Gre | eek                                 | xiii |

| Bi | bliog   | raphic   | Notes                               | XV   |

| Ta | ble o   | f Conte  | ents                                | xvii |

| Li | st of I | Figures  |                                     | xxi  |

| Li | st of T | Tables . |                                     | XXV  |

| 1  | Intro   | oductio  | on                                  | 1    |

|    | 1.1     | Levera   | aging Memory-mapped I/O             | 4    |

|    | 1.2     | Contr    | ibutions                            | 4    |

|    | 1.3     | Organ    | nization                            | 6    |

| 2  | An E    | Efficien | t Memory-Mapped I/O Key-Value Store | 7    |

|    | 2.1     | Backg    | ground                              | 9    |

|    | 2.2     | Design   | n                                   | 10   |

|    |         | 2.2.1    | Tree Index                          | 10   |

|    |         | 2.2.2    | Device layout and access            | 12   |

|    |         | 2.2.3    | Copy-on-write persistence           | 14   |

|    |         | 2.2.4    | Concurrency in <i>Tucana</i>        | 16   |

|    |         | 2.2.5    | H- <i>Tucana</i>                    | 17   |

|    | 2.3     | Exper    | imental Analysis                    | 18   |

|    |         | 2.3.1    | Methodology                         | 18   |

|    |         | 2.3.2    | Experimental Results                | 20   |

|    | 2.4     | Sumn     | nary                                | 29   |

| 3  | Opti    | mizing   | g Writes With User Policies         | 31   |

|   | 3.1  | Backg   | round                                        | 33 |

|---|------|---------|----------------------------------------------|----|

|   | 3.2  | Design  | n                                            | 34 |

|   |      | 3.2.1   | Index Organization                           | 35 |

|   |      | 3.2.2   | Memory-Mapped I/O                            | 38 |

|   |      | 3.2.3   | Persistence                                  | 41 |

|   | 3.3  | Exper   | imental Analysis                             | 42 |

|   |      | 3.3.1   | Methodology                                  | 43 |

|   |      | 3.3.2   | Experimental Results                         | 45 |

|   | 3.4  | Sumn    | nary                                         | 54 |

| 4 | Incr | easing  | Page Fault Concurrency                       | 57 |

|   | 4.1  | Motiv   | ation                                        | 59 |

|   | 4.2  | Design  | n                                            | 61 |

|   |      | 4.2.1   | Separate Clean and Dirty Trees in <i>PFD</i> | 61 |

|   |      | 4.2.2   | Full Reverse Mappings in <i>PVE</i>          | 62 |

|   |      | 4.2.3   | Dedicated DRAM Cache                         | 64 |

|   | 4.3  | Imple   | mentation                                    | 66 |

|   | 4.4  | Exper   | imental Analysis                             | 67 |

|   |      | 4.4.1   | Methodology                                  | 67 |

|   |      | 4.4.2   | Experimental Results                         | 70 |

|   | 4.5  | Sumn    | nary                                         | 81 |

| 5 | Red  | ucing P | Protection Costs                             | 83 |

|   | 5.1  | Backg   | round                                        | 86 |

|   |      | 5.1.1   | Linux <i>mmap</i>                            | 86 |

|   |      | 5.1.2   | VT-x CPU Virtualization                      | 87 |

|   | 5.2  | Design  | n                                            | 88 |

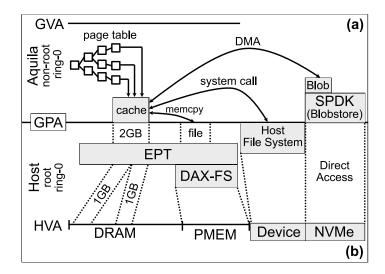

|   |      | 5.2.1   | Virtual to Physical Mappings                 | 89 |

|   |      | 5.2.2   | Device I/O                                   | 92 |

|   |      | 5.2.3   | DRAM Cache                                   | 94 |

|   |      | 5.2.4   | Virtual Memory Lookups and Updates           | 95 |

|   |      | 525     | DRAM Allocation                              | 96 |

|    | 5.3   | Implementation        |                                                                   |  |

|----|-------|-----------------------|-------------------------------------------------------------------|--|

|    | 5.4   | Experimental Analysis |                                                                   |  |

|    |       | 5.4.1                 | Methodology                                                       |  |

|    |       | 5.4.2                 | Experimental Results                                              |  |

|    | 5.5   | Summ                  | nary                                                              |  |

| 6  | Rela  | ted Wo                | rk                                                                |  |

|    | 6.1   | Memo                  | ory-Mapped I/O                                                    |  |

|    |       | 6.1.1                 | Using <i>memory-mapped I/O</i> in data-intensive applications 109 |  |

|    |       | 6.1.2                 | Providing a scalable virtual address space                        |  |

|    |       | 6.1.3                 | Extending the virtual address space over storage                  |  |

|    |       | 6.1.4                 | Dataplane operating systems                                       |  |

|    | 6.2   | Persis                | tent Key-Value Stores                                             |  |

|    |       | 6.2.1                 | LSM-Tree based key-value stores taxonomy and optimizations 114    |  |

|    |       | 6.2.2                 | Other write optimized data structures                             |  |

| 7  | Futu  | ıre Wor               | k                                                                 |  |

|    | 7.1   | Huge                  | Pages in Memory-Mapped I/O                                        |  |

|    | 7.2   | Memo                  | ory-Mapped I/O and Persistent Memory                              |  |

|    | 7.3   | Physic                | cal Memory Extension                                              |  |

|    | 7.4   | Beyon                 | d Persistent Key-Value Stores                                     |  |

|    | 7.5   | Deper                 | ndence on Storage Devices                                         |  |

| 8  | Con   | clusion               | s                                                                 |  |

| Bi | bliog | raphy .               |                                                                   |  |

# **List of Figures**

| 2.1  | The top-level design of <i>Tucana</i> . The left part (a) of the figure shows the tree     |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | index. The right part (b) shows the volume layout                                          | 10 |

| 2.2  | Comparison of $B^{\epsilon}$ -tree (left) and $Tucana$ (right). In $Tucana$ we distinguish |    |

|      | the part of the tree that fits in memory above the dashed line and the rest                |    |

|      | that does not. PH stands for Prefix-Hash                                                   | 11 |

| 2.3  | Table storage in HBase and H- <i>Tucana</i> . CF stands for column family                  | 17 |

| 2.4  | <i>Tucana</i> improvement compared to RocksDB in cycles per operation                      | 21 |

| 2.5  | Performance of <i>Tucana</i> DB and RocksDB in ops/s                                       | 21 |

| 2.6  | Total amount of data read and written during each YCSB workload                            | 23 |

| 2.7  | Number of cycles needed for YCSB workloads                                                 | 23 |

| 2.8  | Scalability of RocksDB and TucanaDB with increasing threads, using the                     |    |

|      | small dataset                                                                              | 24 |

| 2.9  | Improvement in efficiency (cycles/op) achieved by H-Tucana over HBase                      |    |

|      | and Cassandra.                                                                             | 25 |

| 2.10 | Throughput (ops/s) achieved by H- <i>Tucana</i> , HBase and Cassandra                      | 25 |

| 2.11 | Amount of data, in GB, read/written by H- <i>Tucana</i> , HBase, and Cassandra             | 26 |

| 2.12 | Number of cycles needed by H- <i>Tucana</i> for YCSB workloads                             | 28 |

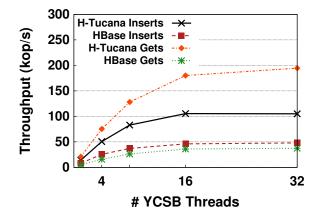

| 2.13 | Scalability of H- <i>Tucana</i> and HBase with the small dataset                           | 28 |

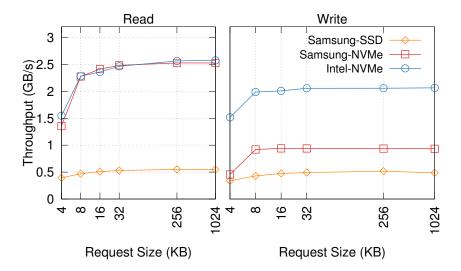

| 3.1  | Throughput vs. block size (using iodepth 32) for Samsung SSD 850 Pro 256 GB,               |    |

| 5.1  | Samsung 950 Pro NVMe 256 GB, and Intel Optane P4800X NVMe 375 GB de-                       |    |

|      | 2                                                                                          |    |

|      | vices, measured with FIO [6].                                                              | 32 |

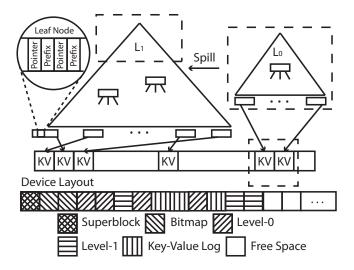

| 3.2 | The main structures of <i>Kreon</i> showing two levels of indexes, the key-value       |    |

|-----|----------------------------------------------------------------------------------------|----|

|     | log, and the device layout. Dashed rectangles include portions of the data             |    |

|     | structures that are kept in memory via <i>kmmap</i>                                    | 37 |

| 3.3 | The main structures of <i>kmmap</i>                                                    | 40 |

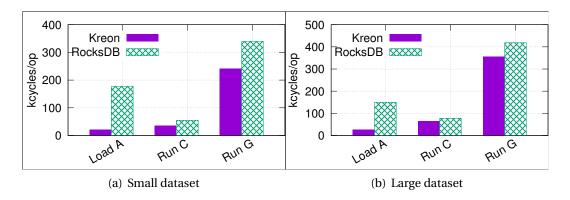

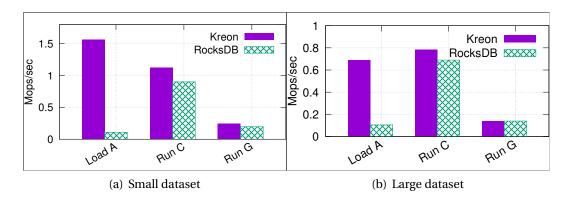

| 3.4 | Efficiency of <i>Kreon</i> and RocksDB in cycles/op                                    | 45 |

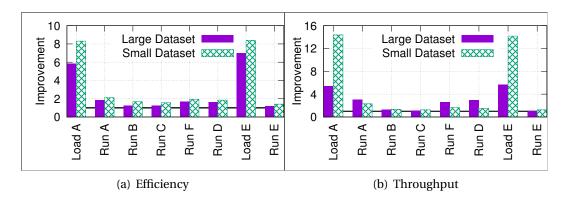

| 3.5 | Efficiency and throughput improvement of <i>Kreon</i> compared to RocksDB for          |    |

|     | all YCSB workloads                                                                     | 46 |

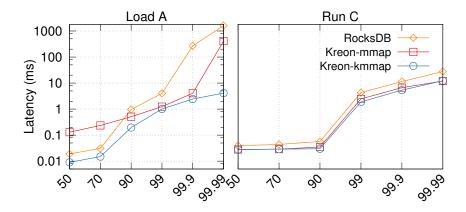

| 3.6 | Tail latency for Load A and Run C for RocksDB, <i>Kreon</i> with vanilla <i>mmap</i> , |    |

|     | and <i>Kreon</i> with <i>kmmap</i>                                                     | 47 |

| 3.7 | Throughput for <i>Kreon</i> and RocksDB in ops/s                                       | 48 |

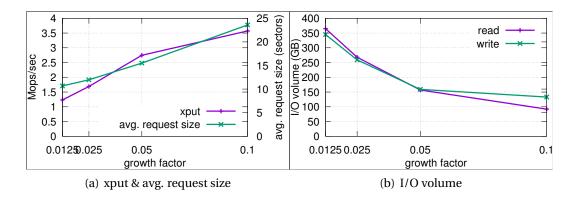

| 3.8 | Results with varying growth factor from 1.25% to 10% (x-axis) using the large          |    |

|     | dataset                                                                                | 53 |

| 3.9 | Results with varying the commit interval (x-axis) for <i>Load A</i> and the large      |    |

|     | dataset                                                                                | 54 |

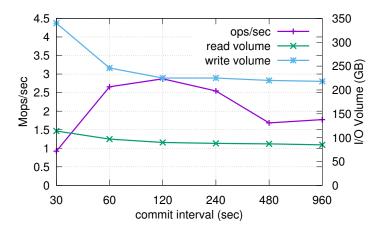

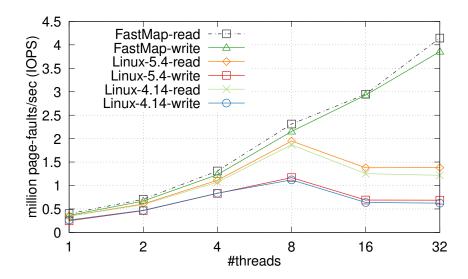

| 4.1 | Scalability of random page faults using two versions of Linux memory-mapped            |    |

|     | $I/O$ path (v4.14 & v5.4) and $FastMap$ , over the $null\_blk$ device                  | 58 |

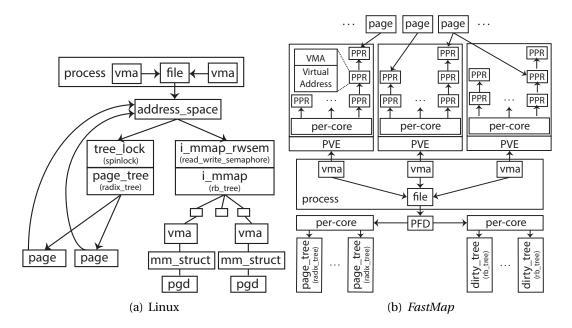

| 4.2 | Linux (left) and FastMap (right) high-level architecture for memory-mapped             |    |

|     | files (acronyms: PFD=Per-File-Data, PVE=Per-Vma-Entry, PPR=Per-Pve-                    |    |

|     | <b>R</b> map)                                                                          | 60 |

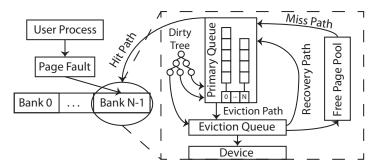

| 4.3 | FastMap I/O path                                                                       | 67 |

| 4.4 | Scalability of random page faults for Linux and FastMap, with up to 80 threads,        |    |

|     | using the <i>null_blk</i> device                                                       | 71 |

| 4.5 | FastMap and Linux mmap breakdown for read and write page faults, with                  |    |

|     | null_blk and 32 cores                                                                  | 72 |

| 4.6 | Performance gains from different optimizations in FastMap, as compared                 |    |

|     | to "vanilla" Linux using <i>null_blk</i> and 32 cores                                  | 73 |

| 4.7 | Execution time for Ligra running BFS with 32 threads and using an Optane               |    |

|     | SSD and a <i>pmem</i> device                                                           | 74 |

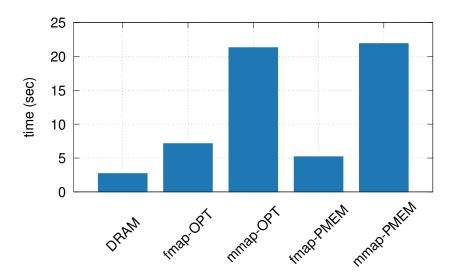

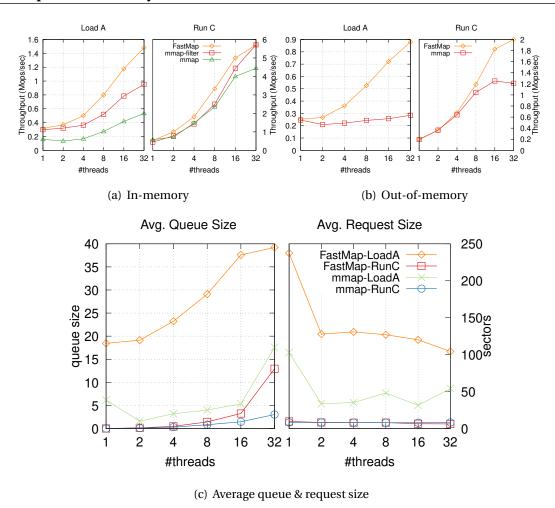

| 4.8  | Kreon scalability with increasing the number of threads ((a) and (b)). Aver-            |

|------|-----------------------------------------------------------------------------------------|

|      | age queue size and average request size for an out-of-memory experiment                 |

|      | (c). In all cases we use the Optane SSD                                                 |

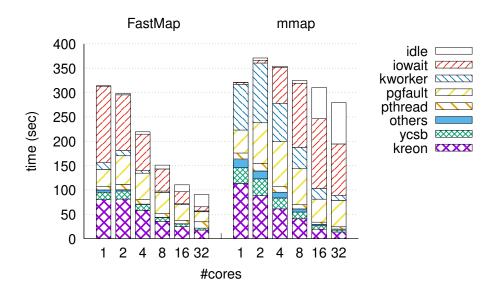

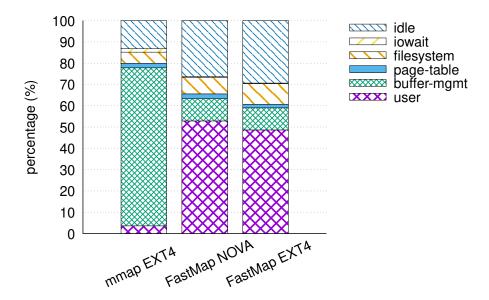

| 4.9  | Kreon breakdown using FastMap and Linux mmap for an out-of-memory                       |

|      | experiment for LoadA YCSB workload, with an increasing number of cores,                 |

|      | an equal number of YCSB threads, and the Optane SSD                                     |

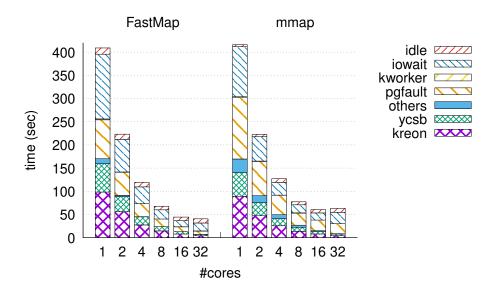

| 4.10 | Kreon breakdown using FastMap and Linux mmap for an out-of-memory                       |

|      | experiment with the RunC YCSB workload, with increasing number of cores                 |

|      | (and equal number of YCSB threads) and the Optane SSD                                   |

| 4.11 | Execution time breakdown for Silo running TPC-C using different file sys-               |

|      | tems and the <i>pmem</i> device                                                         |

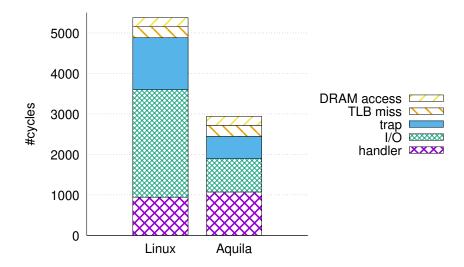

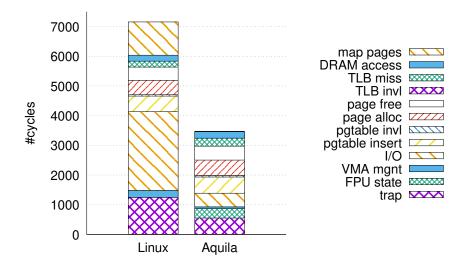

| 5.1  | Page fault latency breakdown for Linux and Aquila, using a pmem device                  |

|      | (backed by DRAM)                                                                        |

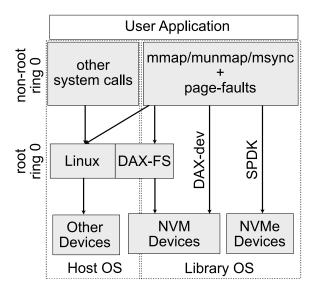

| 5.2  | Aquila high-level design                                                                |

| 5.3  | Page tables, device I/O, DRAM cache, and DRAM allocation in <i>Aquila</i> 90            |

| 5.4  | Aquila execution time breakdown (in cycles) for reads, with a dataset that              |

|      | does not fit in memory and 1 thread                                                     |

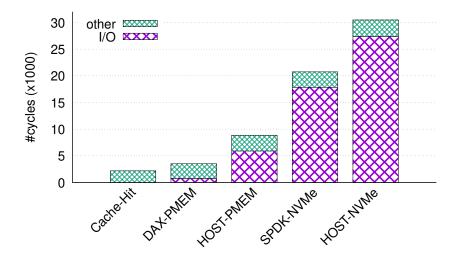

| 5.5  | Aquila execution time breakdown (in cycles) using different approaches for              |

|      | I/O                                                                                     |

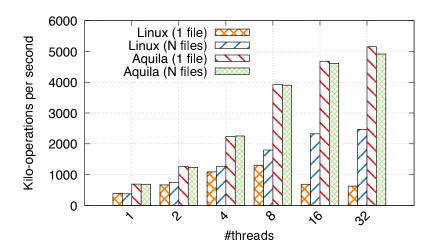

| 5.6  | Linux vs. Aquila throughput (in ops/sec) using random reads for both a                  |

|      | shared and a private file per thread with a dataset that fits in memory $102$           |

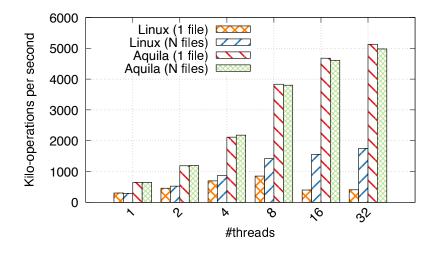

| 5.7  | Linux vs. Aquila throughput (in ops/sec) using random reads for both a                  |

|      | shared and a private file per thread with a dataset that does not fit in memory.102     |

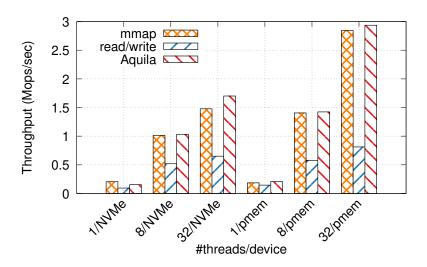

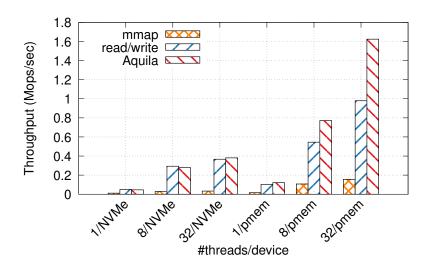

| 5.8  | mmap vs. read/write vs. Aquila for RocksDB and a dataset that fits in memory.104        |

| 5.9  | mmap vs. read/write vs. Aquila for RocksDB and a dataset that does not fit              |

|      | in memory                                                                               |

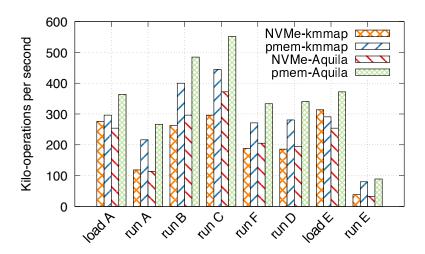

| 5.10 | Kreon <i>kmmap</i> vs. <i>Aquila</i> for a dataset that does not fit in memory for NVMe |

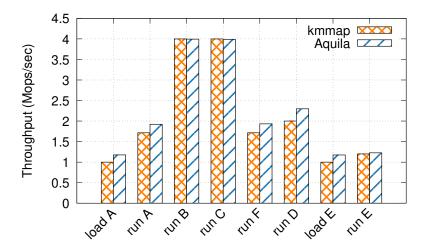

|      | and PMEM using a single thread                                                          |

| 5.11 | Linux <i>kmmap</i> vs. | Aquila for a dataset that fits in memory, a PMEM device |    |

|------|------------------------|---------------------------------------------------------|----|

|      | and 16 threads.        |                                                         | )7 |

### **List of Tables**

| 2.1 | Workloads evaluated with YCSB. All workloads use a query popularity that           |     |  |  |  |  |

|-----|------------------------------------------------------------------------------------|-----|--|--|--|--|

|     | follows a Zipf distribution except for D that follows a latest distribution        | 19  |  |  |  |  |

| 2.2 | Performance for the traffic pattern induced by <i>Tucana</i> and RocksDB as mod-   |     |  |  |  |  |

|     | eled with FIO to isolate device behavior.                                          | 22  |  |  |  |  |

| 3.1 | Workloads evaluated with YCSB. All workloads use a query popularity that           |     |  |  |  |  |

|     | follows a Zipf distribution except for D that follows a latest distribution        | 43  |  |  |  |  |

| 3.2 | Breakdown of cycles per operation for workload Load A (write only). Num-           |     |  |  |  |  |

|     | bers are in kcycles                                                                | 49  |  |  |  |  |

| 3.3 | Breakdown of cycles per operation for workload Run C (read only). Num-             |     |  |  |  |  |

|     | bers are in kcycles                                                                | 50  |  |  |  |  |

| 3.4 | Total I/O volume (in GB) for all benchmarks using the large dataset                | 51  |  |  |  |  |

| 3.5 | I/O randomness using the large dataset and <i>Load A</i> . The higher the value of |     |  |  |  |  |

|     | <i>R</i> , the more random the I/O pattern                                         | 52  |  |  |  |  |

| 4.1 | Standard YCSB Workloads                                                            | 69  |  |  |  |  |

| 4.2 | Throughput in kilo-operations per second and average latency in msec for           |     |  |  |  |  |

|     | TPC-C                                                                              | 79  |  |  |  |  |

| 6.1 | Taxonomy of the main approaches to design key-value stores in three di-            |     |  |  |  |  |

|     | mensions.                                                                          | 115 |  |  |  |  |

### Chapter 1

### Introduction

Flash-based storage devices provide high sequential throughput, high random IOPS, and low access latency. As a result, they introduce new opportunities by narrowing the gap between random and sequential throughput, especially at higher queue depths (number of concurrent I/Os). Despite these technology trends, modern data-intensive applications do not see the full potential of fast storage devices. Consequently, as datasets grow, the I/O path is becoming a significant bottleneck in terms of overhead (CPU cycles) and scalability with the number of cores. Ideally, modern and future servers should consume precious CPU cycles for performing application processing and not I/O to and from devices. Today, we are far from this ideal situation.

Given the performance gap between memory and storage, the I/O path uses a storage cache to leverage locality and reduce the number of accesses to devices. A data access results in a lookup and potential updates in the cache eviction metadata. Even in the case of hits, cache lookups result in high CPU overhead spend for cache management. Authors in [58] claim that about one-third of the total CPU cycles of a database system running OLTP workloads is spent in managing the user-space cache when the dataset fits in memory. In the case of misses, cache replacements move data between memory and the storage devices. Typically these operations use synchronous or asynchronous read and write system calls.

In this dissertation, we propose the use of memory-mapped I/O to manage storage caches and remove software overheads in the case of hits. Hits in memory-mapped I/O

are handled via virtual memory mappings and do not incur any software overhead.

In memory-mapped I/O (i.e. mmap), the application maps a storage device (or a file) in the process virtual address space and the user can access it using processor load and store instructions. In the case of a hit, a valid mapping in the page table already exists. The virtual to physical translation is handled entirely in hardware. In the case of a miss, a page fault happens, which is responsible for adding a new translation in the page table. In this case, the kernel is responsible for reading data from the devices and evicting dirty data when the memory is not enough, when a specific (configurable) amount of time has passed, or when an application explicitly asks for synchronization between memory and the devices. In memory-mapped I/O, the data transfer unit between the devices and memory depends on the hardware-defined page size. Given that the regular page size is 4KB, performing 4KB I/Os in the case of HDDs result in drammatic reduction in the peak device throughput. Fast storage devices address this concern for small I/Os that occur during page faults. However, even in this case, memory-mapped I/O has several shortcomings.

This dissertation addresses limitations of memory-mapped I/O for data-intensive applications over fast storage devices. We show that the use of memory-mapped I/O provides significant improvements compared to read/write system calls and user-space caching.

First, we examine the potential benefit of our approach in persistent key-value stores. Persistent key-value stores are a central component for analytics processing frameworks and data serving systems [41, 5, 30, 49, 54, 36]. We design and implement a persistent key-value store that uses memory-mapped I/O to interact with storage devices. We apply specific optimizations to show the benefits of memory-mapped I/O. Our evaluation shows that hits, which are handled entirely in hardware, provide significant performance improvements compared to a traditional user-space cache and read/write system calls. On the other hand, we also identify several issues of memory-mapped I/O in Linux where the dataset does not fit in memory and, more importantly, in the case of writes, where the user cannot control the timing of I/Os, resulting in high tail latencies.

To overcome the lack of application control in the case where the dataset does not fit in memory, we design and implement a custom memory-mapped I/O path in Linux that handles evictions based on application needs. Our approach uses a priority-based FIFO replacement policy, and during memory pressure, a page with a higher priority is preferred for eviction. To show the applicability of our approach, we use our mechanism in a persistent key-value store designed to take advantage of memory-mapped I/O.

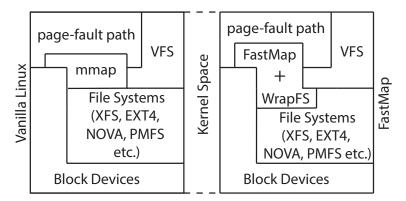

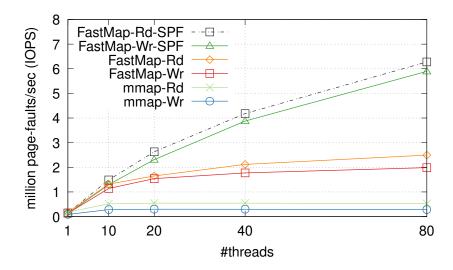

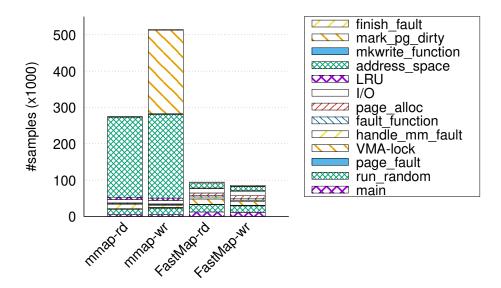

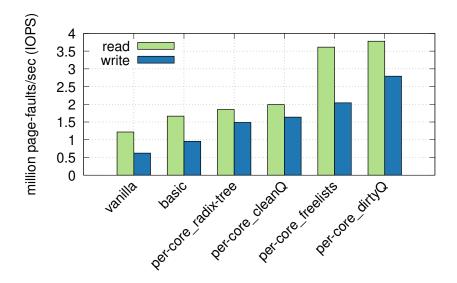

Next, we show that Linux memory-mapped I/O does not scale beyond eight threads. This is a significant limitation for modern multicore servers. To overcome this limitation, we (a) separate clean and dirty-trees to avoid all centralized contention points, (b) use full reverse mappings instead of Linux object-based reverse mappings to reduce CPU processing, and (c) introduce a scalable DRAM cache with per-core data structures to reduce latency variability. Our design achieves both higher scalability and higher I/O concurrency by (1) avoiding all centralized contention points that limit scalability, (2) reducing the amount of CPU processing in the common path, and (3) using dedicated data-structures to minimize interference among processes, thus improving tail latency.

Finally, we tackle miss overheads in memory-mapped I/O managed caches. Memory-mapped I/O introduces page faults instead of system calls in the case of misses. However, page faults incur high overhead. We observe that the main operations of memory-mapped I/O occur at different frequencies: virtual memory management and device access are common path operations. On the other hand, dynamic cache resizing and virtual address range management are uncommon path operations. Based on this observation, we design and implement an efficient library operating system for storage applications that places the application in a virtual machine context. This approach eliminates the cost of protection domain crossings required during page faults. We leverage hardware virtualization extensions to provide full protection semantics while providing the full memory-mapped I/O functionality.

Our approach results in significant performance improvements in terms of performance (throughput and latency), predictability (tail latency), and CPU consumption.

**Thesis statement:** We propose the use of memory-mapped I/O to manage storage caching and remove software overheads in the case of hits. Also, we provide techniques to overcome issues in misses and make memory-mapped I/O practical.

### 1.1 Leveraging Memory-mapped I/O

This dissertation contributes on optimizing the memory-mapped I/O path. To take advantage of our contributions, applications should be re-designed to use memory-mapped I/O instead of a user-space cache and system calls. Our work on persistent key-value stores provides general principles to build an efficient system using memory-mapped I/O. These include: (i) a common data layout for in-memory and persistent representation, (ii) a common allocator for memory and storage, and (iii) the use of Copy-on-Write (CoW) for persistence.

A fundamental design decision on applications that require persistence is the data layout both in memory and device. Today, it is common to have different data representation for memory and devices and translate between them using serialization and deserialization. With memory-mapped I/O an application can map directly parts of the file/device to the user's virtual addresses. This enables data addressing with simple pointer arithmetic operations. Based on this, applications can use the same data layout for both in-memory and persistent representation. Furthermore, applications commonly use different memory and storage allocators due to the different data representation. For the latter, users generally rely on file systems. Our persistent key-value stores, use a common allocator for both memory and persistent data. Both of these techniques reduce by a large factor the number of memory copies, and this results in more CPU cycles and higher memory bandwidth available for user processing. Finally, our work on persistent key-value stores, show that CoW fits well with memory-mapped I/O and it also reduces I/O amplification in the common path. In the next chapters, we provide more details and reasoning about these general principles to design a system that leverages memory-mapped I/O for storage cache management.

#### 1.2 Contributions

The specific contributions of this dissertation are:

1. We apply specific optimizations in a memory-mapped key-value store to show the

1.2. Contributions 5

benefits and deal with the drawbacks of memory-mapped I/O. We show that hits, which are handled entirely in hardware, provide significant performance improvements compared to a traditional user-space cache and read/write system calls. On the other hand, we identify the issues of memory-mapped I/O in Linux, especially when the dataset does not fit in memory.

- 2. We provide a mechanism that handles evictions in memory-mapped I/O based on application needs. We use a priority-based FIFO replacement policy, and during memory pressure, a page with a higher priority is preferred for eviction. We show the applicability of this mechanism on a persistent key-value store that uses memory-mapped I/O to interact with storage devices.

- 3. We show that Linux memory-mapped I/O path fails to scale with increasing the number of concurrent I/Os and application threads. To overcome this issue, we (a) separate clean and dirty-trees to avoid all centralized contention points, (b) use full reverse mappings instead of Linux object-based reverse mappings to reduce CPU processing, and (c) introduce a scalable DRAM cache with per-core data structures to reduce latency variability. Our approach provides scalable performance with large numbers of threads and a large number of concurrent I/Os to the devices, which is essential to achieve peak device throughput.

- 4. We show that a page fault has higher overhead than a system call for the same I/O size. The increased cost can lead to performance degradation in the case of misses. We propose running the application in a privileged domain to reduce page fault cost, similar to where the guest OS runs in virtual machines. We provide full protection semantics by leveraging hardware virtualization extensions. This approach eliminates the cost of protection domain crossings required during page faults. A privileged domain provides direct access to virtual memory hardware, including the page table and TLB that are necessary to handle page faults. Our approach also provides the full memory-mapped I/O functionality.

#### 1.3 Organization

The rest of this dissertation is organized as follows. Chapter 2 presents a *m*emory-mapped I/O use case, in the context of a persistent write-optimized key-value named *Tucana*. Chapter 3 presents a mechanism for user applications to define hot and cold data and affect the eviction policy. We use the *Kreon* key-value store to evaluate our approach. Chapter 4 presents a scalable *m*emory-mapped I/O path inside the Linux kernel named *FastMap*. Chapter 5 presents a design, *Aquila*, to reduce page fault cost in the common path. Chapter 6 reviews related work. Finally, Chapter 7 presents directions for future work and Chapter 8 concludes this thesis.

### Chapter 2

## An Efficient Memory-Mapped I/O Key-Value Store

Our goal in this chapter is to draw a different balance between device and CPU efficiency. We start from a  $B^{\epsilon}$ -tree [22] approach to maintain the desired asymptotic properties for inserts, which is important for write-intensive workloads.  $B^{\epsilon}$ -trees achieve this amortization by buffering writes at each level of the tree. In our case, we assume that the largest part of the tree (but not the data items) fit in memory and we only perform buffering and batching at the lowest part of the tree. Then, we develop a design that manages variable size keys and values, deals with persistence, and stores data directly on raw devices.

Although we still use the buffering technique of  $B^{\epsilon}$ –trees to amortize I/Os, we take a different stance with respect to randomness of I/Os. Unlike LSM-trees [102], we do not make an effort to generate large I/Os. LSM-trees produce large I/Os by maintaining large sorted containers of data items in memory, which can then be read or written as a whole. These large sorted containers are maintained via a compaction technique that relies on sorting and merging smaller pieces. Although this approach has proven extremely effective for HDDs, it results in high CPU overheads and I/O amplification, as we show in our evaluation for LSM-trees.

We design a full featured key-value store, *Tucana*, that achieves lower host CPU overhead per operation than other state-of-the-art systems. *Tucana* provides persistence and recovery from failures, arbitrary dataset sizes, variable key and value sizes, concurrency, multithreading, and versioning. We use copy-on-write (CoW) to achieve recovery without the use of a log, we directly map the storage device to memory to reduce space (memory and device) allocation overhead, and we organize internal and leaf nodes similar to traditional approaches [29] to reduce CPU overhead for lookup operations.

To evaluate our approach, we first compare with RocksDB, a state-of-the-art key-value store. Our results show that Tucana is up to  $9.2\times$  better in terms of cycles/op and between  $1.1\times$  to  $7\times$  in terms of ops/s, across all workloads. This validates our hypothesis that randomness is less important for SSD devices, when there is an adequate degree of concurrency and relatively small I/O requests.

To examine the impact of our approach in the context of real systems, we use Tucana to improve the throughput and efficiency of HBase [5], a popular scale-out NoSQL store. We replace the LSM-based storage engine of HBase with Tucana. Data lookup, insert, delete, scan, and key-range split and merge operations are served from Tucana, while maintaining the HBase mapping of tables to key-value pairs, client API, client-server protocol, and management operations (failure handling and load balancing). The resulting system, H-Tucana, remains compatible with other components of the Hadoop ecosystem. We compare H-Tucana to HBase and Cassandra using YCSB and we find that, compared to HBase, H-Tucana achieves between  $2-8\times$  better CPU cycles/op and  $2-10\times$  higher operation rates across all workloads. Compared to Cassandra, H-Tucana achieves even higher improvements.

Our specific contributions in this work are:

- The design and implementation of a key-value data store that draws a different balance between device behavior and host overheads.

- Practical  $B^{\epsilon}$ -tree extensions that leverage mmap-based allocation, copy-on-write, and append-only logs to reduce allocation overheads.

- An evaluation of existing, state-of-the-art, persistent key-value stores and a comparison with *Tucana*, as well as an improved implementation of HBase.

The rest of this chapter is organized as follows: Section 2.1 provides an overview of persistent data structures. Section 2.2 describes our design. Section 2.3 presents our evalua-

2.1. Background 9

tion methodology and our experimental analysis. Finally, Section 2.4 concludes the chapter.

#### 2.1 Background

In this work, we use as a basis a variant of B-trees, broadly called  $B^{\epsilon}$ -trees [22].  $B^{\epsilon}$ -trees are B-trees with an additional per-node buffer. By using these buffers, they are able to batch insert operations to amortize their cost. In  $B^{\epsilon}$ -trees the total size of each node is B and  $\epsilon$  is a design-time constant between [0,1].  $\epsilon$  is the ratio of B that is used for buffering, whereas the rest of the space in each node  $(1-\epsilon)$  is used for storing pivots.

Buffers contain messages that describe operations that modify the index (insert, update, delete). Each such operation is initially added to the tree's root node buffer. When the root node buffer becomes full, the structure uses the root pivots to propagate a subset of the buffered operations to the buffers of the appropriate nodes at the next level. This procedure is repeated until operations reach a leaf node, where the key-value pair is simply added to the leaf. Leaf nodes are similar to B-Trees and they do not contain an additional buffer, beyond the space required to store the key-value pairs. The cost of an insertion in terms of I/Os is  $O(\frac{\log_B N}{\epsilon B^{1-\epsilon}})$ , where a regular B-Tree has  $O(\log_B N)$  [22, 67].

A get operation is similar to the B-Tree data structure. It traverses the path from the root to the corresponding leaf. This results in similar complexity to B-trees, regarding I/O operations. The main difference is that in a  $B^{\epsilon}$ -tree we also need to search the buffers of the internal nodes along the path. A range scan is similar to a get, except that messages for the entire range of keys must be checked and applied as the appropriate subtree is traversed. Therefore, buffers are frequently modified and searched. For this reason, they are typically implemented with tree indexes rather than sorted containers.

Next, we present the design of *Tucana*, a key-value store that aims to significantly improve the efficiency of data access.

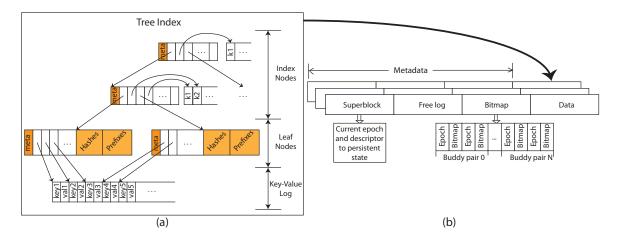

Figure 2.1: The top-level design of *Tucana*. The left part (a) of the figure shows the tree index. The right part (b) shows the volume layout.

#### 2.2 Design

Figure 2.1 shows an overview of *Tucana*. More specifically, Figure 2.1a shows the index organization, which uses  $B^{\epsilon}$ –trees as a starting point (Section 2.2.1). In Figure 2.1b we depict *Tucana*'s approach for allocation and persistence, which we discuss in Sections 2.2.2 and 2.2.3, respectively.

#### 2.2.1 Tree Index

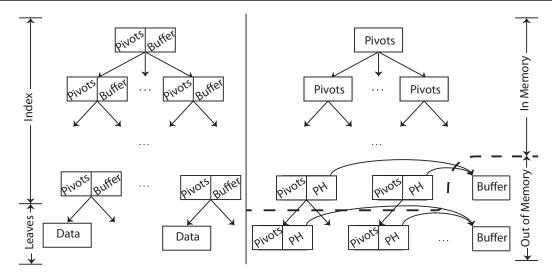

Figure 2.2 shows the differences between Tucana and a B<sup> $\epsilon$ </sup>-tree. On the left side of the figure we show a B<sup> $\epsilon$ </sup>-tree, which we explain in Section 2.1. On the right side of the figure we show Tucana, where we distinguish nodes that fit in main memory from those that do not. To improve host-level efficiency (in terms of cycles/op), Tucana limits buffering and batching to the lowest part of the tree. In many cases today, the largest part of the index structure (but not the actual data) fits in main memory (DRAM today and byte-addressable NVM in the future) and therefore, we do not buffer inserts in intermediate nodes. Tucana design provides desirable asymptotic properties for random inserts, where a single I/O is amortized over multiple insert operations.

Figure 2.1a shows the index organization in *Tucana*. The index consists of internal

Figure 2.2: Comparison of  $B^{\epsilon}$ –tree (left) and *Tucana* (right). In *Tucana* we distinguish the part of the tree that fits in memory above the dashed line and the rest that does not. PH stands for Prefix-Hash.

nodes with pointers to next level nodes and pointers to variable size keys (pivots). We use a separate space per internal node to store the variable size keys themselves. Pointers to keys are sorted based on the key, whereas keys are appended to the buffer. The leaf nodes contain sorted pointers to the key-value pairs. We use a single append-only log to store both the key and values. The design of the log is similar to the internal buffers of  $B^{\epsilon}$ -trees.

Insert operations traverse the index in a top down fashion. At each index node, we perform a binary search over the pivots to find the next level node to visit. When we reach the leaf, we append the key-value pair to the log and we insert the pointer in the leaf, keeping pointers sorted by the corresponding key. Then, we complete the operation. Compared to  $B^{\epsilon}$ —trees we avoid the buffering at intermediate nodes. If a leaf is full, we trigger a split operation prior to insert. Split operations, in index or leaf nodes, produce two new nodes each containing half of the keys and they update the index in a bottom-up fashion. Delete operations place a tombstone for the respective keys, which are removed later. Deletes will eventually cause rebalancing and merging [13].

Point queries traverse the index similar to inserts to locate the appropriate leaf. At the leaf, we perform a binary search to locate the pointer to the key-value pair. Since there are no intermediate buffers as in  $B^{\epsilon}$ -trees, we do not need to perform searches in the

intermediate levels. Finally, range queries locate the starting key similar to point queries and subsequently use the index to iterate over the key range. It is important to notice that in contrast to  $B^{\epsilon}$ –trees we do not need to flush all the intermediate buffers prior to a scan operation.

We note that binary search in the leaf nodes and index nodes is a dominant function used by all operations. To reduce memory footprint for metadata, *Tucana* does not store keys in leaves. This means that keys during binary search need to be retrieved from the device. To avoid this, *Tucana* uses two optimizations, prefixes and hashes.

We store as metadata, a fixed-size prefix for each key in the leaf block. Binary search is performed using these prefixes, except when they result in ambiguity, in which case the entire key is fetched from the log. Prefixes improve performance of inserts, point queries, and range queries. In our tuning of prefixes we find that for different types of keys, prefixes eliminate 65%–75% of I/Os during binary search in leaves.

Additionally, a hash value for each key is stored in the leaf nodes. Hashes help with point queries. For a point query we first do a binary search over prefixes. If this results in a tie, then we linearly examine the corresponding (so not all) hashes. We use Jenkins hash function (one-at-a-time) [69] to produce 4-byte hashes. Then the key is read to ensure there is no collision. In our experiments we find that hashes identify the correct key-value pair in more that the 98% of the cases.

Complexity analysis on the memory footprint and dataset to DRAM ratio are out of the scope of this dissertation and more detail can be found at [105].

### 2.2.2 Device layout and access

Figure 2.1b depicts the data layout in *Tucana*. *Tucana* manages a set of contiguous segments of space to store data. Each segment can be a range of blocks on a physical, logical, virtual block device, or a file. To reduce overhead, segments should be allocated directly on virtual block devices, without the use of a file system. Our measurements show that using XFS as the file system results in a 5-10% reduction in throughput compared to using a virtual block device directly without any file system.

Each segment is composed of a metadata portion and a data portion. The metadata portion contains the superblock, the free log, and the segment allocator metadata (bitmap). The superblock contains a reference to a descriptor of the latest persistent and consistent state for a segment. Modifying the superblock commits the new state for the segment. Each segment has a single allocator common for all databases (key ranges) in a segment. The data portion contains multiple databases. Each database is contained within a single segment and uses its own separate indexing structure.

The allocator keeps persistent state about allocated blocks of a configurable size, typically set to 4 KB, and multiples of it. For this purpose, it uses bitmaps because in key-value stores allocations can be in the order of KBs, as opposed to filesystems that typically do larger allocations. Moreover, allocator bitmaps are accessed directly via an offset and at low overhead, while for searches there are efficient bit parallel techniques [23]. It also maintains state about free operations and performs them lazily in a log structure named *Free log*.

In all persistent key-value stores, including *Tucana*, the index includes pointers to data items in the storage address space. During system operation, part of the index and data are cached in memory. When traversing the index to serve an operation, there is a need to translate storage pointers to pointers in memory. This leads to frequent cache lookups that cannot be avoided easily. Essentially, the cache serves as a mechanism to translate pointers from the storage to the memory address space. Previous work [58] indicates that when all data and metadata fit in memory, managing this cache requires about one-third of the index CPU cycles.

Most key-value stores today follow this caching approach [54, 49, 5, 82, 101]. This allows the key-value store to also control the size and timing of I/O operations between the memory cache and the storage devices, as well as the cache policy.

Instead, *Tucana* uses an alternative approach based on mmap. mmap uses a single address space for both memory and storage and virtual memory protection to determine the location (memory or storage) of an item. This eliminates the need for pointer translation at the expense of page faults. We note that pointer translation occurs during index operations regardless of whether items are in memory or not, whereas page faults occur

only when items are not in memory. The use of mmap also allows *Tucana* to use a single allocator for memory and device space management. Additionally, mmap eliminates data copies between kernel and user space.

The use of mmap has three drawbacks. First, each write operation of variable size is converted to a read-modify-write operation, increasing the amount of I/O. In our design, due to the copy-on-write persistence (see Section 2.2.3), all writes modify eventually the full page and there can be no reads to unwritten parts of a page. Therefore, we use a simple filter block device in the kernel, which filters read-before-write operations and merely returns a page of zeros. Write and read-after-write operations are not filtered and are forwarded to the actual device. The filter module uses a simple, in-memory bitmap and is initialized and updated by *Tucana* via a set of ioctls. The size of the in-memory bitmap is proportional to the block device size (for 1 TB of storage we need 32 MB of memory).

Second, mmap results in the loss of control over the size and timing of I/O operations. mmap generates page-sized I/Os (4 KB). To mitigate the impact of small I/Os we use madvise to instruct mmap to generate larger I/Os. To control their timing we use msync for specific items and memory ranges during commit operation.

Third, mmap introduces page faults for fetching data. The number of page faults depends on mmap kernel page eviction policy. *Tucana* would benefit from custom eviction policies that keep the index and the tail of the append log in memory. In this work, we do not make an attempt to control these policies. However, future work should examine this issue in more detail.

### 2.2.3 Copy-on-write persistence

*Tucana* uses a Copy-on-Write (CoW) approach for persistence instead of a Write-Ahead-Log (WAL). WAL produces sequential write I/Os at the expense of doubling the amount of writes (in the log and later in place). CoW performs only the necessary writes, however, it generates a more random I/O pattern. Therefore, although a WAL is more appropriate for HDDs, CoW has more potential for fast devices. The use of CoW is also motivated by three additional reasons; (a) It is amenable to supporting versioning. (b) It allows instantaneous

recovery, without the need to redo or undo a log. (c) It helps increase concurrency by avoiding lock synchronization for different versions of each data item [93], as we discuss in the next subsection.

The state of a segment consists of the allocator, tree metadata, and buffers. CoW is used to maintain the consistency of both allocator and tree metadata. The bitmap in each segment is organized in *buddy pairs*, as shown in Figure 2.1b. Each *buddy pair* consists of two 4 KB blocks that contain information about allocated space. Each buddy is marked with a global per segment increasing counter named *epoch*. The epoch field is incremented after a successful commit operation and denotes the latest epoch in which the buddy was modified. At any given point only one buddy of the pair is active for write operations, whereas the other buddy is immutable for recovery. Commits persist and update modified buddy pairs.

The allocator defers free operations with the use of the free log [20]. Directly applying a free operation that could be rolled back in the presence of failures is more complicated as it can corrupt persistent state. We log free operations using their epoch id, and we perform them later after their epoch becomes persistent.

To maintain the consistency of the tree structure during updates, each internal index and leaf node uses epochs to distinguish its latest persistent state. During an update, the node's epoch indicates whether a node is immutable, in which case a CoW operation takes place. After a CoW operation for inserting a key, the parent of the node is updated with the new node location in a bottom-up fashion. The resulting node belongs to epoch+1 and will be persisted during the next commit. Subsequent updates to the same node before the next commit are batched by applying them in place. Since we store keys and values in buffers in an append-only fashion, we need to only perform CoW on the header of each internal node.

*Tucana*'s persistence relies on the atomic transition between consistent states for each segment. Metadata and data in *Tucana* are written asynchronously to the devices. However, transitions from state to state occur atomically via synchronous updates to the segment's superblock with msync (commits). Each commit creates a new persistent state for the segment, identified by a unique epoch id. The epoch of the latest persistent state of a

segment is stored in a descriptor to which the superblock keeps a reference.

Commits can take place in parallel with read and write operations. To achieve this, a commit is performed in two steps: (1) Initially, it marks the current state as persistent by increasing the epoch of the system. This state includes the bitmap and the tree indexes for this segment. (2) It flushes the state of the segment to the device. In case of a failure during a commit, the segment simply rolls back to the latest persistent state by ignoring any writes that have reached the device but were not committed via the metadata epoch states.

During a commit operation, the bitmap cannot be modified by new allocations (a subset of the write operations) because this may change the state on the device (mmap may propagate any write from memory to the device asynchronously). In case the current commit fails, then both *buddy pairs* will be inconsistent. To avoid this, allocations during a commit are buffered in a temporary location in memory and are applied at the end of the commit.

### 2.2.4 Concurrency in *Tucana*

Concurrency in key-value stores is important for scaling up as server density increases in terms of CPU, storage, and network throughput. Key-value stores typically operate under high degrees of concurrency, due to the large numbers of client requests.

Similar to most key-value stores, *Tucana* partitions datasets in multiple databases (key ranges). Requests in different ranges can be served without any synchronization. The only exception in *Tucana* is insert operations in different regions that are stored in the same segment. In this case the existence of a single segment allocator requires synchronization across ranges during allocation operations. To reduce the impact of such synchronization, the allocator operates in a batched mode, where a request reserves more space than required for the current operation. Subsequent inserts to the same database do not need to request space from the allocator.

Within each range, *Tucana* allows any number of concurrent reads and a single write without synchronization. To achieve this, *Tucana* uses the versions of the segment cre-

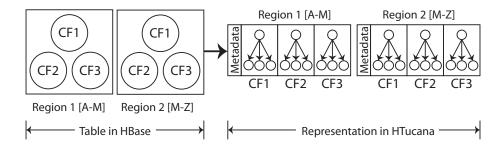

Figure 2.3: Table storage in HBase and H-Tucana. CF stands for column family.

ated through commits, similar to read-copy-update synchronization [95]. In particular, we serve read operations from the latest persistent version of the segment, which is immutable. Writes on the other hand are served from the modified root which contains all modifications.

Updates applied by an application are visible to readers after a commit. *Tucana*'s API offers additional fence operations to allow higher layers to control when updates become visible.

Finally, in the current state of the prototype, *Tucana* does not allow multiple concurrent writes in the same range. Although there are possible optimizations, especially to allow non-conflicting writes via copy-on-write, or dynamic partitioning of the key-space, we leave these for future work.

#### 2.2.5 H-*Tucana*

HBase [5] is a scale-out columnar store which supports a small and volatile schema. HBase offers a table abstraction over the data, where each table keeps a set of key-value pairs. Each table is further decomposed into regions, where each region stores a contiguous segment of the key space. Each region is physically organized as a set of files per column, as shown in Figure 2.3.

At its core HBase uses an LSM-tree to store data [102]. We use *Tucana* to replace this storage engine, while maintaining the HBase metadata architecture, node fault tolerance, data distribution and load balancing mechanisms. The resulting system, H-*Tucana*, maps HBase regions to segments (Figure 2.3), while each column maps to a separate tree in the

segment. In our work, and to eliminate the need for using HDFS under HBase, we modify HBase so that a new node handles a segment after a failure. We assume that segments are allocated over a reliable shared block device, such as a storage area network (SAN) or virtual SAN [97, 132] and are visible to all nodes in the system. In this model, the only function that HDFS offers is space allocation. *Tucana* is designed to manage space directly on top of raw devices, therefore, it does not require a file system. H-*Tucana* assumes the responsibility of elastic data indexing, while the shared storage system provides a reliable (replicated) block-based storage pool.

### 2.3 Experimental Analysis

In this section we evaluate Tucana against RocksDB [49] and H-*Tucana* to HBase [5] and Cassandra [82]. Our goal is to examine the following aspects of *Tucana*:

- 1. How does *Tucana* compares to RocksDB in terms of efficiency and absolute performance and where does these improvements come from?

- 2. What is the impact of *Tucana* in NoSQL stores?

*Tucana* and RocksDB support similar features including persistence and recovery, arbitrary size keys and values and versions. In the same category there are other popular key-value stores, such as LevelDB, KyotoDB, BerkeleyDB, and PerconaFT (based on Fractal Index Trees). In our experiments we find that RocksDB outperforms all of them [52, 55] and therefore, we present only the comparison between *Tucana* and RocksDB. HBase and Cassandra are NoSQL databases that are widely used as a back-end for high throughput systems. HBase and Cassandra use LSM-trees [102].

### 2.3.1 Methodology

Our experimental platform consists of two systems (client and server) each with two quadcore Intel(R) Xeon(R) E5520 CPUs running at 2.7 GHz. The server is equipped with 48 GB DDR-III DRAM, and the client with 12 GB. Both nodes are connected with a 10 Gbits/s

|   | Workload                         |

|---|----------------------------------|

| A | 50% reads, 50% updates           |

| В | 95% reads, 5% updates            |

| C | 100% reads                       |

| D | 95% reads, 5% inserts            |

| E | 95% scans, 5% inserts            |

| F | 50% reads, 50% read-modify-write |

Table 2.1: Workloads evaluated with YCSB. All workloads use a query popularity that follows a Zipf distribution except for D that follows a latest distribution.

network link. As storage devices, the server uses four Intel X25-E SSDs (32 GB) and we make a RAID-0 with them using the standard *md* Linux driver. *Tucana* is implemented in C and can be accessed from applications as a shared library. H-*Tucana* is cross-linked between the Java code of HBase and the C code of *Tucana*.

We use the open-source Yahoo Cloud Serving Benchmark (YCSB) [37] to generate synthetic workloads. The default YCSB implementation executes gets as range queries and therefore, exercises only scan operations. For this reason, we modify YCSB to use point queries for get operations. Range queries are still exercised in Workload E, which uses scan operations.

When comparing RocksDB and *Tucana* we use a low-overhead C++ version of YCSB-C [37, 114]. The original Java YCSB benchmark requires JNI to run with RocksDB and *Tucana*, which are written in C++ and C respectively, incurring high overheads.

In all cases, we run the standard workloads proposed by YCSB with the default values. Table 2.1 summarizes these workloads. We run the following sequence proposed by the YCSB author: Load the database using workload A's configuration file, run workloads A, B, C, F, and D in a row, delete the whole database, reload the database with workload E's configuration file, and run workload E.

When comparing *Tucana* to RocksDB we use 256 YCSB threads and 64 databases (unless noted otherwise) and we choose the appropriate database by hashing the keys. When comparing H-*Tucana* to HBase and Cassandra we use 128 YCSB threads and 8 regions for HBase and H-*Tucana*. Cassandra is hash-based and does not support the notion of region, so we use a single table.

We use a small dataset that fits in memory and a large dataset that does not. The small dataset is composed of 60M or 100M records when using *Tucana* and H-*Tucana*, respectively. The large dataset has 300M or 500M records when using *Tucana* and H-*Tucana*, respectively.

In all the cases, the load phase creates the whole dataset and the run phases issue 5 million operations, bounded also by time (one hour max). With *Tucana*, even in the case of the large dataset the index nodes fit in memory as per our assumptions.

We measure efficiency as cycles/op, which shows the cycles needed to complete an operation on average. We calculate efficiency as:

$$cycles/op = \frac{\frac{CPU\_utilization}{100} \times \frac{cycles}{s} \times cores}{\frac{average\_ops}{s}},$$

(2.1)

where *CPU\_utilization* is the global average of CPU utilization among all processors, excluding idle and I/O time, as given by mpstat. As cycles/s we use the per-core clock frequency. *average\_ops/s* is the throughput reported by YCSB and *cores* is the number of cores including hyperthreads.

### 2.3.2 Experimental Results

### Tucana compared to RocksDB

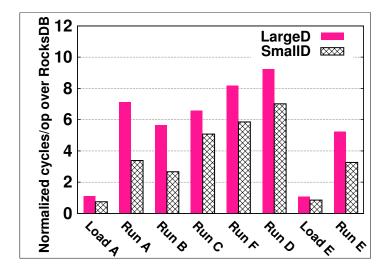

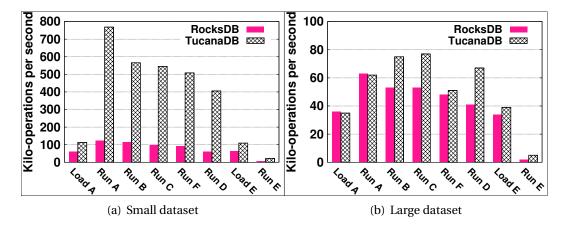

Figure 2.4 shows the improvement over RocksDB in efficiency. In workloads Load A and Load E that are insert intensive, Tucana is similar to RocksDB for both small and large datasets, since both use write-optimized data structures. In all other workloads Tucana outperforms RocksDB by  $0.75\times$  to  $7.01\times$  for the small dataset and by  $1.07\times$  to  $9.24\times$  for the large dataset.

We note that increased efficiency can also be achieved with low absolute performance, which is not desirable. Figure 2.5 shows ops/s for the two systems. We see that for the small dataset *Tucana* outperforms RocksDB by  $2\times$  to  $7\times$  and by  $4.47\times$  on average in absolute performance (throughput) as well. For the large dataset, where both systems are limited by device performance, *Tucana* outperforms RocksDB by  $1.1\times$  to  $2.1\times$  and by  $1.35\times$  on

Figure 2.4: *Tucana* improvement compared to RocksDB in cycles per operation.

Figure 2.5: Performance of *Tucana*DB and RocksDB in ops/s.

average. Average SSD utilization for all workloads is 93% for *Tucana* and 78% for RocksDB. *Tucana* has on average smaller request size, 86 KB compared to 415 KB for RocksDB. As next generation SSDs close the gap between sequential and random performance, we expect even larger performance improvements over RocksDB and similar stores.

Next, we examine I/O amplification and randomness. We run an insert-only benchmark (random distribution) using a *single* database of size 36.3 GB. RocksDB writes 435 GB while *Tucana* writes 123 GB, thus  $3.5 \times$  less than RocksDB. Due to compaction operations, RocksDB also reads  $2.3 \times$  the amount of data read by *Tucana*, 69 GB vs. 29 GB. Table 2.2

|                |            |          | SSD (2010) | SSD (2015) |

|----------------|------------|----------|------------|------------|

| <b>Inserts</b> | Write (GB) | $rq\_sz$ | time (s)   | time (s)   |

| Tucana         | 123        | 18K      | 133        | 31         |

| RocksDB        | 435        | 884K     | 623        | 100        |

| Speedup        |            |          | 4.68       | 3.22       |

|                |           |      | SSD (2010) | SSD (2015) |

|----------------|-----------|------|------------|------------|

| <b>Inserts</b> | Read (GB) | rqsz | time (s)   | time (s)   |

| Tucana         | 26        | 4K   | 256        | 140        |

| RocksDB        | 29        | 6K   | 229        | 171        |

| Speedup        |           |      | 0.89       | 1.22       |

Table 2.2: Performance for the traffic pattern induced by *Tucana* and RocksDB as modeled with FIO to isolate device behavior.

shows the performance difference between these two patterns on two different SSD generations, using FIO (Flexible I/O) [6] to generate each pattern. For inserts, *Tucana*'s I/O pattern is 4.68× faster on the older SSD (2010) and 3.22× faster on the newer SSD (2015), compared to RocksDB's I/O pattern and volume. For gets, the difference in volume size and request size is lower and performance differences are smaller. The I/O pattern of RocksDB is better by 11% for the older SSD, whereas the I/O pattern of *Tucana* is better by 22% for the newer SSD.

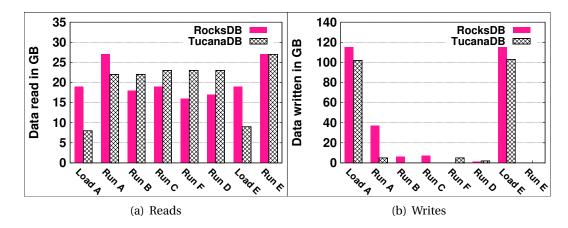

Figure 2.6 shows read and write amplification using 64 databases. Although *Tucana* incurs less I/O on average for both read and write, the difference with RocksDB in this case is smaller. On average RocksDB writes 3.33× and reads 1.25× more data.

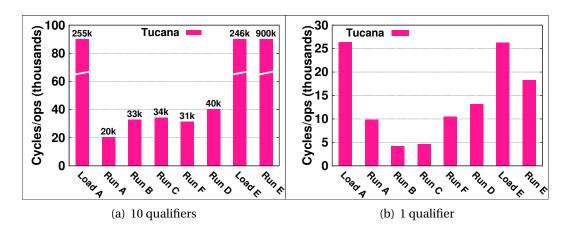

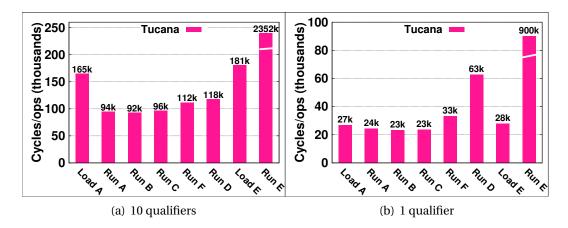

Next, we examine the absolute number of cycles/op for each workload (Figure 2.7(a)). Each operation is a composite operation over a row with ten qualifiers and therefore a get operation performs ten lookup operations. For this reason, we also present numbers for the same workloads, with one qualifier per row in Figure 2.7(b). In addition, in the case of Workload E the default average length of a range query is fifty. In Figure 2.7(b) we change the scan length to five. On average, an insert operation takes about 26K cycles (Load A & Load E), a point query (get) 4K cycles (Run C) and a range query (scan), including initialization and five rows of one qualifier about 18K cycles (Run E). The other workloads are mixes of these operations. If we examine a breakdown of cycles, we see that on average

Figure 2.6: Total amount of data read and written during each YCSB workload.

Figure 2.7: Number of cycles needed for YCSB workloads.

15% is used by YCSB, 43% by *Tucana*, 38% by the OS kernel, and 4% by other server processes. More specifically, for an insert-only benchmark 35% is used by *Tucana* and 60% by OS kernel. On the other hand for a get-only benchmark 66% is used by *Tucana* and 26% by kernel. System time is due to mmap that handles page faults, mappings, and the swapper that evicts dirty pages to devices.

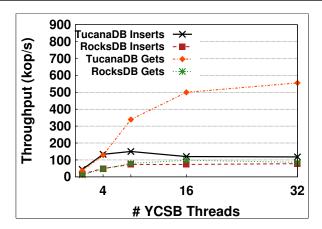

Finally, Figure 2.8 shows scalability of *Tucana* and RocksDB with the number of server cores. We use the small dataset that fits in memory, partitioned in 64 databases, and we increase the load by increasing the number of YCSB threads that issue requests. For gets, *Tucana* is able to scale and it saturates the full server at 16 YCSB threads. *Tucana* pro-

Figure 2.8: Scalability of RocksDB and *Tucana*DB with increasing threads, using the small dataset.

vides lock-less gets and therefore uses all available cores. After warm-up, where data is brought in memory, system utilization is about 100% at 16 YCSB threads. On the other hand, RocksDB, even after warm up, still has about 25% idle CPU time at 8 or more YCSB threads, indicating synchronization bottlenecks.

For inserts, *Tucana* saturates the server at about 8 YCSB threads, where CPU is utilized at 90-95%. RocksDB scales up to 8 threads also, where it saturates the server. Due to its more random I/O pattern, *Tucana* incurs higher device utilization, about 50% vs. 20% for RocksDB. Generally, scaling for puts in both systems is related to the number of databases. In this work, we do not explore this dimension further.

#### Impact on NoSQL store performance

In this section, we analyze the efficiency and performance of H-*Tucana*, compared to HBase [5] and Cassandra [82].

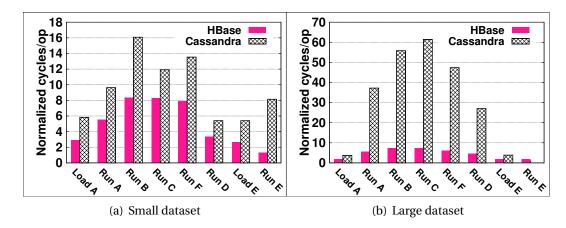

Figure 2.9 depicts the speedup in efficiency (cycles/op) achieved by H-Tucana over HBase and Cassandra. We see that H-Tucana significantly outperforms both HBase and Cassandra. Compared to HBase, H-Tucana uses fewer cycles/op by up to  $2.9\times$ ,  $8.4\times$ , and  $5.6\times$  for write-intensive, read intensive, and mixed workloads. Compared to Cassandra, the improvement depends on the size of the dataset. With the small dataset H-Tucana outperforms Cassandra by up to  $5.8\times$ ,  $16.1\times$ , and  $13.5\times$  for the write, read intensive, and

Figure 2.9: Improvement in efficiency (cycles/op) achieved by H-*Tucana* over HBase and Cassandra.

Figure 2.10: Throughput (ops/s) achieved by H-Tucana, HBase and Cassandra.

mix workloads, respectively. With the large dataset, H-Tucana improves cycles/op over Cassandra by up 3.9×, 61.4×, and 37.2× write, read-intensive and mixed workloads respectively.

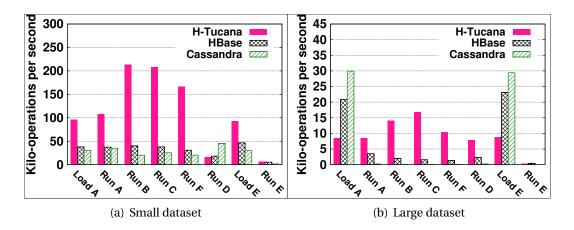

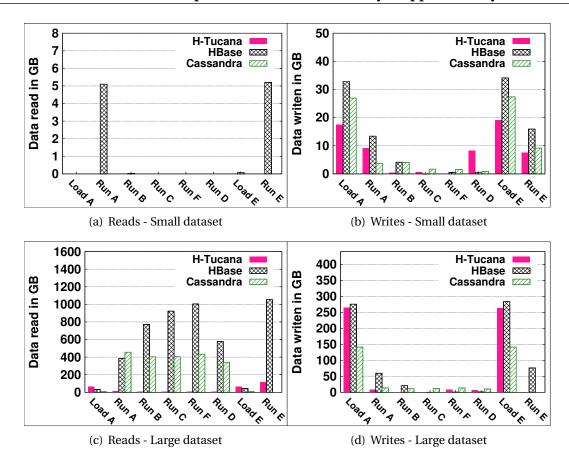

Next, we examine throughput in terms of ops/s. Figure 2.10 shows performance in kilo-operations per second whereas Figure 2.11 depicts the amount of data read and written by each workload.

For the small dataset, H-*Tucana* has up to 5.4× higher throughput compared to HBase, and up to 10.7× compared to Cassandra. In addition, H-*Tucana* does not perform any reads during the run phases. Cassandra does not read any data either, whereas HBase

Figure 2.11: Amount of data, in GB, read/written by H-Tucana, HBase, and Cassandra.

reads 5.1 GB and 5.2 GB when running workloads A and E, respectively. The amount of data written to the device is significantly reduced by H-*Tucana* by 38% and 17% compared to HBase and Cassandra.