# CMOS COMPATIBLE NON-VOLATILE MEMORY DEVICES BASED ON III-N QUANTUM DOTS

Master Thesis

Microelectronics & Optoelectronics Graduate Program

Elena Papadomanolaki

Supervising Professor: Eleftherios Iliopoulos

## **CONTENTS**

| Ac. | know   | ledgem        | ents                                                      | vii  |

|-----|--------|---------------|-----------------------------------------------------------|------|

| Ab  | stract |               |                                                           | ix   |

| Lis | t of F | igures        |                                                           | xi   |

| Lis | t of T | ables         |                                                           | xvii |

|     |        |               |                                                           |      |

| CH  | IAPT   | <b>ER 1</b> : | INTRODUCTION TO NON-VOLATILE MEMORIES                     | 1    |

|     | 1.1    | The F         | loating Gate: Structure and Basic Operation               | 3    |

|     |        | 1.1.1         | Structure of a FG-MOSFET                                  | 3    |

|     |        | 1.1.2         | Operation Principles with Basic Equations                 | 3    |

|     | 1.2    | Memo          | ory Characteristics: Concepts and Definitions             | 7    |

|     |        | 1.2.1         | Memory Window                                             | 7    |

|     |        | 1.2.2         | Retention                                                 | 9    |

|     |        | 1.2.3         | Endurance                                                 | 11   |

|     |        | 1.2.4         | Other Performance Aspects of NVM                          | 11   |

|     | Refe   | erences       |                                                           | 13   |

| CF  | ГАРТ   | 'ER 2. '      | THEORETICAL BACKGROUND                                    | 15   |

| -   | 2.1    |               | 4OS Capacitor and the MOSFET                              | 17   |

|     |        | 2.1.1         | Electronics of the Metal-Oxide-Semiconductor System       | 17   |

|     |        | 2.1.2         | MOS Capacitance                                           | 20   |

|     |        | 2.1.3         | The MOS Field Effect Transistor and the Threshold Voltage | 23   |

|     | 2.2    | Physic        | cs of the FG-MOSFET                                       | 25   |

|     |        | •             | Charge Storage                                            | 25   |

|     |        |               | FG-MOS Capacitance                                        | 28   |

|     |        | 2.2.3         | Limits of the FG-MOSFET                                   | 31   |

|    | 2.3  | Nano          | particle Memory Devices                                | 33         |

|----|------|---------------|--------------------------------------------------------|------------|

|    |      | 2.3.1         | Structure and Operation                                | 33         |

|    |      | 2.3.2         | Memory Window and Capacitance                          | 34         |

|    |      | 2.3.3         | Nanoparticle Memory Cells versus Conventional Floating | •          |

|    |      |               | Devices                                                | 38         |

|    | 2.4  | _             | tum Dots                                               | 40         |

|    |      | 2.4.1         | Confinement: Properties of Quantum Dots                | 40         |

|    |      |               | Materials for Quantum Dots                             | 43         |

|    | Refe | erences       |                                                        | 46         |

|    |      |               |                                                        |            |

|    |      |               |                                                        |            |

| CI | HAPT | <b>ER 3</b> : | DEVICES AND CHARACTERIZATION                           | 49         |

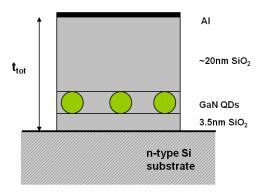

|    | 3.1  | Grow          | th of GaN QDs MOS Devices                              | 50         |

|    |      | 3.1.1         | Fabrication of the Devices                             | 50         |

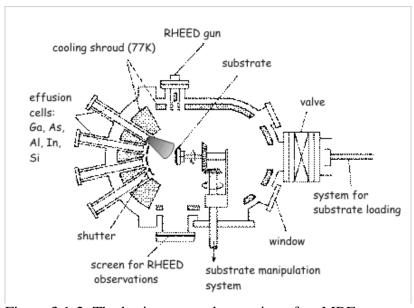

|    |      | 3.1.2         | Description of Fabrication Processes                   | 51         |

|    |      | 3.1.3         | Quantum Dot Properties and Formation                   | 52         |

|    | 3.2  | Capac         | citance-Voltage Measurements                           | 56         |

|    |      | 3.2.1         | Experiment and Results                                 | 56         |

|    |      | 3.2.2         | Analysis and Discussion                                | 60         |

|    | 3.3  | Pulse         | Measurements                                           | 66         |

|    |      | 3.3.1         | Experiment and Results                                 | 66         |

|    |      | 3.3.2         | Discussion                                             | 70         |

|    | 3.4  | Trans         | ient Current Measurements                              | 75         |

|    |      | 3.4.1         | Experiment and Results                                 | 75         |

|    |      | 3.4.2         | Discussion                                             | 76         |

|    | 3.5  | Conc          | lusions and Further Study                              | 84         |

|    | Refe | erences       |                                                        | 85         |

|    |      |               |                                                        |            |

|    |      |               |                                                        |            |

| ΑĪ | PEN  | DIX A         | : MODELING THE IMPEDANCE OF THE DEVICES                | 89         |

|    |      |               |                                                        |            |

|    | .nes | DIV.          | MATTA D. GODE                                          | ^ <b>-</b> |

| Al | 'PEN | DIX B         | : MATLAB CODE                                          | 97         |

#### Acknowledgements

I would like to thank my supervising professor, Mr. Eleftherios Iliopoulos, for his valuable guidance and help, and for appreciating my work. I would also like to express my thanks to Mr. Panagiotis Dimitrakis and Mr. Pascal Normand at IMEL/NCSR "Demokritos" for their indispensable collaboration on this project, as well as Caroline Bonafos at CEMES, CNRS, Toulouse, France for her contribution. I would like to thank Maria Kayambaki, whose help for the experimental part of my thesis was vital. My thanks also go to the members of my thesis committee and to anyone who takes an interest in this work.

What is more, I would like to thank my friends and colleagues at the University of Crete, Savvas Eftyhis, Alexandros Tzimis, and Katerina Papamichail for making me feel welcome and for pretending to listen to my academic problems. My thanks go to all my old friends, Maria, Effie, Giorgos, Iro, and Marina, for their love and for always providing a safe escape when I need it. I owe my gratitude to my parents, Afroditi and Manolis, for making my education possible and for other things, too many to be listed. My deepest love and thanks lastly go to my sister, Maria, and my dogs, Rabito and Roza, for the precious moments of stress relief.

#### **Abstract**

To investigate memory properties of GaN QDs, MOS capacitors were realized with GaN nanocrystals embedded in the SiO<sub>2</sub> dielectric. Samples were grown on n-type Si and Al was used as the metal gate. A reference sample with no QDs was also developed. High-frequency capacitance-voltage measurements were performed which revealed a wide hysteresis for all the samples except for the reference which exhibited no hysteresis for a full voltage sweep. C-V characteristics suggest electron injection that takes place from the substrate but limited hole injection. The width of the hysteresis was found to increase with the quantity of GaN embedded in the oxide. Pulse measurements confirm an asymmetry between electron and hole injection and suggest that erasing is more challenging than programming for these devices. Retention measurements at room temperature revealed good retention properties meeting the ten-year threshold for non-volatility. Finally, transient current measurements were performed to further investigate injection mechanisms.

The continuous floating gate transistor faces several challenges, the most significant of which is its scalability problem, and this does not allow NVMs to follow the rate of shrinkage of other integrated circuits. For that reason, several alternatives to the FG-MOSFET have been proposed in literature with the nanoparticle FG-MOSFET being a very prominent candidate. In this direction, GaN QDs could present two key advantages: compared to Si, GaN is considered to have a negative conduction band offset which could result in improved retention characteristics; in addition, it is fully compatible with current CMOS manufacture technologies. The current thesis investigates the potential of GaN QDs in NVMs.

The first chapter introduces the reader in the basic concepts of NVM, as well as the fundamental operation of the FG-MOSFET. The second chapter includes the theoretical background that is necessary for the understanding of this work. Physics of the MOS system are first described with emphasis on the capacitance of the device. The paragraphs that follow look into the properties of both the continuous and the nanoparticle floating gate respectively. Finally, chapter 3 describes the experimental process, the results and the analysis in full detail.

## **List of Figures**

| Figure 1.0-1: Floating-gate transistor: (a) elements of the transistor structure and (b) circuit symbol.                                                                                                           | 2  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1-1: Schematic representation of the basic FG-MOSFET.                                                                                                                                                     | 3  |

| Figure 1.1-2: I-V characteristics of a memory cell in program and erase states and the extraction of the memory window.                                                                                            | 4  |

| Figure 1.1-3: Reading principle for floating gate devices.                                                                                                                                                         | 5  |

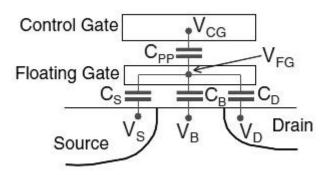

| Figure 1.1-4: Schematic cross-section of a floating gate NVM cell showing the intrinsic capacitances. $C_B = C_{TO}$ .                                                                                             | 6  |

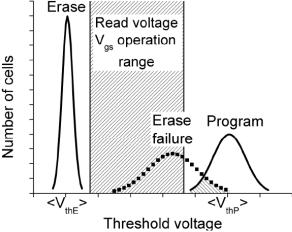

| Figure 1.2-1: Representation of threshold voltage distribution for the program and erase states of a Flash memory cell.                                                                                            | 7  |

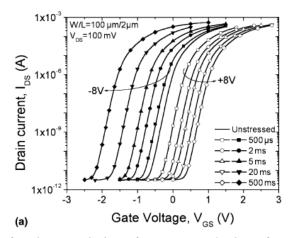

| Figure 1.2-2: Transfer characteristics of a memory device after application of $\pm 8V$ voltage pulsed of various durations.                                                                                       | 8  |

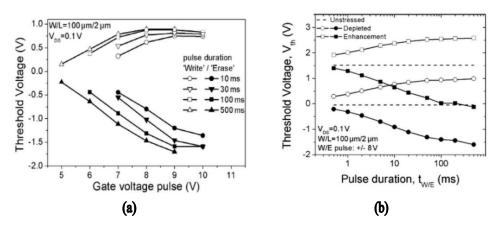

| Figure 1.2-3: Memory windows of NVM devices after application of different voltage pulses (a) dependence of the memory window on the amplitude of the pulse and (b) dependence on the pulse duration.              | 8  |

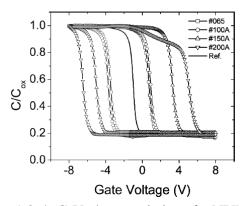

| Figure 1.2-4: C-V characteristics of a NVM cell.                                                                                                                                                                   | 9  |

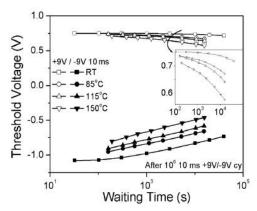

| Figure 1.2-5: Data retention characteristics of NVM devices at room temperature (RT), $85^{\circ}$ , $115^{\circ}$ , and $150^{\circ}$ C. Samples have also been stressed with $10^{6}$ P/E cycles (10 ms +9/-9V). | 10 |

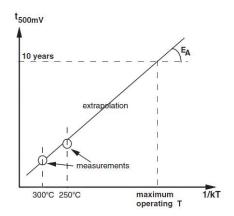

| Figure 1.2-6: Arrhenius diagram of a floating gate device.                                                                                                                                                         | 10 |

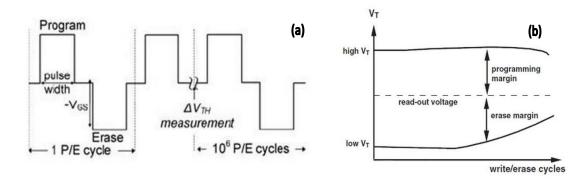

| Figure 1.2-7: (a) Schematic representation of the voltage pulse sequence which is used in endurance tests. (b) Endurance characteristics of a floating-gate device.                                                | 11 |

| Figure 2.1-1: (a) Structure of the MOS Capacitor. (b) Band diagram of the MOS capacitor in equilibrium.                                                                                                            | 18 |

| Figure 2.1-2: Band diagrams and charge distributions for the MOS capacitor.                                                                                                                                        | 19 |

| Figure 2.1-3: General behaviour of C-V curves of an ideal MOS system under different dc bias and ac small signal conditions.                                                                                       | 20 |

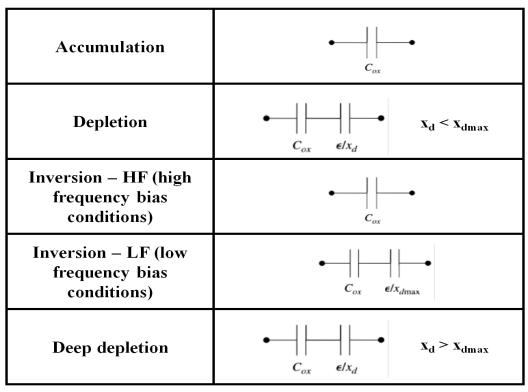

| Figure 2.1-4: Equivalent circuits for the overall capacitance of the MOS System under different bias conditions.                                                                                                   | 22 |

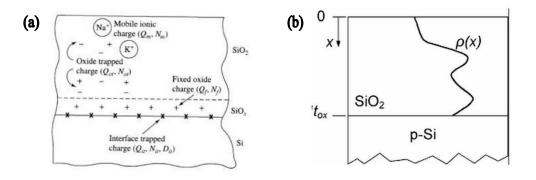

| Figure 2.1-5: (a) Four categories of oxide charge in the MOS system (b) Charge density distribution in an oxide layer.                                                                                             | 22 |

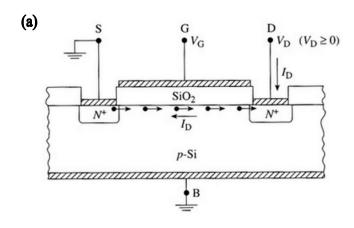

| Figure 2.1-6: (a) Schematic representation of the n-channel MOSFET. (b) Typical I-V characteristics of a MOSFET device. $V_{G4} > V_{G3} > V_{G2} > V_{G1}$ .                                                                                                                                  | 24 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

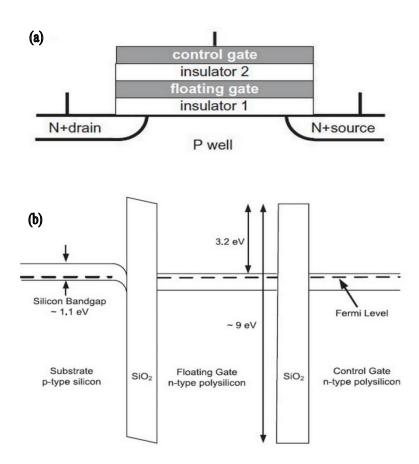

| Figure 2.2-1: (a) The FG-MOSFET. (b) Energy band diagram for a typical floating-gate structure.                                                                                                                                                                                                | 25 |

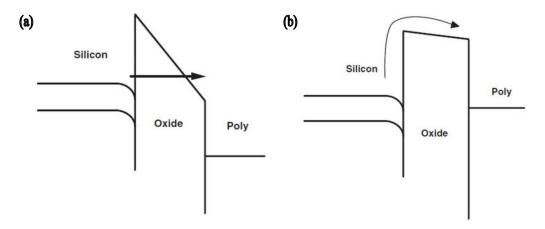

| Figure 2.2-2: (a) Energy band representation of Fowler-Nordheim tunnelling through thin oxides; electrons in the silicon conduction band tunnel through the triangular energy barrier. (b) Energy band representation of channel hot-electron injection (CHEI) in an n-channel MOS transistor. | 26 |

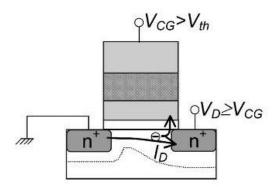

| Figure 2.2-3: Bias conditions for Channel Hot-Electron Injection mechanism for the storing of charge on the floating gate.                                                                                                                                                                     | 27 |

| Figure 2.2-4: Schematic representation of the charge density distribution of the stored charge in a floating gate memory cell.                                                                                                                                                                 | 28 |

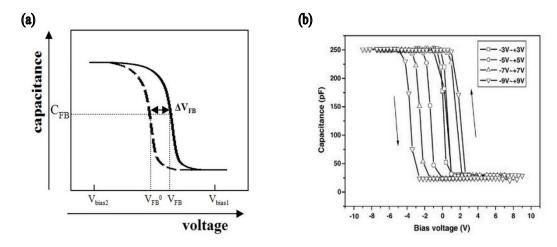

| Figure 2.2-5: (a) Hysteresis in the C-V characteristic of a floating gate memory device. The dashed curve corresponds to the state without any stored charge on the floating gate. (b) Read C-V tests performed on a memory device.                                                            | 29 |

| Figure 2.2-6: Shift of the C-V curves for different types of charge stored in the floating gate. The dashed curve corresponds to the state without any stored charge on the floating gate.                                                                                                     | 30 |

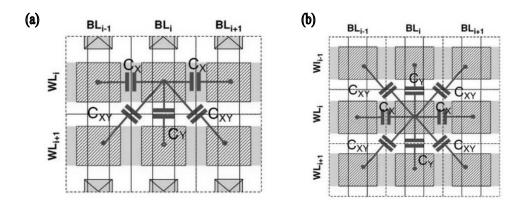

| Figure 2.2-7: Schematic drawing of parasitic capacitance among nearby cells in (a) NOR Flash array and (b) a NAND Flash array.                                                                                                                                                                 | 32 |

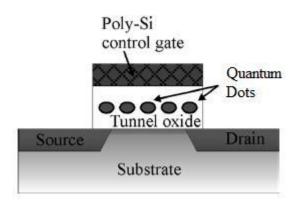

| Figure 2.3-1: Schematic representation of a nanocrystal memory cell.                                                                                                                                                                                                                           | 33 |

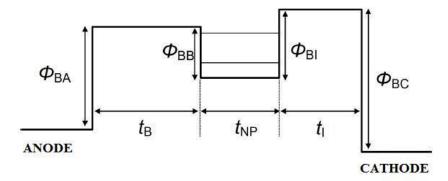

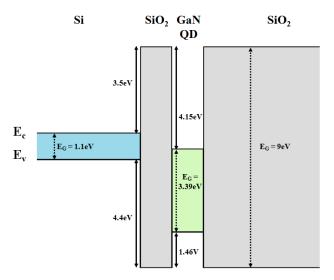

| Figure 2.3-2: One dimensional energy band diagram under flat-band conditions describing the basic structure for NP-based memory cells.                                                                                                                                                         | 34 |

| Figure 2.3-3: Schematic representation of the charge density distribution of the stored charge in NP-based memory.                                                                                                                                                                             | 34 |

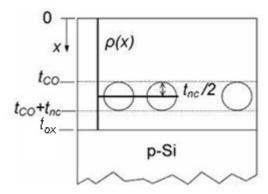

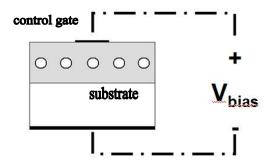

| Figure 2.3-4: Applying bias to the nanoparticle memory MOS capacitor.                                                                                                                                                                                                                          | 36 |

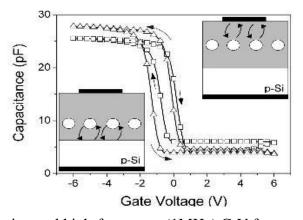

| Figure 2.3-5: Experimental high-frequency (1MHz) C-V for two NP-MOS capacitor memory cells where the 2-D array of nanoparticles is sited at different distances from the Si substrate, leading to different exchange mechanisms.                                                               | 36 |

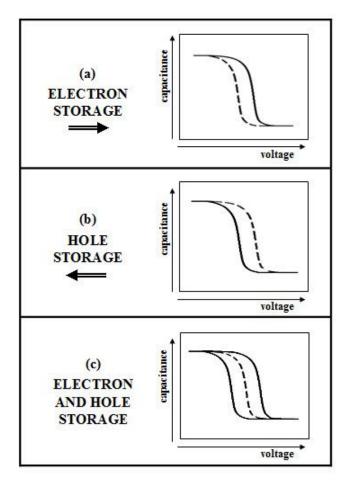

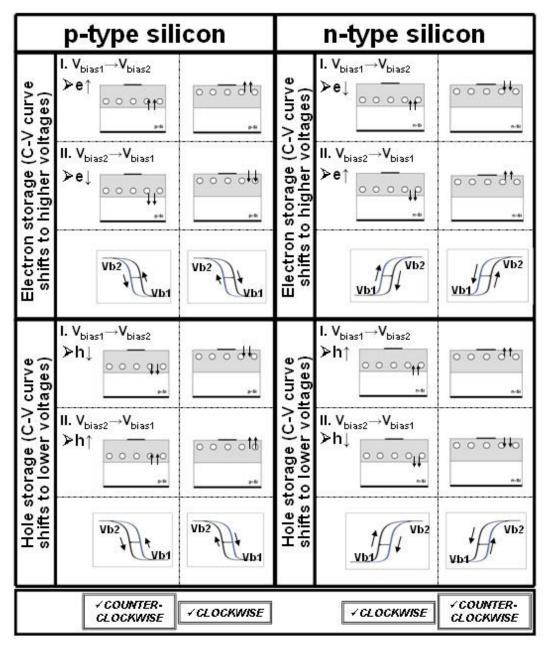

| Figure 2.3-6: Direction of the hysteresis loop in relation to the place of carrier injection.                                                                                                                                                                                                  | 37 |

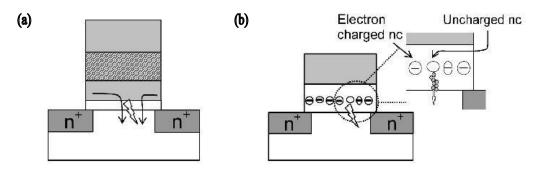

| Figure 2.3-7: The stored charge in a conventional FG NVM (a) is leaked entirely to the channel and the stored information is lost, while in a NP memory cell (b) only the quantum dot above the defect is discharged and hence the stored information remains.                                 | 38 |

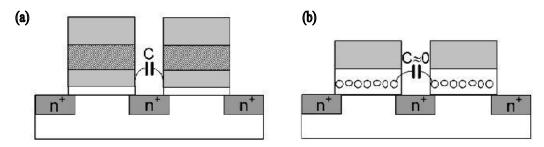

| Figure 2.3-8: Schematic representation of capacitive coupling between adjacent NVM cells in the case of (a) a continuous FG and (b) nanoparticle FG.                                                                                                                                           | 38 |

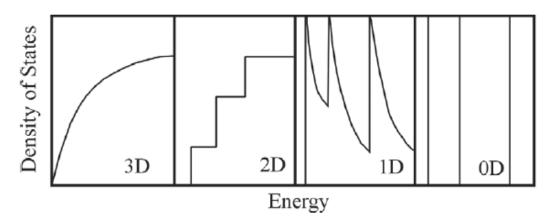

| Figure 2.4-1: Density of states vs. energy for a bulk material (3D), quantum well (2D), quantum wire (1D), and quantum dot (0D).                                                                                                                                                               | 40 |

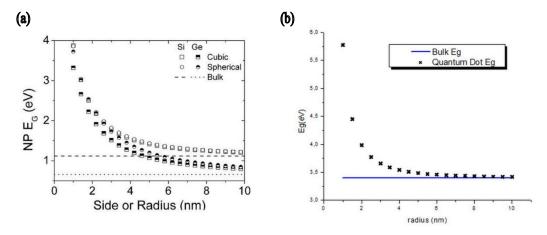

| Figure 2.4-2: (a) Dependence of the energy band-gap on the effective dimension of spherical and cubic Si and Ge nanoparticles. (b) Dependence of the energy band-gap on the radius of a spherical GaN QD.                                        | 41 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

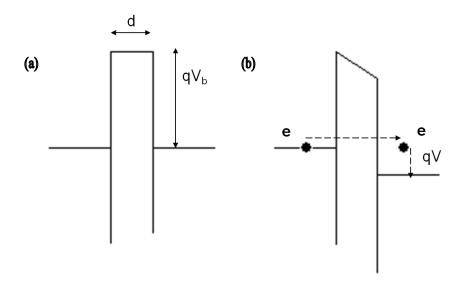

| Figure 2.4-3: Schematic representation of an electron tunnelling through a barrier.                                                                                                                                                              | 42 |

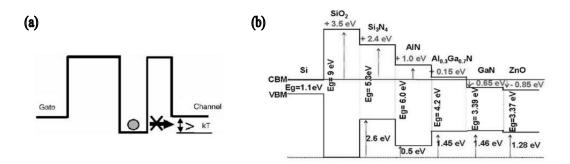

| Figure 2.4-4: (a) Energy barriers of a nanocrystal memory in the case of metallic nanoparticles with higher work function than silicon (channel area). (b) CBO (Conduction Band Offset) values of various materials compared to that of silicon. | 43 |

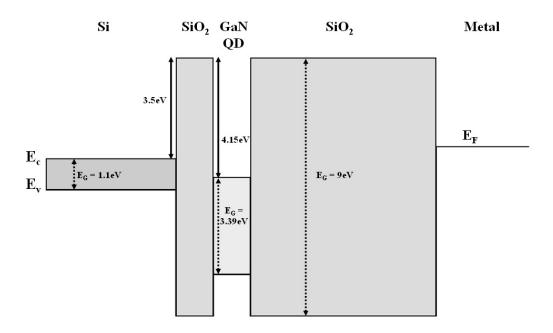

| Figure 2.4-5: One-dimensional energy band diagram of a non-volatile cell of the MOS type with GaN QDs.                                                                                                                                           | 44 |

| Figure 3.1-1: Structure of the GaN-QDs MOS Device.                                                                                                                                                                                               | 50 |

| Figure 3.1-2: The basic parts and operation of an MBE system.                                                                                                                                                                                    | 52 |

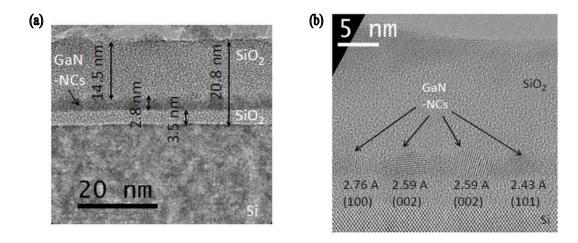

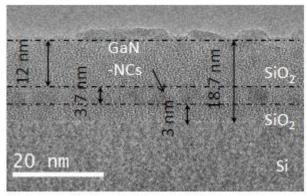

| Figure 3.1-3: TEM images of an early sample that show QDs in the oxide.                                                                                                                                                                          | 53 |

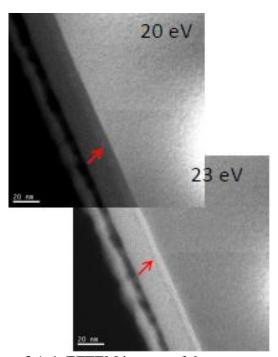

| Figure 3.1-4: EFTEM images of the same sample.                                                                                                                                                                                                   | 53 |

| Figure 3.1-5: TEM images for a second sample.                                                                                                                                                                                                    | 54 |

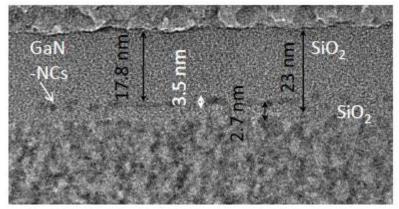

| Figure 3.1-6: TEM images for sample C2014.                                                                                                                                                                                                       | 55 |

| Figure 3.1-7: TEM images for sample C2015.                                                                                                                                                                                                       | 55 |

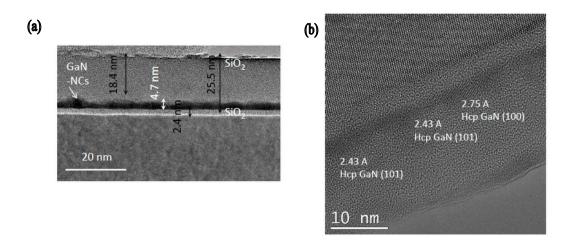

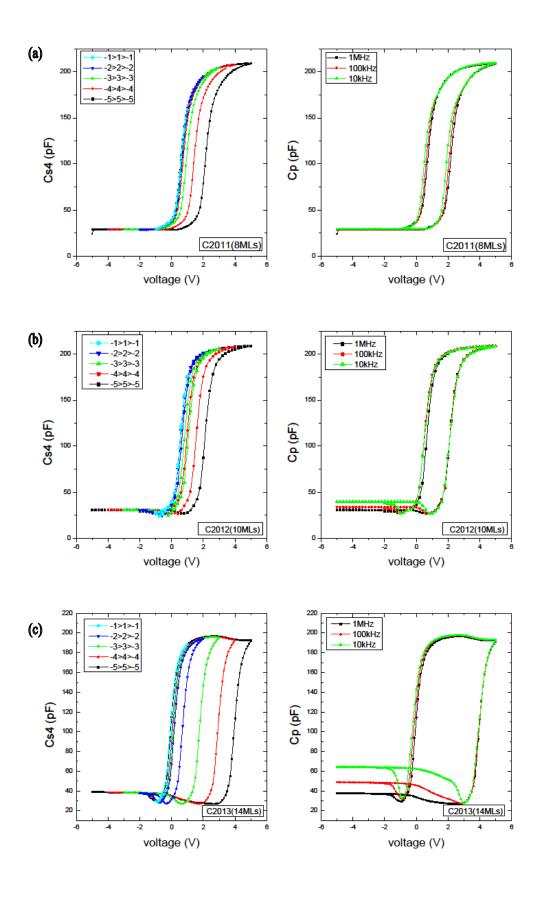

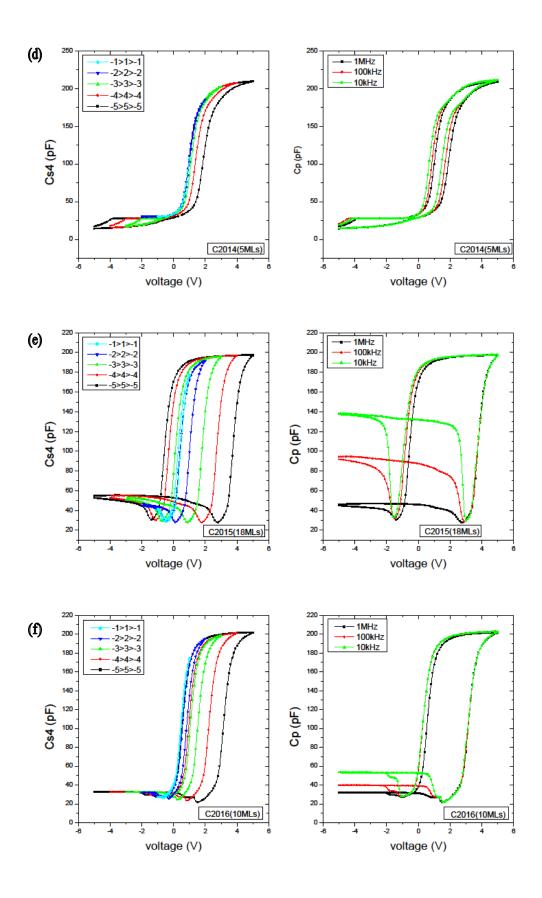

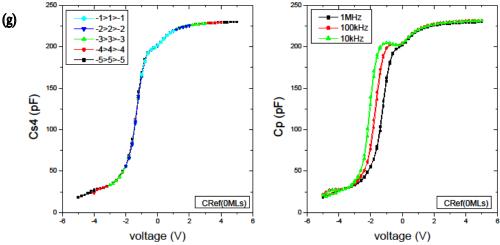

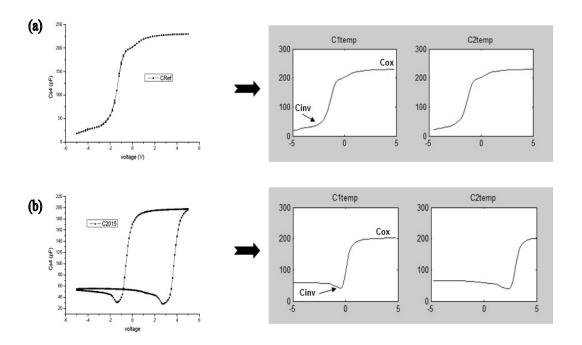

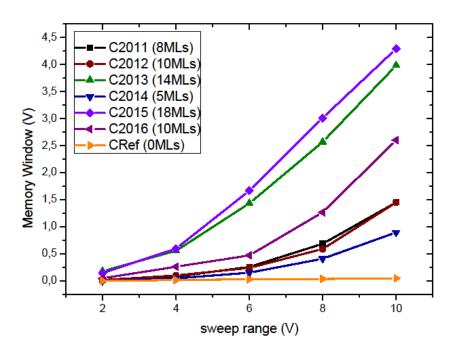

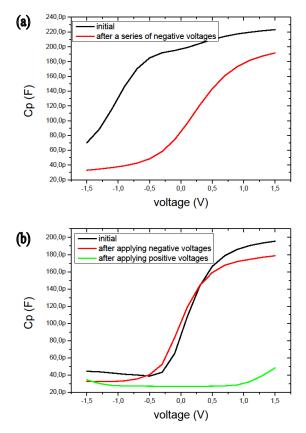

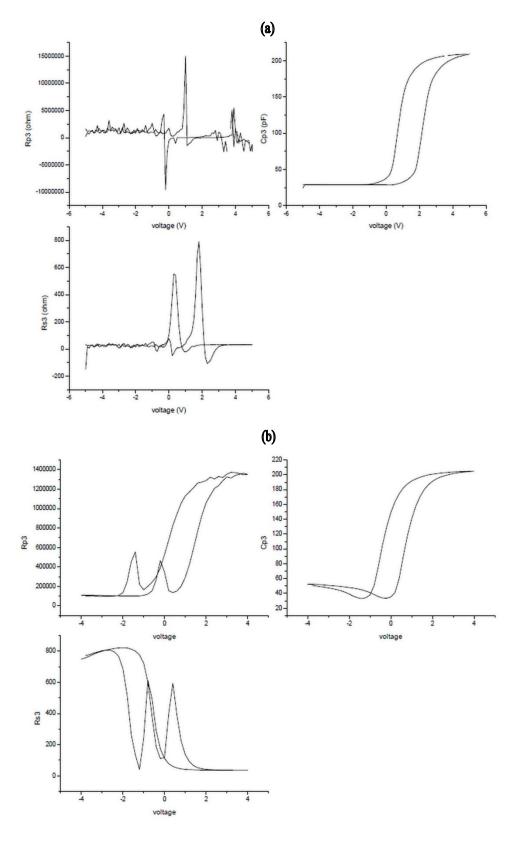

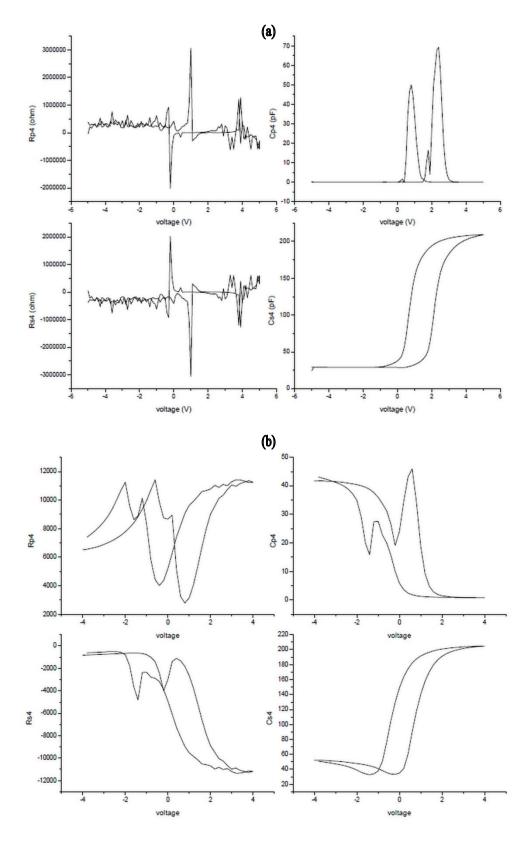

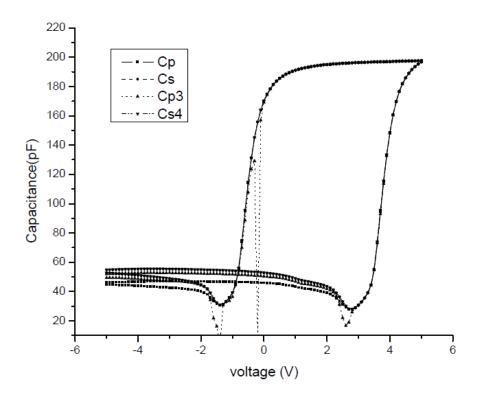

| Figure 3.2-1: C-V characteristics for different sweeps (on the left) and for different frequencies (on the right) for samples C2011 (a), C2012 (b), C2013 (c), C2014 (d), C2015 (e), C2016(f), and CRef (g).                                     | 59 |

| Figure 3.2-2: (a) The appearing hysteresis is clockwise for all the C-V curves. (b) Injection of electrons takes place from the substrate.                                                                                                       | 59 |

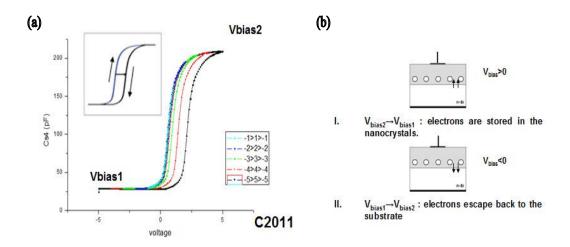

| Figure 3.2-3: Assigning $C_{\text{ox}}$ and $C_{\text{inv}}$ for CRef (a) and C2015 (b).                                                                                                                                                         | 60 |

| Figure 3.2-4: Memory Window vs the range of the C-V sweep for all the devices.                                                                                                                                                                   | 62 |

| Figure 2.3-5: Extraction of the memory window from the peaks in the parallel conductance: (a), (b) Examples of conductance-voltage characteristics. (c) Comparing the results with the ones extracted from the C-V curves.                       | 63 |

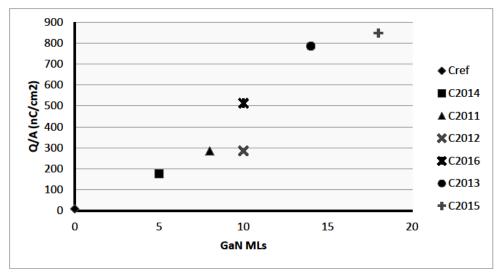

| Figure 2.3-6: Charge Density in the devices, as it is affected by the quantity of the deposited GaN.                                                                                                                                             | 65 |

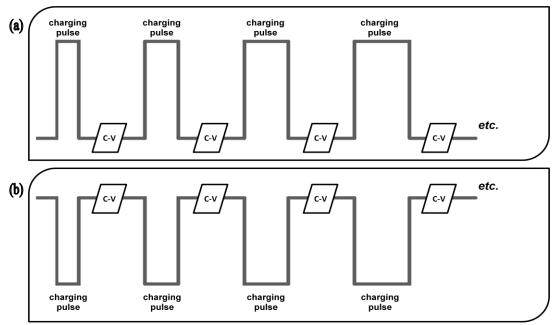

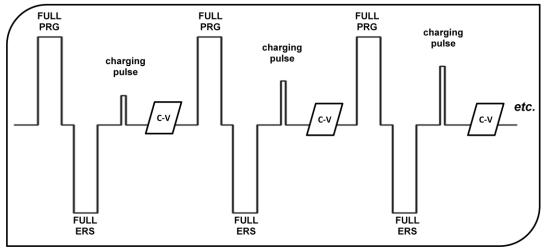

| Figure 3.3-1: The voltage pulse sequence, including the high-frequency C-V measurements, that was used that was used for (a) positive pulses (charging of the capacitors) and (b) negative pulses (discharging).                                 | 66 |

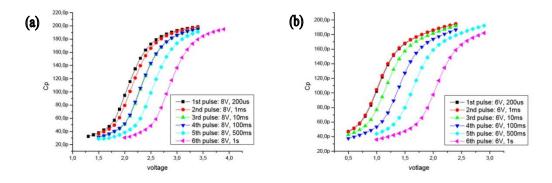

| Figure 3.3-2: Examples of how the C-V curve shifts during pulse measurements.                                                                                                                                                                    | 67 |

| Figure 3.3-3: The voltage pulse sequence usually used to help bring the device to its initial state before applying the charging pulse.                                                                                                          | 67 |

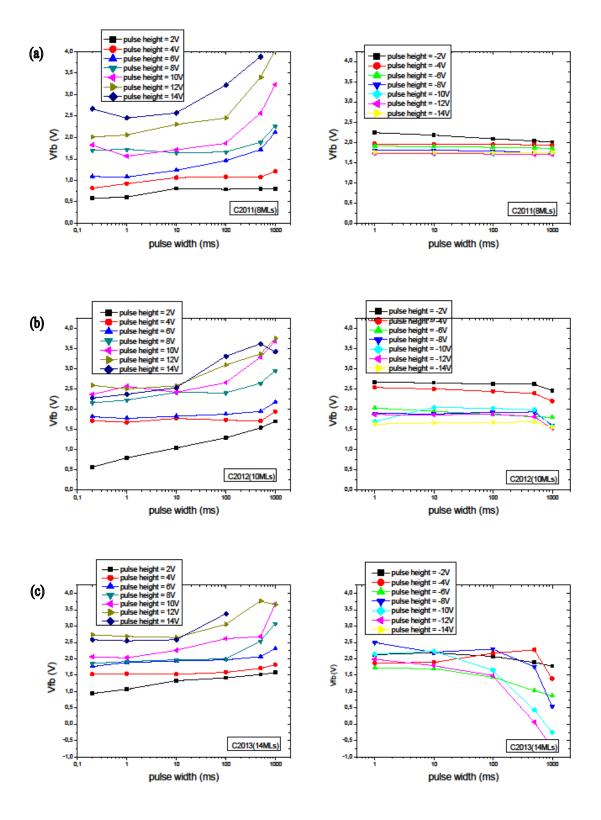

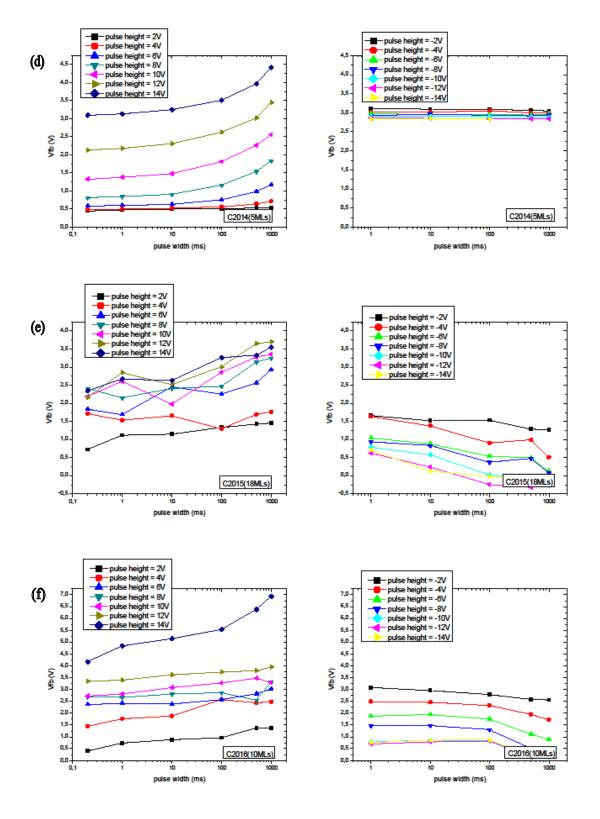

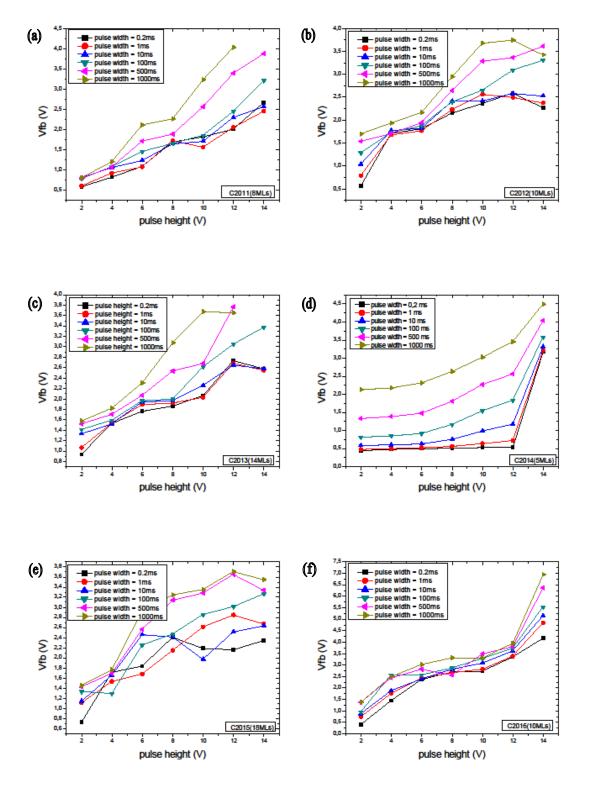

| Figure 3.3-4: Pulse Measurements: $V_{FB}$ vs pulse width for (a) C2011, (b) C2012, (c) C2013, (d) C2014, (e) C2015, and (f) C2016.                                                                                                           | 69 |

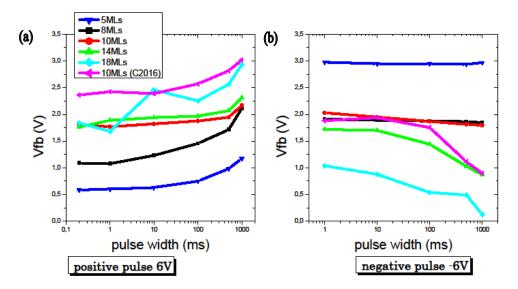

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.3-5: (a) The effect of a series of positive pulses of amplitude 6V on the samples, (b) The effect of a series of negative pulses of amplitude -6V on the samples.                                                                    | 71 |

| Figure 3.3-6: Band Diagram for the GaN QD memory devices.                                                                                                                                                                                     | 71 |

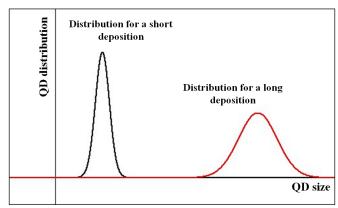

| Figure 3.3-7: The duration of the deposition affects the quantum dot size.                                                                                                                                                                    | 72 |

| Figure 3.3-8: $V_{FB}$ -pulse height plots for the charging of uncharged devices: (a) C2011, (b) C2012, (c) C2013, (d) C2014, (e) C2015, and (f) C2016.                                                                                       | 73 |

| Figure 3.3-9: $V_{FB}$ -pulse height plots for the discharging of charged devices: (a) C2011, (b) C2012, (c) C2013, (d) C2014, (e) C2015, and (f) C2016.                                                                                      | 74 |

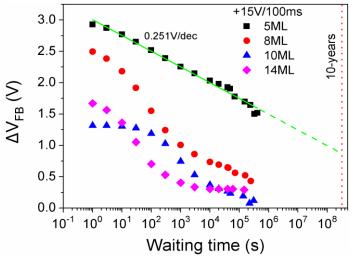

| Figure 3.4-1: Retention measurements at room temperature as were obtained by Dimitrakis, P., and Normand, P. at IMEL/NCSR Demokritos.                                                                                                         | 75 |

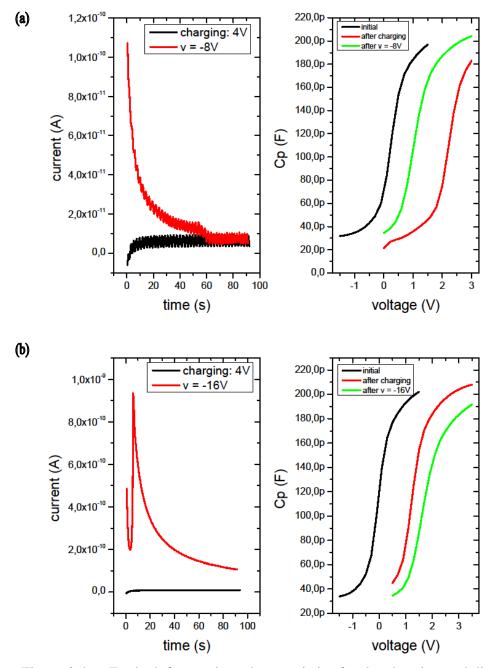

| Figure 3.4-2: DUT bias conditions and current flow for the transient measurements.                                                                                                                                                            | 76 |

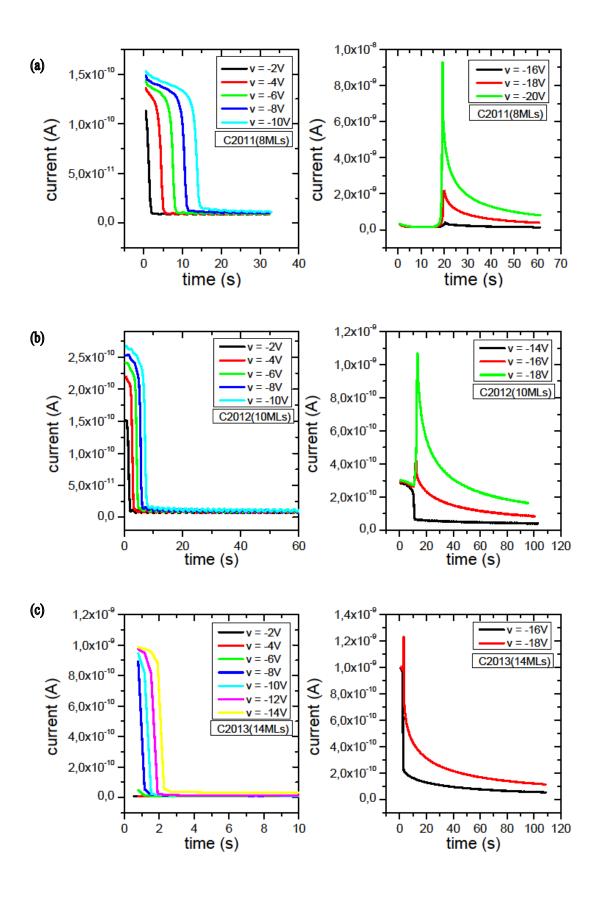

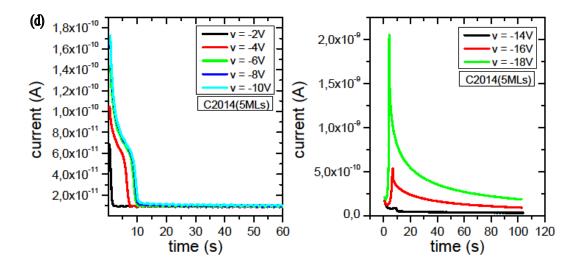

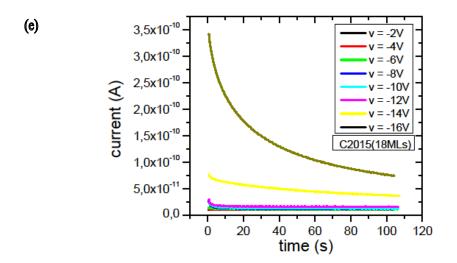

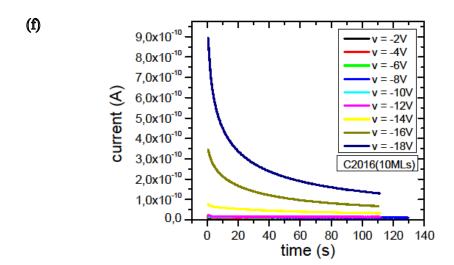

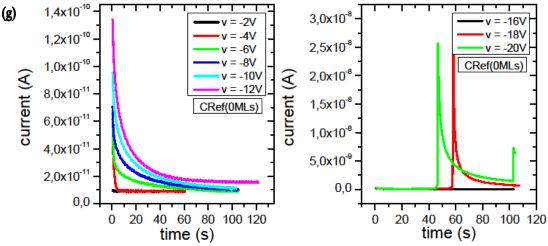

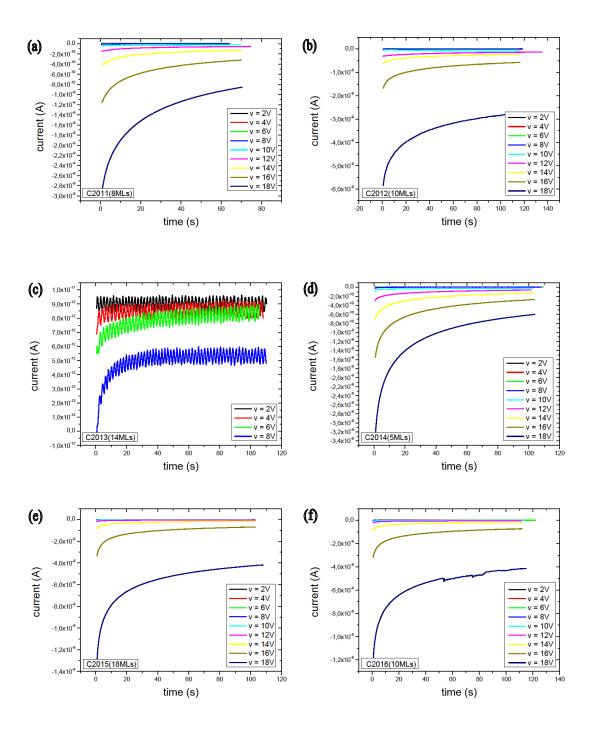

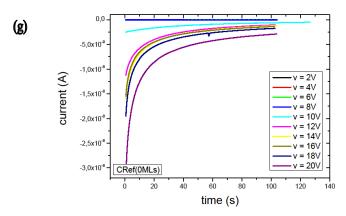

| Figure 3.4-3: Current transients at different negative voltages: (a) C2011 (8MLs GaN), (b) C2012 (10MLs GaN), (c) C2013 (14MLs GaN), (d) C2014 (5MLs GaN), (e) C2015 (18MLs GaN), (f) C2016 (10MLs GaN – lower III-V), and (g) CRef (no GaN). | 79 |

| Figure 3.4-4: Current transients at different positive voltages: (a) C2011 (8MLs GaN), (b) C2012 (10MLs GaN), (c) C2013 (14MLs GaN), (d) C2014 (5MLs GaN), (e) C2015 (18MLs GaN), (f) C2016 (10MLs GaN – lower III-V), and (g) CRef (no GaN). | 81 |

| Figure 3.4-5: C-V curves before and after applying bias voltages for samples C2011 (a), and sample C2015 (b).                                                                                                                                 | 81 |

| Figure 3.4-6: To the left: transient characteristics for the charging and discharging currents. To the right: capacitance shifts for the applied voltages. (a) applied voltage: -8V, (b) applied voltage: -16V (sample C2014).                | 82 |

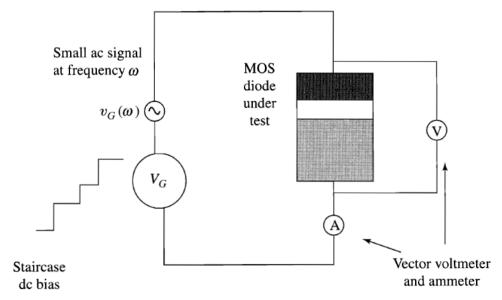

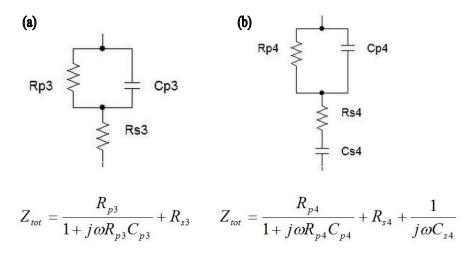

| Figure A.1: MOS C-V measurement system. The voltmeter and ammeter measure both the magnitude and the phase of the voltage across the diode and the current through it.                                                                        | 89 |

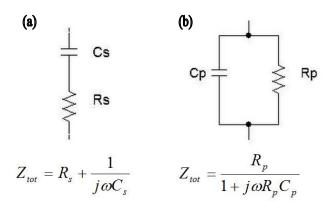

| Figure A.2: Two-element models: (a) series model, (b) parallel model,                                                                                                                                                                         | 90 |

| Figure A.3: Two-frequency models: (a) three-element model, (b) four-element model.                                                                                                                                                            | 90 |

| Figure A.4: Calculating the elements for all four models.                                                                                                                                                                                     | 91 |

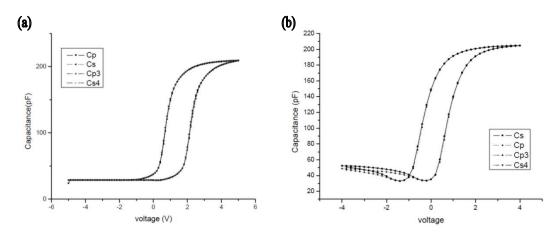

| Figure A.5: The capacitances calculated from all four models are compared for two different devices: device (a) and device (b).                                                                                                               | 92 |

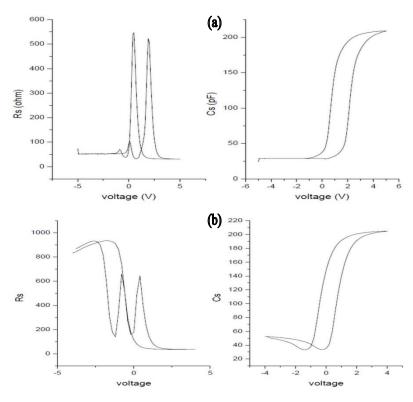

| Figure A.6: Series models for device (a) and device (b).                                                                                                                                                                                      | 93 |

| Figure A.7: Parallel models for device (a) and device (b).                                                | 93 |

|-----------------------------------------------------------------------------------------------------------|----|

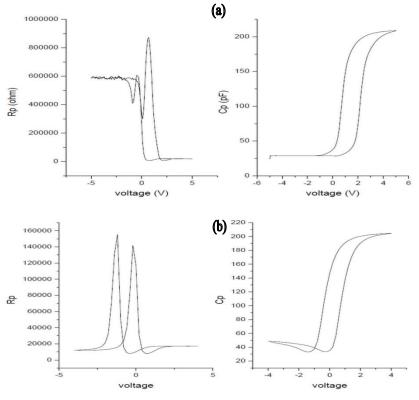

| Figure A.8: Three-element model for device (a) and device (b).                                            | 94 |

| Figure A.9: Four-element models for device (a) and device (b).                                            | 95 |

| Figure A.10: The three-element model sometimes exhibits instabilities compared to the other three models. | 96 |

### **List of Tables**

| Table 1.0-1: Nonvolatile Memory Functional Capability Classifications. | 2  |

|------------------------------------------------------------------------|----|

| Table 3.1-1: Description of the fabricated samples.                    | 50 |

| Table 3.2-1: Calculated values for all of the samples.                 | 62 |

| Table 3.2-2: Calculated charge density for the devices.                | 64 |

## **CHAPTER 1**

## **Introduction to Nonvolatile Memories**

Semiconductor memory is an essential part of modern information processors. The length of time that the memory can retain the data is a property called *retention* and the unpowered retention time parameter is the measure of *non-volatility*. A volatile memory will typically have a worst-case retention time of less than a second. A nonvolatile memory (NVM) is usually specified as a worst-case unpowered retention time of 10 years, although this parameter can vary from days to years depending on the specific memory technology and application. Integrated circuit nonvolatile memories are frequently further classified in terms of the degree of functional flexibility available for modification of stored contents (table 1.0-1). It should be mentioned here that out of the different categories of nonvolatile memory, Flash memory is of great significance. Flash memory is an EEPROM where the entire chip or a subarray within the chip may be erased at one time and it has been the dominant form of NVM over the years.

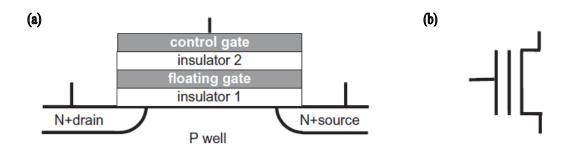

The conventional NVM device is the floating-gate MOS Field Effect Transistor (FG-MOSFET). The FG-MOSFET makes use of charge storage on a *floating gate*, a thin layer formed within the gate insulator of a field effect transistor between the gate electrode (the control gate) and the channel, usually made of polysilicon. The basic structure of a FG-MOSFET is presented in figure 1.0-1. The amount of charge on the floating gate determines if the transistor will conduct when a fixed set of 'read' bias conditions are applied. Because the floating gate is surrounded by insulators, it can retain its charge for long periods of time and in this way non-volatility is ensured.

The present chapter reviews the function principles of a simple NVM cell and introduces important characteristics and basic concepts that are useful in the study of nonvolatile memories.

| Acronym             | Definition                             | Description                                                                                                                                                 |

|---------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROM                 | Read-only memory                       | Memory contents defined manufacture and                                                                                                                     |

|                     |                                        | not modifiable.                                                                                                                                             |

| <b>EPROM</b>        | Erasable programmable                  | Memory is erased by exposure to UV light                                                                                                                    |

|                     | ROM                                    | and programmed electrically.                                                                                                                                |

| EEPROM              | Electrically erasable programmable ROM | Memory can be both erased and programmed electrically. The se of 'EE' implies block erasure rather than byte erasable.                                      |

| E <sup>2</sup> PROM | Electrically erasable programmable ROM | Memory can be both erased and programmed electrically as for EEPROM, but the use of 'E <sup>2</sup> ' implies byte alterability rather than block erasable. |

Table 1.0-1: Nonvolatile Memory Functional Capability Classifications.

Figure 1.0-1: Floating-gate transistor: (a) elements of the transistor structure and (b) circuit symbol.

#### 1.1 THE FLOATING GATE: STRUCTURE AND BASIC OPERATION

#### 1.1.1 Structure of a FG-MOSFET

The basic structure of a FG-MOSFET is again presented in more detail in figure 1.1-1.

Figure 1.1-1: Schematic representation of the basic FG-MOSFET.

As it is shown, like a plain MOS Field Effect Transistor, it includes a source and a drain, two highly doped regions on a silicon substrate (body). The current will be conducted from source to drain (for a p channel) or from drain to source (for an n channel) when an inversion layer is formed. The inversion layer is formed, again, like a regular MOSFET, by the bias applied to the gate, only for a FG-MOSFET we call it a 'control gate' to distinguish it from the *floating gate*. The floating gate is a thin layer, usually made of polysilicon that lies between the control gate and the substrate and is isolated from both by two layers of dielectric: the injection oxide that separates it from the body and the interpoly dielectric that separates it from the control gate. The injection oxide (also called the tunnel oxide) is usually a thin (≥6nm) layer of silicon oxide and it is so called because it is where the charge of the floating gate is injected through. The interpoly dielectric (or control dielectric or control oxide) comprises of one or more types of dielectric; its purpose is not to allow the charges to escape to the control gate and should, therefore, be somewhat thicker than the injection oxide.

#### 1.1.2 Operation Principles with Basic Equations

For a plain MOSFET device, the threshold voltage is usually defined as the gate voltage where an inversion layer forms at the interface between the oxide and the substrate. The inversion layer's forming allows the flow of carriers along the gate-source junction and, practically, the threshold voltage is the voltage at which there are sufficient minority carriers in the inversion layer to make a low resistance conducting path between the MOSFET source and drain.

The operation principle of FG-NVM is essentially based on the switching of the MOSFET's threshold voltage  $V_{th}$  between a low and a high value. This is achieved by storing an amount of charge into the floating gate. Since the floating gate controls at

least part of the underlying transistor channel, the charge on this gate will directly influence the current in the channel. The mechanism is in short, the following:

For simplicity, let us assume the charge that is stored in the floating gate comprises of electrons, even though a similar case can be made if the stored charge is positive (holes). The storage of negative charge reduces the channel potential and hence decreases the current flowing from the source to the drain. A negatively charged floating gate increases the threshold voltage and leads to a parallel shift of the transfer characteristics  $I_{DS}$ - $V_{GS}$  with respect to the uncharged transistor (fig. 1.1-2). The shift can be calculated by the following expression:

$$V_{thW} = V_{th0} + Q_W / C_{IPD}$$

where  $V_{thW}$  and  $V_{th0}$  are the threshold voltage values after and before electron storage

respectively,

$$Q_W$$

is the amount of stored electrons (in Cb) and  $C_{IPD} = \frac{\varepsilon_{IPD} A}{t_{IPD}}$  is the

capacitance (in F) of the interpoly dielectric. A is the gate area,  $\epsilon_{IPD}$  is the dielectric constant of the interpoly dielectric and  $t_{IPD}$  is the interpoly dielectric thickness. This high  $V_{th}$  state is commonly named *Write* or *Program* state. If the stored mount of charge is decreased to

$$V_{thE} = V_{th0} + Q_E / C_{IPD}$$

.

This new state is usually named  $\mathit{Erase}$  state and the difference between  $V_{thW}$  and  $V_{thE}$  is called  $\mathit{memory window}$ :

$$\Delta V_{th} = V_{thW} - V_{thE} = Q/C_{IPD}$$

.

The operation that corresponds to the transfer of information from the outside world into the memory cell is referred to as the programming or write operation, whereas the operation that establishes the initial condition of the cell is called the erase operation.

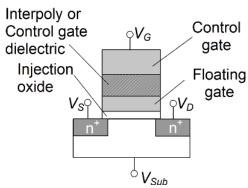

Figure 1.1-2: I-V characteristics of a memory cell in program and erase states and the extraction of the memory window.

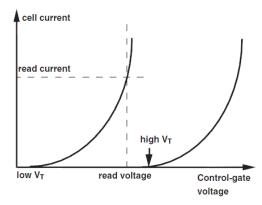

Finally, the readout operation, communicates the current state (Write or Erase) of the memory cell to the outside world. The individual state of a cell, corresponding to the logic '0' or '1', is detected by applying a gate voltage in between the  $V_{thW}$  and  $V_{thE}$  values. Specific circuits sense the current flowing from the source to drain,  $I_{DS}$ , and indicate whether the transistor is 'ON' or 'OFF', i.e. whether the cell is in the

erase or the program state respectively. The readout operation uses a readout voltage that lies somewhere between the two distinct threshold voltages (fig. 1.1-3).

We note, that in the case that the stored charge is positive, the threshold voltage accordingly shifts to lower voltages, since the channel potential is enhanced:

$$V_{th} = V_{th0} - Q/C_{IPD}$$

In any case, the low  $V_{th}$  state is usually considered as the erase state while the high  $V_{th}$  state is the write state. In order to set the memory cell in the program state (logic state '1'), the floating gate should be charged negatively. Erasure of the programme state (logic state '0') requires at the very least the extraction of the stored electrons from the floating gate even though it is possible to have injection of holes; this further widens the memory window.

Figure 1.1-3: Reading principle for floating gate devices.

#### **Gate Coupling Ratio**

The floating-gate device, as operated from the control gate and the drain, acts as a metal-oxide-semiconductor transistor but with slightly different characteristics. The main reason is that the external control gate of the cell is not directly controlling the transistor channel. The floating gate, however, has a more direct impact on the transistor channel while it is biased only through capacitive coupling from other terminals (mainly the control gate).

A main parameter for characterizing memory cells is, therefore, the gate coupling ratio, which is defined as the ratio of the control-gate-to-floating-gate capacitance and the overall floating-gate capacitance (fig. 1.1-4). Basically, it quantifies the percentage of control gate voltage that is coupled form the control gate to the floating gate in any operation mode. The subthreshold slope of the memory cell as measured from this control gate is smaller than that of the floating-gate transistor by a factor equal to this gate-coupling ratio.

A general expression for the coupling ratio is:

$$\alpha = \frac{C_{PP}}{\sum_{i} C_{j}}$$

which becomes, if one considers only the capacitance of the tunnel oxide to be important:

$$\alpha = \frac{C_{PP}}{C_{TO} + C_{PP}}$$

where  $C_{TO}=\frac{\mathcal{E}_{TO}A}{t_{TO}}$  is the capacitance of the injection (tunnel) oxide. In case the tunnel oxide and the interpoly dielectric are made of the same material, the coupling factor becomes  $\alpha=\frac{t_{TO}}{t_{TO}+t_{IPD}}$ .

Figure 1.1-4: Schematic cross-section of a floating gate NVM cell showing the intrinsic capacitances ( $C_B = C_{TO}$ ).

#### 1.2 MEMORY CHARACTERISTICS: CONCEPTS AND DEFINITIONS

The floating gate transistor is the most fundamental and most common of all non-volatile memory devices and the study of its function is essential if we are to gain an understanding of the elemental theory of non-volatile memory. Of course, there are many more different kinds of devices for non-volatile memory; however, in order to characterize all of them one needs to familiarize themselves with some of the concepts that are usually used to evaluate their behaviour and their effectiveness. In this paragraph, we attempt to introduce these concepts, give definitions and explain their importance.

#### 1.2.1 Memory Window

As it was mentioned earlier, the memory window of a memory cell is the difference between the higher and the lower values of the threshold voltages of its two distinct states, the program (or write) state and the erase state. The memory window plays a particularly important role in the effectiveness of the readout operation. To read the state of a memory device, a set of bias voltages is applied. A voltage pulse is applied on the control gate and the amplitude of that pulse lies somewhere between the lower and the higher threshold voltages of the device. Subsequently, the current that flows through the device is sensed by a highly sensitive current detecting circuit: if the current is higher (lower) than a predetermined value at these certain bias conditions then the cell is considered to be erased (programmed). If the memory window is too narrow there is a greater chance of an incorrect readout. Especially when dealing with large arrays of memory cells, the extracted threshold voltage may exhibit a statistical distribution around a central value (fig. 1.2-1), and a wide memory window makes it easier to avoid overlapping.

It becomes therefore obvious why the memory window is one of the critical measures for the evaluation of the performance of a non-volatile memory cell.

Figure 1.2-1: Representation of threshold voltage distribution for the program and erase states of a Flash memory cell.

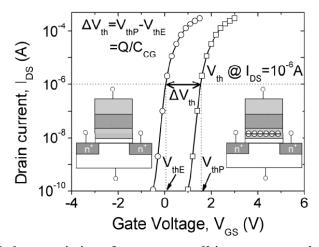

The memory window can be measured if one extracts the current-voltage  $I_{DS}$ - $V_{GS}$  characteristics of a NVM memory cell after applying a series of positive and negative

voltages on the control gate. As mentioned above, the pulses result in the shifting of the characteristics to either more positive or more negative values (fig. 1.2-2). The threshold voltage can then be calculated for each one of the characteristics using one of the many methods in literature, the simplest and most common of which is the constant current method. The constant current method evaluates  $V_{th}$  as the gate voltage corresponding to a given arbitrary constant drain current, a typical value for which is  $(W_m/L_m)*10^{-7}$  where  $W_m$  and  $L_m$  are the mask channel width and length respectively.

Of course, when extracting the memory window as described above, one must keep in mind that the resulting value depends both on the duration and the amplitude of the pulse (fig. 1.2-3), even though after a certain voltage the window stops to vary significantly (fig 1.2-3a).

Figure 1.2-2: Transfer characteristics of a memory device after application of  $\pm 8V$  voltage pulsed of various durations.

Figure 1.2-3: Memory windows of NVM devices after application of different voltage pulses (a) dependence of the memory window on the amplitude of the pulse and (b) dependence on the pulse duration.

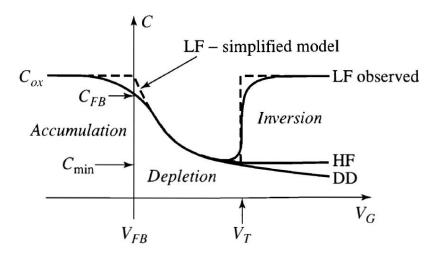

Frequently, however, a different method is used in order to estimate the memory window. The method involves performing capacitance-voltage (C-V) measurements on the NVM device. The charge storage results in a hysteresis in the C-V characteristic as the voltage sweeps from inversion to accumulation and back to

inversion (fig. 1.2-4). The width of the hysteresis in the characteristic is a measure of the memory window, and is, of course, dependent on the range of the voltage sweep. This is more thoroughly discussed in following chapters.

Figure 1.2-4: C-V characteristics of a NVM cell.

The advantages of this method is that it is simple and gives quick results even though sometimes it is possible to overestimate the memory window. Most importantly, it does not require a four terminal device: two terminal MOS-C-type structures suffice for the measurement and such a structure can be much more easily realized.

#### 1.2.2 Retention

The most important requirement for a nonvolatile memory cell is the ability to preserve the stored data for long periods of time without the need for external power supply. That ability is called *charge* or *data retention* and the key aspect of a NVM device is its *retention time*. The retention time can be defined as the time between data storage and the first erroneous readout. For true non-volatility at least ten years of charge retention are required. In any other case the NVM cell is deemed unreliable.

Each non-volatile storage technology employs a particular storage mechanism and properties associated with that mechanism and its implementation format will determine the retention characteristics of the device. For FG-MOSFETs as discussed above, the storage mechanism is to hold charge on its floating gate.

The measurement procedure of the retention time comprises of three basic steps. First, the memory device under test is selected and programmed or erased. Next, the device is stored in a controlled temperature place (e.g. a furnace) with no bias to its electrodes. After a pre-determined time has elapsed, the device is taken out of the storage place and the threshold voltage is measured. This procedure is repeated until the total storage (or waiting, or bake) time exceeds  $10^4$  s. Semi-logarithmic plots of  $V_{th}$  versus the waiting time (t) at different temperatures are presented in figure 1.2-5.  $V_{th}$  then shows a dependence on time that can be described by the equation:  $V_{th} = K_1 - K_2 \log(t)$ , where  $K_1$  and  $K_2$  are constants. Of course, any change in  $V_{th}$  is proportional to the charge loss:

$$\Delta V_{th} = KQ(t)$$

.

Figure 1.2-5: Data retention characteristics of NVM devices at room temperature (RT),  $85^{\circ}$ ,  $115^{\circ}$ , and  $150^{\circ}$  C. Samples have also been stressed with  $10^{6}$  P/E cycles (10 ms +9/-9V).

Figure 1.2-6: Arrhenius diagram of a floating gate device.

Data retention is sensitive to many parameters. The most important of them are (a) the device history, (b) the ambient temperature (raise in temperature results in the increase of the  $K_2$  parameter in the relationship above), and (c) the thickness and the quality of the injection and control oxide layers. Dependence on temperature is particularly significant because for higher temperatures the charge loss proceeds with faster rates. That is the reason why in practice, temperature accelerated tests are used (typically  $250^{\circ}$  to  $300^{\circ}$  C) that enhance the charge loss mechanism.

The bake time corresponding to a given threshold voltage shift is displayed as a function of the inverse of the absolute temperature. Figure 1.2-6 shows such a log (time) versus 1/T result, which is known as an Arrhenius plot. From practical experience, it is known that this relationship describes the temperature dependence of the charge loss mechanism quite well. This not only allows data taken at high temperatures to be extrapolated to predict what will happen at room or operating temperatures, but also helps extract the activation energy  $E_A$  of the dominant charge loss mechanism. And once the activation energy is known, one can then identify the charge loss mechanism itself. Mathematically, if the abscissa is 1/kT (with k Boltzmann's constant), the slope of this curve will be equal to the activation energy:

$$t_{\Delta V_t} \sim \exp(E_A/kT).$$

It should be noted that temperature accelerating testing has its drawbacks and sometimes yields retention times that can be misleading because the operation temperatures of a NVM cell are in reality different. In addition, the memory window of a device is affected by the readout operations and such tests do not take that into account.

#### 1.2.3 Endurance

The processes employed to write and/or read cells will result in stresses that eventually degrade the properties of the memory or disturb the contents of the memory. *Endurance* is the term used to describe the ability of a device to withstand these stresses, and it is quantified as a minimum number of erase-write cycles or write-read cycles that the chip can be expected to survive. For quite a number of years the industry has used 100,000 cycles as the minimum competitive endurance requirement. High performance NVMs must even meet the requirement for one million program/erase cycles. The write/erase cycling endurance (or endurance for short) of a floating-gate device is the major reliability characteristic because it describes the gradual degradation of the cell and, therefore, its lifetime in terms of the number of write/erase cycles that can be applied before failure.

For a single cell, endurance is usually monitored by measuring the threshold voltage window as a function of the number of applied write/erase cycles (fig 1.2-7). The lower  $V_{th}$  should not increase above a certain value in order to guarantee sufficient readout current. An important remark is that the cell-level endurance tests always underestimate the lifetime of the cell because a large number of cycles are applied to the cell in a very short period in order to reduce test time. In practice, there will be more time in between cycles, and the degradation will be relaxed because of recovery effects.

Figure 1.2-7: (a) Schematic representation of the voltage pulse sequence which is used in endurance tests. (b) Endurance characteristics of a floating-gate device.

#### 1.2.4 Other Performance Aspects of NVM Cells

As we have mentioned earlier, the memory devices are programmed, erased and read by applying voltage pulses of specific amplitudes and durations. The duration of

those pulses is a measure of the *speed* of the NVM devices and for fast memory cells short duration pulses are desired. It is also desirable that the device operates with as low voltages as possible so that the *power consumption* is kept to minimum values.

Another very important issue with non-volatile memories is the size of the device. Clearly, it is preferable to have memory cells that are as small as possible because the smaller the devices, the more of them can be integrated on a single microchip. Unfortunately, as the dimensions of the device shrink, the FG-MOSFET is faced with several challenges. The main problem is that as the injection oxide gets thinner it becomes easier for the stored charge to tunnel from the floating gate back to the substrate and the result is that retention characteristics deteriorate dramatically. Additionally, devices for logic applications that do not face such problems move a lot faster to shorter technology nodes. The result is a technology mismatch between memory devices and devices for logic applications and that makes difficult the implementation of embedded memory units. To overcome these difficulties alternative ideas for memory cells have been proposed one of which is the nanoparticle non-volatile memory cell which is the subject of this thesis.

#### **REFERENCES**

- [1] Brewer, J. E. (ed.), and Gill M. (ed.), (2008) *Nonvolatile Memory Technologies with Emphasis on Flash: A Comprehensive Guide to Understanding and Using NVM Devices*. New Jersey: John Wiley and Sons.

- [2] Khriachtchev, L. (ed.) (2009) *Silicon Nanophotonics: Basic Principles, Present Status and Perspectives.* Singapore: Pan Stanford Publishing Pte Ltd.

- [3] Dimitrakis, P., (2006) *Nanoparticle Electronics*. Ph.D., National Technical University of Athens.

- [4] Dimitrakis, P., Kapetanakis, E., Normand, P., Skarlatos, D., Tsoukalas, D., Beltsios, K., Clavarie, A., Benassayag, G., Bonafos, C., Chassaig, C., Carrada, M., and Soncini, V. (2003) *MOS Memory Structures by Very-Low-Energy Implanted Si in Thin SiO*<sub>2</sub>. Materials Science and Engineering, B101, pp. 14-18.

- [5] Dimitrakis, P., Kapetanakis, E., Tsoukalas, D., Skarlatos, Bonafos, C., Benassayag, G., Clavarie, A., Perego, M., Fanciulli, M., Soncini, V., Sotgiu, R., Agarwal, A., Ameen, M., Sohl, C., and Normand, P. (2004) *Silicon Nanocrystal Memory Devices Obtained by Ultra-Low Energy Ion-Beam Synthesis*. Solid State Electronics, 48, pp. 1511-1517.

- [6] Ortiz-Conde, A., Garcia, F. J., Lion J. J., Cerdeira, A., Estrada, M., and Yue, Y. (2002) *A Review of Recent MOSFET Threshold Voltage Extraction Methods. Microelectronics Liability*, 42, pp. 583-596.

- [7] Ghetti, A., Bortesi, L., Vendrame, L. (2005) 3D Simulation Study of Gate Coupling and Gate Cross-Interference in Advanced Floating Gate Non-Volatile Memories. Solid State Electronics, 49, pp. 1805-1812.

## **CHAPTER 2**

## **Theoretical Background**

The floating-gate MOS device, which is, as discussed in the previous chapter, the fundamental cell for non-volatile memory, is based on the operation of the MOS-Field-Effect-Transistor, the most common of all the electronic devices in integrated circuits. So do a lot of other types of non-volatile memories including nanocrystal memory cells. The MOSFET, in turn, takes advantage of the properties of the Metal-Oxide-Semiconductor structure. For that reason, it becomes necessary that we examine some of the operation principles of the MOS junction, and the MOSFET, in this chapter. The focus is, of course, on those properties relevant to the behavior of memory devices and for a full review the reader is prompted to go through the related literature.

So far, only the general concepts of non-volatile memory have been introduced. Yet, the need to optimize memory devices requires a full understanding of their function as well as the challenges they face. To do that, this chapter next takes a closer look at the FG-MOSFET and the physics involved in the mechanisms that make its operation possible. It also looks into their problematic areas and proposes possible solutions to those problems.

To overcome some of the difficulties that come with the FG-MOSFET current research is looking into a number of alternatives, each one of which has both benefits and weaknesses. One of the most prominent candidates to replace the floating-gate transistor in the future is the nanocrystal memory cell. The idea is that the floating-gate layer within the dielectric of the transistor is replaced with nanoparticles of a semiconducting material (such as silicon, germanium or, in our case, gallium nitride). The advantages of such a structure over the simple floating-gate device are many, the most important of which is, maybe, that it is not limited by the thickness of the

interpoly dielectric. Nanoparticle memory cells was first proposed by Tiwari in 1996; since then significant progress has been made and recent tests to evaluate their effectiveness have produced very promising results. Nanocrystals (or quantum dots) are briefly discussed in order to gain a perspective of their properties, after an analysis of the operation of a nanoparticle memory cell, as it is understood, is given. Lastly, we argue about the reasons that might make gallium nitride a suitable material for the nanocrystals in memory applications.

#### 2.1 THE MOS CAPACITOR AND THE MOSFET

#### 2.1.1 Electronics of the Metal-Oxide-Semiconductor System

The Metal-Oxide-Silicon structure takes advantage of the fact that silicon, a semiconductor, turns into a very effective insulator when oxidized. In reality, the MOS system is a simpler, yet still more specific case of the Metal-Insulator-Oxide system, which means that any appropriate insulator can be used in place of the silicon dioxide with similar effects.

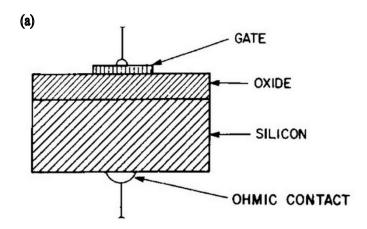

The device is presented in figure 2.1-1a. We assume acceptor-doped silicon throughout this paragraph for our analysis, but mention is given to the n-type silicon substrate when it is deemed necessary. On top of the silicon lies a layer of silicon dioxide (SiO<sub>2</sub>) of thickness t<sub>ox</sub>. The metal, usually aluminium, also called the *gate*, provides an electrode at which the voltage can be fixed. It should be noted here, that a lot of the times, especially in recent devices, polysilicon is used instead of the metal without this affecting the operation of the device. The resulting structure is basically a simple capacitor with its top electrode on the metal-oxide interface, its bottom electrode somewhere in the bulk silicon and a dielectric in between. The energy band diagram of this system in equilibrium is given in figure 2.1-1b.  $X_{Si}$  and  $X_{ox}$  are the electron affinities of the silicon and the oxide accordingly and  $\Phi_M$  is the metal work function. The metal and the semiconductor form then two plates of a charged capacitor and this capacitor is charged to a voltage that corresponds to the difference between the metal and the silicon work function. However, it should be noted that frequently, especially in practical applications this difference is ideally considered to be zero.

#### **Flat-Band Condition**

Now let us consider the case when a bias voltage is applied between the gate and the silicon, and let us also assume that the applied voltage is set to a value that exactly compensates the difference in the work functions of the metal and the semiconductor:

$$V_{FB} = \Phi_M - \Phi_S$$

.

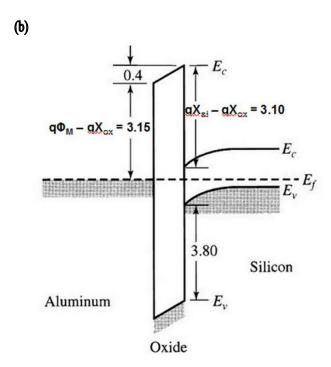

This voltage is called *flat-band voltage* and the MOS system is then said to be in *flat-band condition*, which as it has been mentioned is sometimes ideally considered to occur at 0V. The name flat-band means that the band diagram of the system is then 'flattened' (fig. 2.1-2).

#### **Accumulation**

Subsequently, if the silicon is held at ground and the voltage applied to the metal is kept negative but increased in magnitude, holes will begin to accumulate on the oxide-semiconductor interface so that the surface will eventually have a greater density of holes than the acceptor density. This condition is called *accumulation* and the region at the surface containing the increased hole population is known as the *accumulation layer*.

#### **Depletion**

In the case that a positive voltage is applied between the metal and the silicon negative charge will be stored at the silicon surface and positive on the metal. What this means is that holes will be drawn by the field away from the semiconductor-metal interface leaving positively charged acceptors close to the surface. The area where holes have left their acceptors exposed is called *depletion region* or *depletion layer*

and the system is said to be in conditions of *surface depletion*. The width of the depletion layer is  $x_d$  and  $Q_d$  is the total charge of the depletion layer:

$$Q_d = -qN_a x_d,$$

where  $N_a$  is the acceptor density of the silicon substrate, and q the electron charge in coulombs. The width of the depletion layer  $x_d$  increases as we move to higher voltages.

Figure 2.1-1: (a) Structure of the MOS Capacitor. (b) Band diagram of the MOS capacitor in equilibrium.

# **Inversion**

If the voltage applied to the metal is increased further, the field at the surface of the silicon will also increase and generation of carriers will eventually exceed recombination where majority carriers have been depleted. Then the width of the depletion region will have reached a maximum which can be found to be equal to:

$$x_{d \max} = \sqrt{\frac{4\varepsilon_S |\phi_p|}{qN_a}}, \quad \text{where } \phi_p = \frac{E_i - E_f}{q}.$$

$E_f$  is the Fermi level in the bulk of the semiconductor,  $E_i$  is the intrinsic Fermi level, and  $\varepsilon_S$  is the dielectric constant of the semiconductor.

The electron-hole pairs generated are separated by the field, the holes being swept into the bulk and the electrons moving to the oxide-silicon interface to form the *inversion layer*, so called because the surface contains more electrons than holes even though the silicon is doped with acceptor impurities. The inversion layer is the channel used in MOS Field Effect transistor to conduct current between the source and the drain of the transistor. The voltage at which the inversion layer occurs is sometimes called *threshold voltage* ( $V_{th}$  or  $V_{T}$ ) and will be discussed in more detail in a following paragraph. As soon as the inversion layer is formed, the system is said to go into *inversion*. The inversion layer comprises then of negative charge ( $Q_{n}$ ) which adds to the total charge on the semiconductor surface so that the total charge is the sum of the negative charges of the depletion and the inversion layers:  $Q = Q_d + Q_n$ .

Figure 2.1-2: Band diagrams and charge distributions for the MOS capacitor.

The band diagrams for all of the above cases, as well as the charge densities, are collectively presented in figure 2.1-2. The above discussion can easily be made for a donor-doped silicon substrate, if we keep in mind that in that case, the electrons will be the majority carriers and the holes the minority carriers; then, the charges discussed change their sign. Additionally, a MOS capacitor on n-type silicon, will move from

accumulation to inversion as the gate voltage becomes more and more *negative* instead of more positive, as was the case for p-type silicon.

# 2.1.2 MOS Capacitance

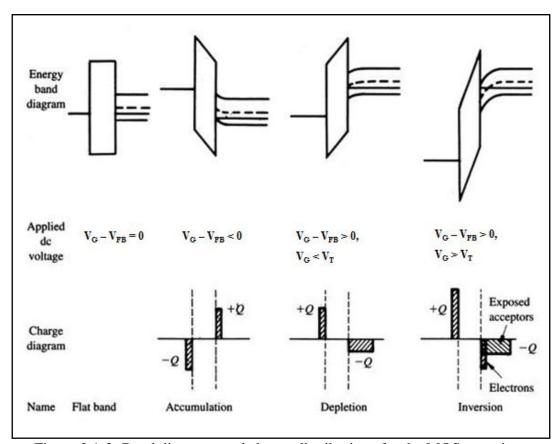

As it has been already stated, the MOS system is, in fact, a capacitor. What makes it so important is that its capacitance does not remain constant; it rather depends on the voltage bias that is applied at the gate. To study how the bias voltage affects the capacitance of the system, we assume a dc signal applied to the gate, and a small ac voltage superposed on that dc bias, which will help measure the system impedance.

Let us first consider that the MOS system described in the previous paragraph is biased with a steady voltage that causes the silicon surface to be accumulated (for a ptype silicon sample, it has been pointed out this corresponds to a negative applied voltage). The excess holes at the surface are pulled very close to the oxide, and therefore the capacitance measured will be that of the oxide itself:

$$C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}},$$

where  $\epsilon_{ox}$  is the oxide dielectric constant,  $t_{ox}$  the oxide thickness, and C is capacitance per unit area.

As the surface area becomes less accumulated, and the system approaches flatband conditions, the capacitance will start to decrease. When the gate bias finally reaches the flat-band voltage the capacitance has be found to be given by the following expression:

$$C_{FB} = \frac{1}{1/C_{ox} + L_D/\varepsilon_s},$$

where  $L_D = \sqrt{\frac{\varepsilon_s kT}{q^2 N_a}}$  is the Debye length, T the temperature in K and k the Boltzmann constant.

Figure 2.1-3: General behaviour of C-V curves of an ideal MOS system under different dc bias and ac small signal conditions.

When the gate voltage becomes more positive than the flat-band voltage, holes are repelled from the surface of the silicon and the system is in depletion. Under this condition, relatively straightforward electrostatic analysis shows that the overall capacitance C corresponds to the capacitance obtained by a series connection of the oxide capacitance and the capacitance  $C_s$  across the surface depletion region:

$$C_{depletion} = \frac{1}{1/C_{ox} + 1/C_s} = \frac{1}{1/C_{ox} + x_d/\varepsilon_s},$$

where  $x_d$  is the width of the surface depletion layer, which depends upon gate bias as well as the doping and oxide properties. From the above equation it is obvious that the capacitance of the system decreases as the depletion region widens.

When the gate bias is increased sufficiently to invert the surface, a new feature must be considered to describe the MOS capacitance behaviour. The inversion layer at the MOS surface results from the generation of minority carriers; hence, the population of the inversion layer can change only as fast as carriers can be generated within the depletion region near the surface. This limitation causes the measured capacitance to be a function of the frequency of the ac signal used to measure the small-signal capacitance of the system (fig. 2.1-3).

The simplest case arises when both the dc gate-bias voltage and the small-signal measuring voltage are changed very slowly so that the silicon can always approach equilibrium. In this case, the signal frequency is low enough so that the inversion-layer population can 'follow' it. The capacitance of the MOS system is just that associated with charge storage on either side of the oxide; its value is approximately  $C_{ox}$ . In this case the C-V characteristic of the system follows the curve that is marked LF (low frequency) in figure 2.1-3: going from  $C_{ox}$  in the accumulation region of bias through a decreasing region as the surface traverses the depletion region and moving back up to  $C_{ox}$  when the surface becomes inverted.

When the ac measuring signal is changed rapidly while the dc bias voltage is varied slowly, the inversion layer cannot respond to the measuring signal. The capacitance then corresponds to the series combination of the oxide capacitance and the depletion-region capacitance, as was true under depletion bias. Since the depletion region reaches a maximum width  $x_{dmax}$  when the system goes into strong inversion, the measured capacitance approaches a value corresponding to the series connection of the oxide capacitance and the capacitance associated with the maximum depletion-region width. It remains constant at this value as the bias voltage is increased further (HF-high frequency curve in figure 2.1-3).

There is a final capacitance behaviour called *deep depletion* (DD on the C-V characteristic of figure 2.1-3). It corresponds to the experimental situation in which both the gate bias voltage  $V_G$  and the small-signal measuring voltage vary at a faster rate than can be accommodated by generation in the surface depletion-region. Since the inversion layer cannot form, the depletion region becomes wider than  $x_{dmax}$ . The capacitance in this mode is given by the series combination of the oxide capacitance and the capacitance of the depletion region, only in this case  $x_d > x_{dmax}$  and C does not reach a minimum.

The equivalent circuits for all of the above cases are presented in figure 2.1-4.

Figure 2.1-4: Equivalent circuits for the overall capacitance of the MOS System under different bias conditions.

The Effect of the oxide and interface charge on the Flat-Band Voltage: So far we have tried to describe the behaviour of the MOS system which essentially depends on how the charge is distributed in the silicon and metal interface and how that distribution is affected by applying a voltage bias on the metal. We have considered the ideal case when no charge can exist within the oxide. However, very frequently and despite any efforts to eliminate it, several kinds of charges sometimes present themselves in the bulk of the dielectric or the surface and one has to consider their effect on the system behaviour, especially when one is interested in the MOS system as a platform for charge storage, as is the case for non-volatile memories.

Figure 2.1-5: (a) Four categories of oxide charge in the MOS system (b) Charge density distribution in an oxide layer.

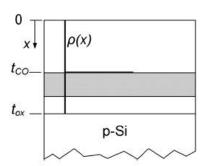

Oxide charge is the result of defects in the dielectric, it generally depends on how effective the process of the forming of the layer is performed and it usually is categorized in four groups (fig. 2.1-5a):  $Q_f$  the fixed interface charge density,  $Q_{ot}$  the oxide trapped-charge density,  $Q_{it}$  the interface trapped-charge density, and  $Q_m$  the mobile charge density.

The oxide charge causes the C-V curves of the MOS system to distort. The exact analysis is fairly complicated and different for each kind of charge. For example, fixed oxide charge causes the C-V characteristic to shift along the voltage sweep. In this paragraph, we only make a brief mention of how the oxide charge affects the flatband voltage because it will prove useful for the analysis that follows in the next chapters; should one wish so, one can look into the related literature.

We have mentioned above that the flat-band voltage where there is no oxide charge is given by the expression:

$$V_{FB} = \Phi_M - \Phi_S = \Phi_{MS}.$$

When we take into consideration the effect of oxide charges, the above equation can be found to take the form:

$$V_{FB} = \Phi_{MS} - \frac{Q_f}{C_{ox}} - \gamma \frac{Q_m}{C_{ox}} - \gamma \frac{Q_{ot}}{C_{ox}} - \frac{Q_{it}}{C_{ox}}, \text{ where:}$$

$$\gamma = \frac{\int_0^{t_{ox}} \frac{x}{t_{ox}} \rho(x) dx}{\int_0^{t_{ox}} \rho(x) dx}.$$

$\rho(x)$  is the charge density distribution through the oxide layer (fig. 2.1-5b), and  $Q = \frac{1}{t_{ox}} \int_{0}^{t_{ox}} x \rho(x) dx$ .

If now we consider only the trapped charge in the oxide, with a random distribution  $\rho$ , then, we get:

$$V_{FB} = \Phi_{MS} - \gamma \frac{Q_{ot}}{C_{out}},$$

and this results in a shift in the C-V characteristic, as well as in the flat-band voltage. This will be again discussed in the following paragraphs.

# 2.1.3 The MOS Field Effect Transistor and The Threshold Voltage

This paragraph briefly describes the operation of the MOS Field Effect Transistor. It does not attempt a lengthy analysis, nor does it contain a full mathematical description as such a thing would stray from the purpose of the present study; it rather focuses on a few characteristics of the device that will be useful for future reference.

The basic structure of an n-channel MOSFET is shown in figure 2.1-6a. It consists of the MOS structure of the previous paragraphs, with a surface inversion layer or *channel* extending between two diffused junctions. These two junctions are electrically disconnected unless there in an n-type inversion layer at the surface to provide a conduction channel between them. When the surface is inverted and a voltage is applied between the junctions, electrons can enter the channel at one junction, called the *source*, and leave at the other, called the *drain*. The density of free

charge in the channel is controlled by a field that extends from the gate electrode to the silicon through the insulating layer.

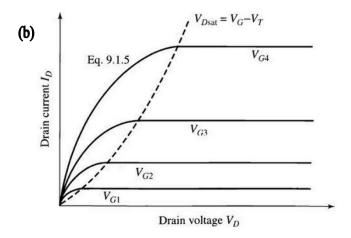

The characteristics of the device are presented in figure 2.1-6b. When a positive voltage  $V_{\rm G}$  is applied to the gate relative to the substrate, mobile negative charges (electrons) gets attracted to Si-oxide interface. These induced electrons form the channel. For a given value of  $V_{\rm G}$ , the current  $I_{\rm D}$  increases with  $V_{\rm D}$ , and finally saturates.

The reason it is called an 'n-channel' MOSFET is because the inversion layer (or the channel) consists of electrons. The same principles apply for a p-MOSFET, developed on n-type silicon, with a channel that consists of holes.

Figure 2.1-6: (a) Schematic representation of the n-channel MOSFET. (b) Typical I-V characteristics of a MOSFET device.  $V_{G4} > V_{G3} > V_{G2} > V_{G1}$ .

In order for the channel to form, however, and for current to be able to flow, the gate voltage must be higher than the *threshold voltage*  $V_T$  (or  $V_{th}$ ) of the device, as we have mentioned before. A full electronic analysis yields the threshold voltage to equal:

$$V_{T} = V_{FB} + V_{C} + 2 \left| \phi_{p} \right| + \frac{1}{C_{ox}} \sqrt{2\varepsilon_{S} q N_{a} \left( 2 \left| \phi_{p} \right| + V_{C} + V_{B} \right)}.$$

$V_{FB}$  is the flat-band voltage of the MOS system,  $V_{C}$  is the voltage applied to the transistor source, and  $V_{B}$  the voltage applied to the body (substrate).

#### 2.2 PHYSICS OF THE FG-MOSFET

#### 2.2.1 Charge Storage

The best place to begin to understand the physics of the FG-MOSFET is to consider the energy levels involved. Figure 2.2-1b shows the band structure for a simple floating gate device (fig. 2.2-1a) where the silicon substrate is shown on the left. This band diagram might depict a two-terminal single memory cell (like to the MOS capacitor) or can be part of a more complex device with three or more terminals. The n-type control gate is shown instead of a metal on the right, and an n-type polysilicon floating gate is in the middle, sandwiched between two silicon dioxide layers. The floating gate, embedded within insulators, is isolated from the exit or entry of charge by the high-energy barrier between the conduction band in the polysilicon and the conduction bands in the top and bottom SiO<sub>2</sub> layers. These barriers, much greater than the thermal energy, provide non-volatile retention of the charge. In order to change the amount of charge stored on the floating gate it is necessary to change the potential of the floating gate relative to the potential on the opposite side of either SiO<sub>2</sub> layer until some conduction mechanism is invoked that can overcome or tunnel through the barrier.

Figure 2.2-1: (a) The FG-MOSFET. (b) Energy band diagram for a typical floating-gate structure.

Different strategies may be selected to overcome the energy barriers. Two conduction mechanisms in common use are channel hot-electron injection (CHEI) and

Fowler-Nordheim (FN) tunnelling. Hot-carrier injection may be used to add electrons to a floating gate (i.e. programming). FN tunnelling may be used to remove or add electrons to a floating gate (i.e. erase or program). Other mechanisms (enhanced tunnelling, substrate hot electron injection, etc.) can be used but, since they are not as common, we will not be concerned with such procedures.

Figure 2.2-2: (a) Energy band representation of Fowler-Nordheim tunnelling through thin oxides; electrons in the silicon conduction band tunnel through the triangular energy barrier. (b) Energy band representation of channel hot-electron injection (CHEI) in an n-channel MOS transistor.

**Fowler-Nordheim Tunnelling**: FN tunnelling is in fact a field-assisted electron tunnelling mechanism. When a large voltage is applied across a polysilicon- $SiO_2$ -silicon structure, its band structure has a shape as indicated in figure 2.2-2a. Due to the high electric field, the electrons in the silicon conduction band see a triangular energy barrier of which the width is dependent on the applied field. The height of the barrier is determined by the electrode material and the band structure of  $SiO_2$ .

At sufficiently high fields, the width of the barrier becomes sufficiently small for electron to tunnel through the barrier from the silicon conduction band into the oxide into the oxide conduction band. A simple expression for the FN current is given:

$J = \alpha E_{inj}^2 \exp\left(\frac{-E_c}{E_{inj}}\right)$

with:

$$\alpha = \frac{q^3}{8\pi h \phi_b} \frac{m}{m^*}$$

$$E_c = \frac{4\sqrt{2m^*}\phi_b^{3/2}}{3\eta q}$$

where h is Planck's constant,  $\phi_b$  is the energy barrier at the injecting interface (3.2eV for Si-SiO<sub>2</sub>),  $E_{inj}$  is the electric field at the injecting interface, q the charge of a single electron, m the free electron mass, m\* the effective ass of an electron on the bandgap of SiO<sub>2</sub> and  $\eta$ =h/2 $\pi$ .

More accurate expressions for the FN current density have been expressed and are available in literature, but in general, the current shows an exponential dependence on the applied field.

FN tunnelling is very common in non-volatile memories for programming and erasing. It provides low currents and, hence, low power operation. It has also shown good endurance and current controllability for the devices that employ it. It has, however, some disadvantages such as the large voltages it requires for tunnelling and the demand for good quality of the tunnel oxide.