Computer Science Department University of Crete

## Design and Implementation of a Coherent Memory Sub-System for Shared Memory Multiprocessors

Master's Thesis

Evaggelos Vlachos

July 2006 Heraklion, Greece

Πανεπιστήμιο Κρήτης Σχολή Θετικών και Τεχνολογικών Επιστημών Τμήμα Επιστήμης Υπολογιστών

## Design and Implementation of a Coherent Memory Sub-System for Shared Memory Multiprocessors

Εργασία που υποβλήθηκε από τον Βλάχο Ευάγγελο ως μερική εκπλήρωση των απαιτήσεων για την απόκτηση Μεταπτυχιακού Διπλώματος Ειδίκευσης

Συγγραφέας:

Ευάγγελος Βλάχος, Τμήμα Επιστήμης Υπολογιστών

Εισηγητική Επιτροπή:

Μανόλης Κατεβαίνης, Καθηγητής, Επόπτης

Άγγελος Μπίλας, Αναπληρωτής Καθηγητής, Μέλος

Διονύσης Πνευματικάτος, Αναπληρωτής Καθηγητής, Μέλος Τμήμα Ηλεκτρονικών Μηχανικών & Μηχανικών Υπολογιστών, Πολυτεχνείο Κρήτης

Δεκτή:

Δημήτρης Πλεξουσάκης, Αναπληρωτής Καθηγητής Πρόεδρος Επιτροπής Μεταπτυχιακών Σπουδών

Ηράκλειο, Ιούλιος 2006

## Design and Implementation of a Coherent Memory Sub-System for Shared Memory Multiprocessors

by

**Evaggelos Vlachos**

Master's Thesis

Department of Computer Science University of Crete

#### Abstract

Recent technology advances in integrated electronics offer the ability to add more and more transistors into modern chips. Chip Multiprocessors (CMPs) are architectures that feature multiple processing cores on a single chip. They result in higher processing power, easier design scalability, and greater performance/power ratio. CMPs appear to be one of the dominating architectural approaches for the years to come in the area of high performance architectures.

The purpose of this work is to design and implement a shared memory multi-core system that matches the needs of future CMPs. Specifically, an FPGA-based prototype has been implemented, which constitutes a two-node processing system. The design takes advantage of the two PowerPC cores that are embedded in the FPGA fabric. We have implemented external coherent caches equipped with a MESI protocol, and a bus-based coherent memory interconnect to connect the two processors. Shared memory resides in external DDR memory accessible through the interconnect and the DDR controller.

We find that the area overhead of our coherent memory system is 33.4% of a medium-size FPGA. We evaluate the performance of the system by using both simulations and custom software benchmarks running on the two processors. Our simulations show that the system implemented is more efficient than systems based exclusively by Xilinx soft-cores that offer the same type of memory coherence. Our custom benchmarks simulate basic operations found commonly in parallel programs. Our results show that our design scales well with respect to a single processor, for the Merge-Sort algorithm and the Producer-Consumer benchmark that don't require a great amount of synchronization traffic. The speedup measured ranges between 1.89 to 1.92 and 1.89 to 3.45, respectively. On the other hand, the Shared-Counter benchmark slows down by 3 to 10 times due to excessive synchronization traffic.

Thesis Supervisor: Manolis Katevenis, Professor

## Σχεδίαση και Υλοποίηση ενός Υποσυστήματος Μνήμης Συνοχής Δεδομένων για Πολυεπεξεργαστές Διαμοιραζόμενης Μνήμης

Βλάχος Ευάγγελος

Μεταπτυχιακή Εργασία

Τμήμα Επιστήμης Υπολογιστών Πανεπιστήμιο Κρήτης

### Περίληψη

Πρόσφατα τεχνολογικά επιτεύγματα στον τομέα των ολοκληρωμένων κυκλωμάτων προσφέρουν την δυνατότητα πρόσθεσης περισσοτέρων τρανζίστορ στα σημερινά ολοκληρωμένα κυκλώματα. Τα «Ολοκληρωμένα Πολυεπεξεργαστικών Συστημάτων» αποτελούν αρχιτεκτονικές οι οποίες διαθέτουν πολλαπλούς πυρήνες επεξεργασίας στο ίδιο ολοκληρωμένο. Αυτό έχει σαν αποτέλεσμα την αύξηση επεξεργαστικής ισχύς, την ευκολότερη κλιμάκωση της σχεδίασης και την αύξηση του λόγου απόδοσης ανά μονάδα κατανάλωσης. Αυτό το είδος σχεδίασης αναμένεται να επικρατήσει στο μέλλον στον τομέα της αρχιτεκτονικής υπολογιστών.

Ο σχοπός αυτή της εργασίας είναι η σχεδίαση χαι υλοποίηση ενός συστήματος πολλαπλών πυρήνων διαμοιραζόμενης μνήμης, το οποίο προσεγγίζει τις ιδιότητες ενός μελλοντιχού πολυεπεξεργαστιχού συστήματος. Πρωτότυπο του συστήματος αυτού υλοποιήθηχε σε μια FPGA χαι αποτελεί ένα σύστημα με δυο επεξεργαστιχούς πυρήνες. Το σύστημα αξιοποιεί τους δύο ενσωματωμένους επεξεργαστές PowerPC, οι οποίοι χαι αποτελούν μέρος του όλου συστήματος. Υλοποιήσαμε εξωτεριχές χρυφές μνήμες εφοδιασμένες με πρωτόχολλο συνοχής διαμοιραζόμενης μνήμης χαι ένα δίχτυο τύπου αρτηρίας για να συνδέσουμε τους δύο επεξεργαστές. Η διαμοιραζόμενη μνήμη βρίσχεται στην εξωτεριχή DDR μνήμη χαι είναι προσπελάσιμη μέσω του υπο-συστήματος μνήμης.

Το επιπρόσθετο κόστος σε εμβαδόν που εισάγεται από το σύστημά μας είναι 33,4% σε μια FPGA μεσαίου μεγέθους. Αποτιμήσαμε την επίδοση του συστήματός μας χρησιμοποιώντας προσομοιώσεις και δοκιμαστικά προγράμματα που τρέχουν και στους δύο επεξεργαστές. Οι προσομοιώσεις μας έδειξαν ότι το σύστημα που υλοποιήθηκε είναι πιο αποδοτικό από κάθε άλλο που προσφέρει συνεπή διαμοιραζόμενη μνήμη και βασίζεται αποκλειστικά σε κομμάτια από την βιβλιοθήκη της Xilinx. Τα δοκιμαστικά προγράμματα που χρησιμοποιούμε προσομοιώνουν βασικές λειτουργίες που εμφανίζονται συχνά σε παράλληλα προγράμματα. Τα αποτελέσματα δείχνουν ότι η απόδοση του σύστημά μας κλιμακώνεται ομαλά σε σχέση με τον ένα επεξεργαστή, για τον αλγόριθμο ταξινόμησης και το πρόγραμμα Παραγωγού-Καταναλωτή, τα οποία δεν δημιουργούν μεγάλες ποσότητες κίνησης συγχρονισμού. Η επιτάχυνση που μετρήθηκε κυμαίνεται από 1,89 έως 1,92 και από 1,89 έως 3,45, αντίστοιχα. Αντιθέτως, το πρόγραμμα του διαμοιραζόμενου μετρητή επιβραδύνθηκε από 3 έως 10 φορές λόγω υπερβολικής κίνησης συγχρονισμού.

Επόπτης Μεταπτυχιαχής Εργασίας: Μανόλης Κατεβαίνης, Καθηγητής

#### Acknowledgments

First of all I would like to thank my family (Kostas, Marditsa, Apostolis and Anda) for their love and support they have offered all these years. They have sacrificed everything in order to help me reach my goals. Without their help I would certainly have not made it to here.

I would also like to thank my advisor Prof. Manolis Katevenis as also Prof. Angelos Bilas and Prof. Dionysios Pnevmatikatos, for their guidance and their support throughout this work. Their constructive remarks and the time they devoted to me constitute a significant amount of help.

Finally, I would like to thank all my fellow students and/or co-workers at FORTH for their help and their support in all the good and bad times. Working in the same environment with you my friends has been a pleasant and an honor.

(Dr. Manolis Marazakis, Vasilis Papaefstathiou, George Kalokairinos, Mixalis Ligerakis, Stamatis Kavadias, Mixalis Papamicheal, George Mihelogiannakis, Aggelos Ioannou, Nikos Andrikos, George Passas, Kostas Kapelonis, Evriklis Kounalakis, George Panagiotakis, Dimitris Antoniadis, Manolis Athanatos and many other....)

This work was carried out with the financial and technical support from FORTH - ICS and in the framework of the European FP6-IST program through the SIVSS (STREP 002075), UNISIX (MC EXT 509595), SARC(FET 027648) projects, and the HiPEAC Network of Excellence (NoE 004408).

To my family

# Contents

| 1 | Intro | oduction                                                 | 1  |

|---|-------|----------------------------------------------------------|----|

|   | 1.1   | Background                                               | 2  |

|   |       | 1.1.1 Shared Memory Multirocessors                       | 3  |

|   |       | 1.1.2 Chip Multiprocessors                               | 9  |

|   | 1.2   | Releated Work                                            | 11 |

| 2 | Desi  | gn and Implementation                                    | 13 |

|   | 2.1   | General Description                                      | 13 |

|   | 2.2   | PowerPC 405                                              | 15 |

|   | 2.3   | PLB Bus Interconnect                                     | 17 |

|   | 2.4   | PLB BRAM Controller, BRAM blocks and PLB2IPIF Controller | 18 |

|   | 2.5   | PLB2Cache module                                         | 18 |

|   |       | 2.5.1 PLB2Cache Module Architecture                      | 20 |

|   | 2.6   | Coherent Cache                                           | 21 |

|   |       | 2.6.1 Cache Characteristics                              | 22 |

|   |       | 2.6.2 Tags and Data Memory Organization                  | 23 |

|   |       | 2.6.3 Coherency Protocol                                 | 24 |

|   |       | 2.6.4 Part A: Cache's Processor side                     | 26 |

|   |       | 2.6.5 Part B: Cache's Bus side                           | 31 |

|   | 2.7   | Coherent Memory Interconnect                             | 34 |

|   | 2.8   | DDR Multiplexer                                          | 39 |

|   | 2.9   | DDR Controller                                           | 40 |

| 3  | Eval        | uation and Verification                                          | 41 |

|----|-------------|------------------------------------------------------------------|----|

|    | 3.1         | Hardware Resources                                               | 41 |

|    |             | 3.1.1 Target FPGA                                                | 41 |

|    |             | 3.1.2 Hardware Resources                                         | 42 |

|    |             | 3.1.3 Timing Conciderations                                      | 43 |

|    | 3.2         | Performance Evaluation                                           | 45 |

|    |             | 3.2.1 Comparison with other Coherent Shared Memory Organizations | 51 |

|    | 3.3         | Correctness verification                                         | 52 |

|    |             | 3.3.1 Software primitives                                        | 52 |

|    |             | 3.3.2 Shared Memory Programs                                     | 53 |

| 4  | Con         | clusion and Future Work                                          | 65 |

| Re | eferen      | ces                                                              | 66 |

| A  | DSP         | LB & PLB2Cache module                                            | 71 |

|    | A.1         | DSPLB Behavior                                                   | 71 |

|    | A.2         | DSPLB Signal Summary                                             | 73 |

|    | A.3         | PLB2Cache module FSMs                                            | 75 |

|    | A.4         | Returning Data                                                   | 77 |

| B  | Deta        | ils about the Coherent Cache                                     | 79 |

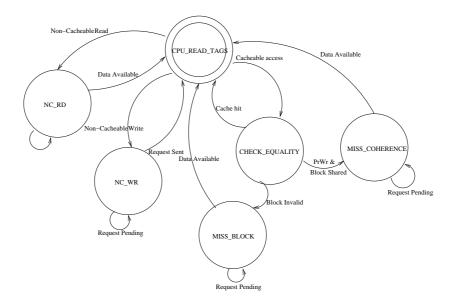

|    | <b>B</b> .1 | Part A FSMs                                                      | 79 |

|    |             | B.1.1 FSM_CPU_ACCESS                                             | 79 |

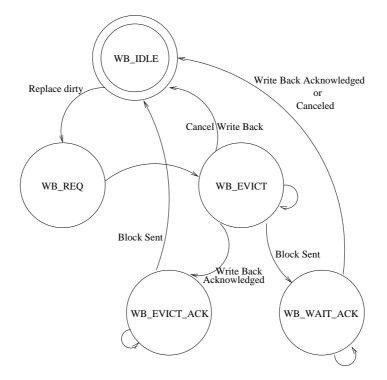

|    |             | B.1.2 WB_FSM                                                     | 80 |

|    | B.2         | Completing Requests and Cache Status                             | 83 |

|    | B.3         | Part B FSMs                                                      | 84 |

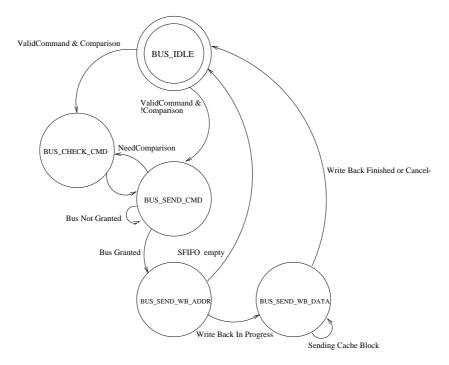

|    |             | B.3.1 BUS_FSM                                                    | 84 |

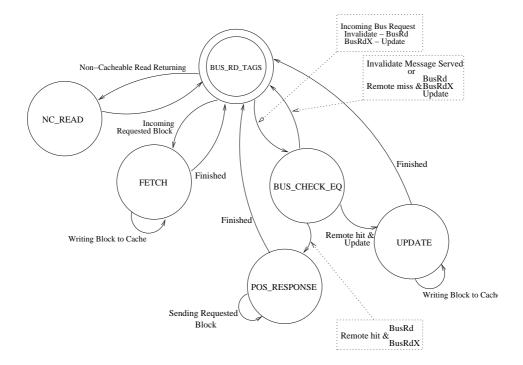

|    |             | B.3.2 FSM_REQ_IN                                                 | 86 |

|    | B.4         | Communication with the dependency check module                   | 88 |

| С  | Coh         | erent Bus Module FSMs                                            | 89 |

|    | C.1         | FSM_Arb                                                          | 89 |

|   | C.2  | FSM_BUS_WB                                 | 91 |

|---|------|--------------------------------------------|----|

| D | Deta | iled Reports                               | 93 |

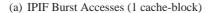

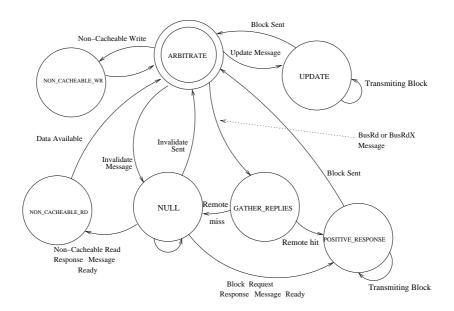

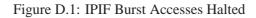

|   | D.1  | Waveforms for Halted IPIF Burst Accesses   | 93 |

|   | D.2  | Detailed Timing Reports for Critical Paths | 93 |

# **List of Figures**

| 1.1  | The Cache Coherence Problem                                                     | 3  |

|------|---------------------------------------------------------------------------------|----|

| 1.2  | State diagram for the MSI write-invalidate cache coherece protocol              | 7  |

| 1.3  | State diagram for the write-update cache coherece protocol                      | 9  |

| 2.1  | Architecture of the System                                                      | 14 |

| 2.2  | PowerPC 405 Organization                                                        | 16 |

| 2.3  | 3-cycle PLB Arbitration                                                         | 17 |

| 2.4  | Connection between the PowerPC, the PLB2Cache module, and the Bus               | 19 |

| 2.5  | PLB2Cache Architecture                                                          | 20 |

| 2.6  | Coherent Cache General Description                                              | 22 |

| 2.7  | Coherency Protocol State Diagram                                                | 24 |

| 2.8  | Part A block diagram                                                            | 27 |

| 2.9  | Two First Cycles of a Processor Access                                          | 28 |

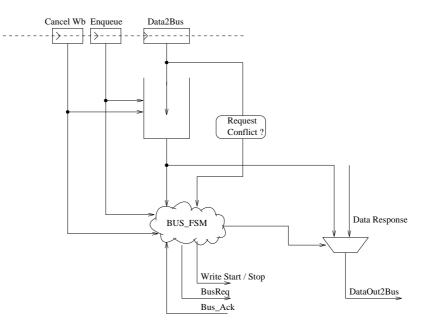

| 2.10 | Cache2Bus Block Diagram                                                         | 32 |

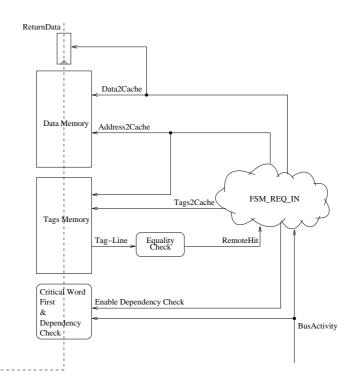

| 2.11 | Bus2Cache Block Diagram                                                         | 34 |

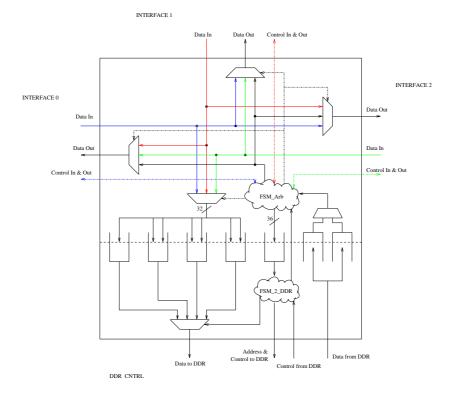

| 2.12 | Coherent Memory Interconnect Block Diagram                                      | 35 |

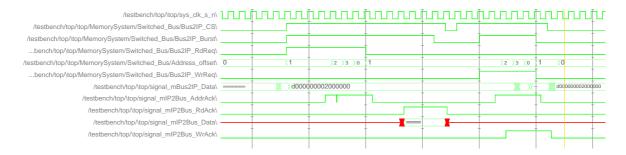

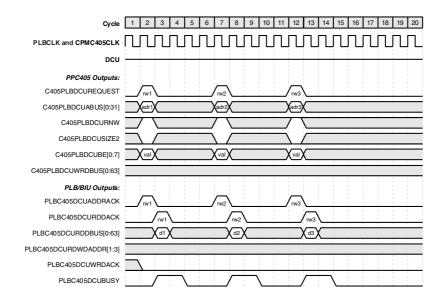

| 2.13 | IPIF Accesses                                                                   | 38 |

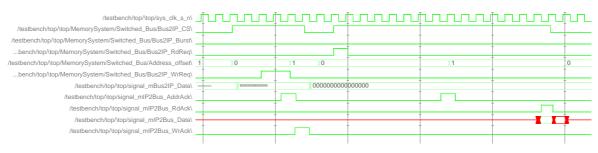

| 3.1  | Floorplanned view of the system                                                 | 42 |

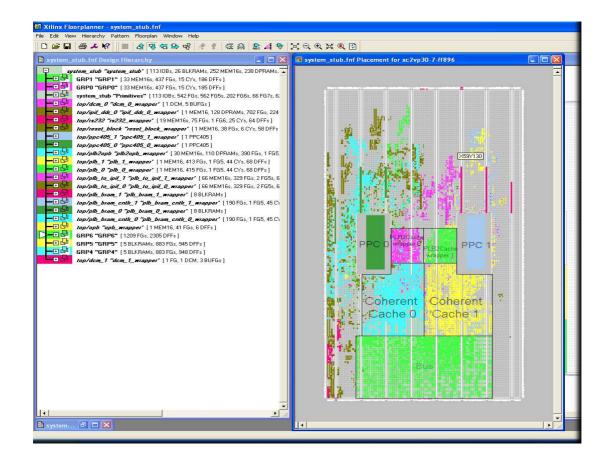

| 3.2  | Write hit and Read hit Scenarios                                                | 46 |

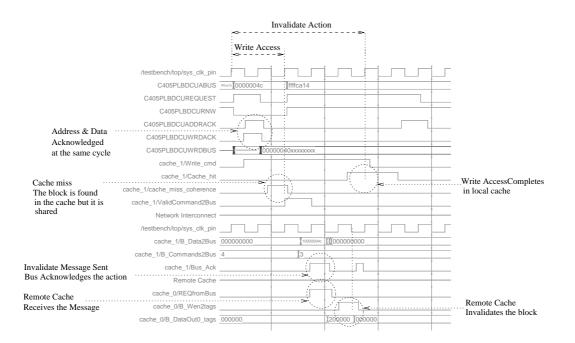

| 3.3  | Invalidate Scenario                                                             | 47 |

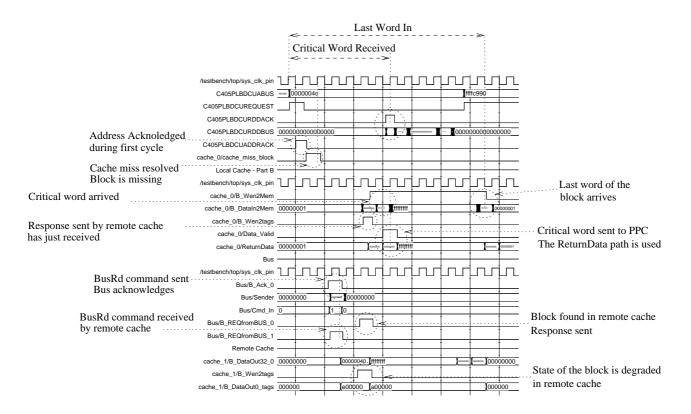

| 3.4  | BusRd Remote Cache hit Scenario                                                 | 48 |

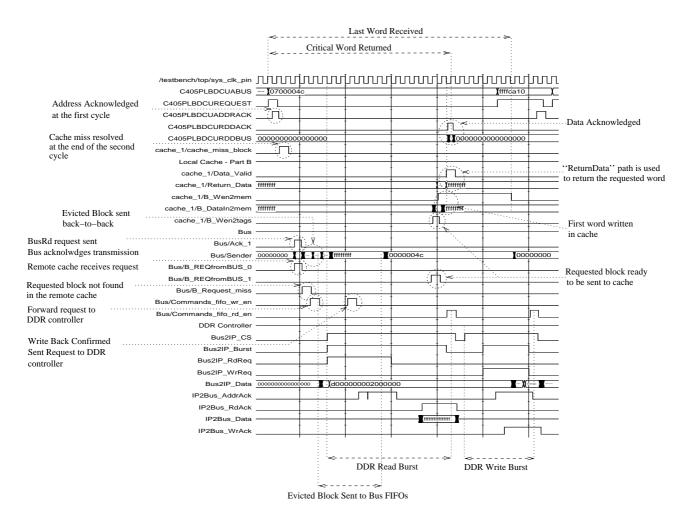

| 3.5  | BusRd Remote miss. Fetching cache block from external memory. Block eviction at |    |

|      | the same time                                                                   | 49 |

| 3.6  | Non-Cacheable Write & Read Accesses                                             | 50 |

| 3.7         | Locking Algorithms                    | 54 |

|-------------|---------------------------------------|----|

| 3.8         | Competing for Access to Shared Memory | 58 |

| 3.9         | Producer - Consumer Program           | 59 |

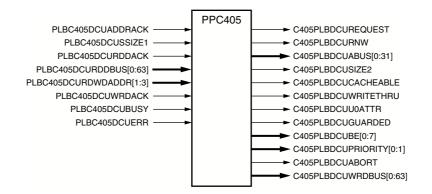

| A.1         | Data-Side PLB Interface Block Symbol  | 73 |

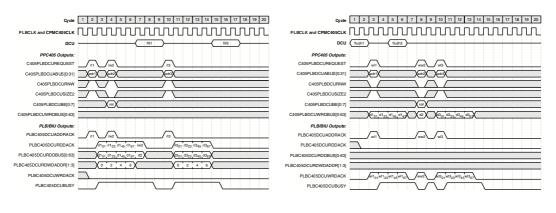

| A.2         | PLB Accesses                          | 74 |

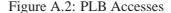

| A.3         | PLB2Cache module FSMs                 | 76 |

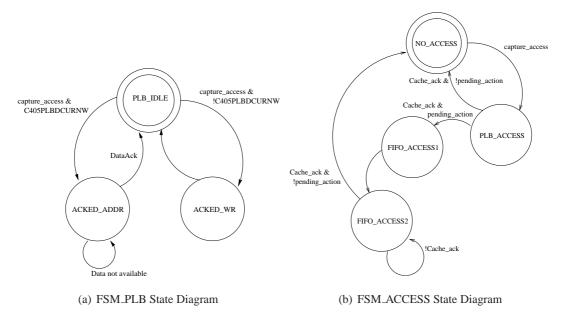

| A.4         | DSPLB Three Consecutive Word Reads    | 78 |

| <b>B</b> .1 | FSM_CPU_ACCESS State Diagram          | 80 |

| B.2         | WB_FSM State Diagram                  | 81 |

| B.3         | BUS_FSM State Diagram                 | 85 |

| B.4         | FSM_REQ_IN State Diagram              | 87 |

| C.1         | FSM_Arb State Diagram                 | 90 |

| D.1         | IPIF Burst Accesses Halted            | 93 |

# **List of Tables**

| 2.1 | Generation of Coherent Requests                                                     | 25 |

|-----|-------------------------------------------------------------------------------------|----|

| 2.2 | Combinations of Accesses                                                            | 29 |

| 3.1 | Virtex II Pro Resource Summary                                                      | 41 |

| 3.2 | Hardware Utilization                                                                | 43 |

| 3.3 | Delay of Critical Paths                                                             | 44 |

| 3.4 | Access Latency (measured in PLB cycles - 100MHz clock freq.)                        | 51 |

| 3.5 | Additional penalties imposed to Shared Memory Requests (measured in PLB cycles -    |    |

|     | 100MHz clock freq.)                                                                 | 51 |

| 3.6 | System Parameters                                                                   | 54 |

| 3.7 | Duration of "Shared-Counter" program for different arcitectures in processor cycles |    |

|     | (clk. freq. 100 MHz)                                                                | 55 |

| 3.8 | Duration of "Producer-Consumer" in processor cycles (clk. freq. 100 MHz)            | 60 |

| 3.9 | Duration of "Merge-Sort" program in processor cycles (clk. freq. 100 MHz)           | 63 |

| A.1 | DSPLB PLB Interface Signal Summary                                                  | 72 |

| D.1 | Time Consumption at the Read Hit Path                                               | 94 |

| D.2 | Time Consumption at the end of the Read Miss Path                                   | 95 |

| D.3 | Time Consumption when requesting the Bus                                            | 95 |

# Chapter 1

# Introduction

Recent technology advances in integrated electronics offer to computer engineers the ability of adding more and more transistors into modern chips. The logic being added is becoming more and more complex, describing and implementing more powerful designs. This effect has resulted in the occurrence of Chip Multiprocessors (CMPs). This approach suggests that high-performance processor architectures should move towards designs that feature multiple processing cores on a single chip. These designs have the potential to provide higher peak throughput, easier design scalability, and greater performance/power ration than nowadays uniprocessor ones. This trend appears to be one of the dominating architectural approaches for the years to come in the area of high performance architecture. Specifically, there are already some multi-core architectures on the market [1, 2, 3] that dispose a small number of processing cores. In the near future CMPs are expected to have a larger number of processing core. It is following that this area will be dedicated to deploy additional cores [4, 5, 6].

Having so many units on a single chip, it certainly alters the architectural decisions that have been considered safe until now. Processing power no longer constitutes the bottleneck of these designs. The vast amount of transistors available on chip has transferred the bottleneck to the need of making all the processing cores cooperate efficiently. Thus, one of the most important characteristics, on which a great amount of consideration will be focused, will deal with communication issues between the multiple processors, either on-chip or even off-chip. The on-chip communication is usually carried out by on-chip interconnection networks that connect the on-chip processing elements. The off-chip communication is usually the responsibility of a Network Interface, which make feasible the commu-

nication with other multinode systems. However, efficiency in communication has a close relation with the proximity of computation to communication. This tight coupling between computation and communication is usually expressed as customizing the features of Network Interfaces in order to meet particular application domain demands. This, however, influence the design of the interconnect network. Thus, an integrated design of the network interface and the interconnection network will provide the desired features to the whole system.

An approach that offers tight coupling between communication and computation suggests the use of Coherent Network Interfaces (CNI) [7, 8]. According to this approach, the multiple nodes (CPUs) use a coherency protocol to share the available memory. The Network Interface is connected to the memory bus and uses the underlying coherency protocol to transfer data to the memory and/or the cache hierarchies. In this way, low-latency communication is provided, as opposed to the currently long-latency coupling through the I/O bus.

The purpose of this study is to design and implement a system that comes closer to the future architecture that described above. Specifically, an FPGA-based prototype has been implemented, which constitutes a two-node processing system. A Xilinx Virtex-II Pro FPGA has been used to host the whole system. The design takes advantage of the two PowerPC cores that are embedded in the FPGA fabric [9, 10, 11]. External coherent caches and a coherent memory interconnect have been implemented to connect properly the two processors. Shared memory resides in external DDR memory accessible through the interconnect and the Xilinx DDR controller. Each processor is also connected to a PLB bus in order to have access to instructions and private data. Finally, the coherent memory interconnect has been designed to accept also a third participant, which can be a coherent network interface. However, this entity remains a future objective.

The rest of the thesis is organized as follows: Background information and related work are discussed in the rest of this chapter. In Chapter 2 the design and the implementation of the whole system is presented. Experimental results and comments from the evaluation of the system are shown in Chapter 3. Finally, the conclusion of this study and future work directives can be found in Chapter 4.

### 1.1 Background

This section of the chapter presents some background information about Shared Memory Multiprocessors and Chip Multiprocessors. Specifically, the Cache Coherence property will be described in detail, and some Cache Coherence protocols will be presented. Finally, the CMP architectural organization

#### 1.1. BACKGROUND

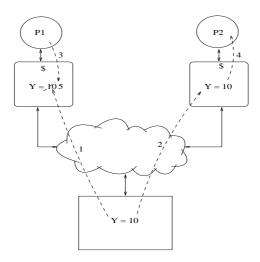

Figure 1.1: The Cache Coherence Problem

will be presented and analyzed.

### 1.1.1 Shared Memory Multirocessors

#### **The Cache Coherence Problem**

Figure 1.1 depicts the problem that arises when multiple processors have access to a shared region of memory. Processors P1 and P2 are connected through an interconnection network to the main memory, while both of them have one private write-back cache. In this example P1 and P2 share variable Y, which both use it in the normal flow of their parallel program. At some point in time processor P1 reads (arc no. 1) variable Y from main memory and places a copy of Y into its cache. Let's say that at that time Y has the value of '10'. Then, processor P2 reads (arc no. 2) variable Y from main memory, placing a copy of Y into its cache, too. The value of Y is still '10' and at that point both processors have an up-to-date copy of Y. The problem arises when processor P1 attempts to modify (arc no. 3) the value of Y. The action of writing to Y the value of '5' updates only the local copy that P1 retains in its cache. However, the copy of Y that P2 has remains intact maintaining an older value of Y. When processor P2 attempts to read Y (arc no. 4), it reads a stale value of that variable. At this point processor P2 has an out-of-date view of the specific memory location, resulting to wrong execution of the parallel program. This is usually referred to as the cache coherence problem.

A naive solution to this problem would be to prevent caching of shared memory by the processors. However, this would have a tremendous negative impact on the performance of the parallel program. Furthermore, in shared memory multiprocessor architectures, reading from and writing to shared memory regions by different processors is expected to happen frequently. This frequent event is used by processes of a parallel program to communicate with each other. This concludes to the fact that addressing shared memory in these architectures must be addressed in different way than convenient uniprocessors do. The answer to this problem is given by hardware techniques that provide coherency among shared data.

#### **Cache Coherence**

In the previous example the problem appeared when the last read operation issued by processor P2 didn't return the up-to-date value of variable Y. This happened because the last write access to this variable was made by processor P1, and P2 was never informed about that. This problem is attributed to the memory interconnect, part of which are also the processors' caches. In [12] a strict definition of cache coherence is given and is apposed below for completeness. According to it,

#### A memory system is coherent if:

- 1. A read by a processor P, to a location X that follows a write by P to X, with no writes of X by another processor occurring between the write and the read by P, always return the value written by P.

- 2. A read by a processor to location X that follows a write by another processor to X returns the written value if the read and write are sufficiently separated and no other writes to X occur between the two accesses.

- 3. Writes to the same location are serialized: that is, two writes to the same location by any two processors are seen in the same order by all processors. For example, if the values 1 and 2 are written to a location, processors can never read the value of the location as 2 and then later read it as 1.

The first property indicates that operations issued by any processor occur in the order which they are issued to the memory system by that processor. That means that the memory system doesn't change the relevant ordering between memory operations from the same processor. The order, which is preserved in this way, is the same order that the memory operations appear in the program, since the processor does not issue memory operations in a way that will violate the program semantics. The second property indicates that the value returned by each read operation is the value written by the last write operation to that location. If that couldn't hold then the whole system wouldn't be able to become in any way coherent. The violation of this rule was presented in the above example. Finally, the third property indicates the serialization of memory operations from all the processors. Every memory operation accesses a physical location at main memory. Since the physical memory module

#### 1.1. BACKGROUND

can serve one request at a time, it would impose a serial order on all the read and write operations from all the processors to any location.

In order to enforce coherency among multiple processors, hardware protocols embedded in the cache hierarchy of each processor manage all the generated accesses [13, 14]. They use the coherent memory interconnect to exchange messages with the other caches to impose synchronization among them. The objectives that they serve are: upon a write request the local cache must ensure that it holds the only copy of the data accessed. Also, all the other caches of the system must be informed about this action and must either invalidate or update their specific copy of the data, if they have one. Upon a read request the local cache must notify all the other caches of the system that a new copy of the data accessed has been generated. In this way a cache that had until now a unique copy is informed that this situation has changed.

#### Hardware Schemes for Enforcing Coherence

An important property of coherency protocols is the way they track the state of each data block accessed by a processor. There are two dominant approaches that have been proposed (found in [15]). The first one, named *Directory based*, suggests that the state of every block is kept in a single location. This location is responsible for administering the specific block of memory, by making it available to other processors in a manner that preserves data coherency. The second approach, named *Snooping based* suggests that no centralized state is kept. On the contrary, every cache that maintains a copy of a block also maintains a copy of the sharing status of the same block. Every time a memory block is requested all the caches must search themselves to see if they hold a copy of this block. If a cache does have a copy, then it follows the steps imposed by the coherency protocol.

Shared memory systems that follow the first approach separates the whole memory to *n* parts, where *n* the number of available processors. Each part is assigned to one processor, which is called the host-processor and is responsible to administer it properly. The host-processor maintains the status of every block memory assigned to it, and also a list of all the other processors that have access to memory blocks, for every memory block to its jurisdiction. This hardware structure is called *directory* and is maintained within the cache hierarchy of each processor. Every time a processor wants to access a block that doesn't resides in its local cache, it sends a request to the *directory* of the owner processor. Depending on the type of the action requested, the *directory* is responsible to notify all the other caches that already hold a copy, and also provide the requested data, if needed. The interconnect connecting the processors of the systems is not required to have any specific properties, and affects

#### CHAPTER 1. INTRODUCTION

only the form of the messages exchanged. The *directory based* schemes have appeared later in the bibliography and as has been proved they have a very good performance. The key characteristic of this architecture is that it scales well when the number of processors available in a system increases. However, its major drawback is its complexity. Specifically, each directory structures constitutes a hot-spot of the system, since they receive requests by all the processors, including the local one, that require access to the range of memory assigned to it. Due to its complexity the implementation of such a scheme was rejected, and thus there will be no longer reference to it in the rest of the thesis.

On the other hand, shared memory systems that follow the second approach no parts of memory are assigned to any processor. At any given time, a processor that requests to access a memory block, which doesn't resides in its local cache, it sends a message to all the other caches. All the caches *snoop* the traffic on the interconnection network to identify a new message. If no cache has a copy of the requested block then the block is loaded from main memory. If, however, one or more caches maintain a valid copy, one of them sends the requested block back to the cache that requested it. Messages are used not only to facilitate data transferring. Every message is assigned a type, which has a specific meaning for the coherency protocol. Based on this type caches that receive such messages are becoming familiar about the intention of the requesting processor. Having this knowledge they are able to follow the steps imposed by the coherency protocol. This kind of coherency protocols adds an additional requirement from the interconnection network, which constitutes the basic property of the protocol. This requirement refer to the ability that must be offered to any cache to broadcast messages and also to *snoop* the bus activity. Otherwise, it is impossible for the distributed protocol to synchronize the processors' requests.

#### **Snooping Based Coherency Protocols**

There are two types of snooping based coherency protocols that have been proposed until now. Each one of them has been presented in many versions; however the basic steps remain identical. This separation of protocols is based on the action taken by the protocol in order to preserve coherency. Coherency is usually threatened by write actions, as was also presented in Figure 1.1. There are two ways to maintain the coherence requirement. The first one is to ensure that a processor has exclusive access to a data item before it writes that item. Protocols that follow this approach are usually called *write invalidate* protocol because of the action taken. The second way is to update all the other caches that hold a copy of the item addressed, with the new value that is about to be written. This type of protocol is called *write update* protocol. These two types of coherency protocols are described below.

#### 1.1. BACKGROUND

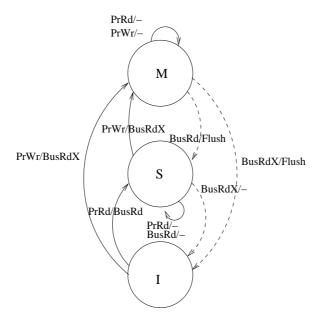

Write Invalidate Protocol A basic invalidate protocol is the three-state MSI write-back invalidation protocol. The protocol uses three states to encode the state of a cache block that resides in a processor's cache. These three states are the Invalid, the Shared and the Modified. The Invalid state corresponds to the absence of the requested block from the cache. The Shared state means the block is present in an unmodified state in the cache, the main memory is up-to-date, and zero or more copies of the block can be found in other caches. Finally, the Modified state means that only this cache has a valid copy of the block, and the copy in main memory is stall. Figure 1.2 depicts the state diagram of the protocol. Actions inducing transitions between states are shown next to the arcs. Processors issue two types of accesses, reads (PrRd) and writes (PrWr). Next to these accesses the corresponding bus messages, which will be generated upon a cache miss, are shown. A BusRd message is generated when a PrRd misses in the cache. The cache sends a BusRd message to request a copy of the specific block that doesn't intent to modify. A memory system participant, either some other cache or the main memory, will reply. A BusRdX message is generated when the processor wants to write a cache block that is either not present in the cache or is in the cache but not in the Modified state. The message is sent to all the other caches, which invalidate their copies, if they have one. A cache or the main memory supplies an exclusive copy of the block. The write action completes when the copy arrives in the cache.

Figure 1.2: State diagram for the MSI write-invalidate cache coherece protocol

Observing the state of blocks from the processor's side, a PrRd always causes the requested block

to transit to *Shared* state (transitions I to S and S to S). Furthermore, a *PrWr* always causes the requested block to transit to *Modified* state (transitions I to M, S to M, and M to M). Observing the state of the block from the bus's side then the following transitions can take place. A *BusRdX* message always causes the requested block to transit to *Invalid* state (transitions M to I and S to I). If the block is initially found in the *Modified* state, then the cache may have to reply with the cache block (flush action). Furthermore, a *BusRd* message always causes the requested block to transit to *S*. Again, if the block was initially found in the *Modified* state, the cache block was initially found in the *Modified* state, the

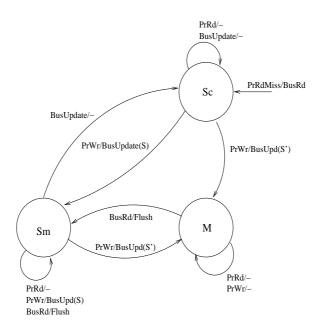

Write Update Protocol A basic update protocol is the three-state MSmSc write-back update protocol. The protocol uses three states to encode the state of a cache block that resides in a processor's cache. These three states are the SharedClean, the SharedModified and the Modified. The Shared-*Clean* state means the block is present in an unmodified state in the cache, the main memory may or may not be up-to-date, and zero or more copies of the block can be found in other caches. The SharedModified state means that one or more caches have a copy of this block, main memory isn't up-to-date, and it's this cache responsibility to update the main memory. Only one cache can be in SharedModified state for a specific block at each time. Finally, the Modified state means that only this cache has a valid copy of the block, and the copy in main memory is stall. Figure 1.3 depicts the state diagram of the protocol. Actions inducing transitions between states are shown next to the arcs. Processors issue two types of accesses, reads (PrRd or PrRdMiss) and writes (PrWr or PrWr).Next to these accesses the corresponding bus messages, which will be generated, are shown. A BusRd message is generated when a *PrRd* misses in the cache. The cache sends a *BusRd* message to request a copy of the specific block that doesn't intent to modify. A memory system participant, either some other cache or the main memory, will reply. A *BusUpdate* message is generated when the processor writes to a cache block. The bytes written by the processor are broadcasted to all the other processors so that they can update their copies, if they have one.

Observing the state of blocks from the processor's side, a *PrRd* always causes the requested block to enters the cache in the *SharedClean* state, or maintain itself in this state. On the other hand, a *PrWr* message can cause the block to transit either to *SharedModified* or to *Modified*. The final transition depends on the state of the block in the other caches. If the block is shared then the Sc to Sm transition takes place, otherwise the block transits to *Modified* state. If the block is initially absent from the cache a *PrWrMiss* is translated to a *PrRdMiss* followed by a *PrWr* scenario. Observing the state of the block

#### 1.1. BACKGROUND

Figure 1.3: State diagram for the write-update cache coherece protocol

from the bus's side then the following actions are taken. A *BusRd* message causes a modified block to enter one of the *Sc* or *Sm* states. It depends on the initial state of the block which one will be the resulting state. If the block was found in the *M* state then it transits to *Sm* state. Otherwise, if the block was found in either two states then it remains in that states. Whatever the transition might be the cache may be forced to transmit a copy of the block. On the other hand, a *BusUpdate* message can find a block only in the *Sc* or *Sm* state. In this case the block transits to *Sc* state, updating its part that is modified. Both of these two types of coherency protocols that resented above have been used the past years. Patterns of memory accesses may be presented that are served more efficiently by an invalidate or an update protocol. However, throughout the years the scientific community has shown a preference for invalidate protocols over the update ones. The main reason for this comes from the fact that the update protocols generate great amounts of traffic on the memory interconnect. For this study, an invalidate coherency protocol was chosen to be implemented. The protocol, which is presented in the next chapter, constitutes an extension of MSI protocol presented above.

#### 1.1.2 Chip Multiprocessors

While CMOS manufacturing technology continues to improve, reducing the size of single gates, physical limits of semiconductor-based microelectronics become a major design concern. Some effects of these physical limitations can cause significant heat dissipation and data synchronization problems. The demand for more complex and capable microprocessors causes CPU designers to utilize various methods of increasing performance. Some Instruction Level Parallelism (ILP) methods like super-scalar pipelining are suitable for many applications, but are inefficient for others that tend to contain difficult-to-predict code. Many applications are better suited to Thread Level Parallelism (TLP) methods, which suggest the parallel execution of multiple threads in one or more processors. Multiple independent CPUs is one common method used to increase a system's overall TLP. A combination of increased available space due to refined manufacturing processes and the demand for increased TLP led to the logical creation of Chip MultiProcessors (CMPs). CMP organizations combine two or more independent processors, often called cores, into a single integrated circuit. The cores are usually connected together using a Network-on-Chip (NoC) type interconnection network.

In general, the existence of multiple processors on a single chip provides excessive computational power. This can be translated by parallel applications as opportunity to exhibit thread-level parallelism (TLP) to a higher extend. Furthermore, communication between different CPUs is carried out faster as opposed to parallel computers. In a CMP system the end points of communication are found in the same chip. The messages exchanged between them don't experience the latency of traveling off-chip. As far as the hardware perspective is concerned, a CMP design disposes greater performance/power ratio than monolithic designs. An *n*-node CMP system consumes less power than *n* single processors. This comes from the fact that a CMP system has fewer pins, which also means that less power is consumed to drive signals external to the chip. Furthermore, the smaller silicon process geometry allows the cores to operate at lower voltages; while a part of significant size of the circuitry (part of the cache hierarchy) is usually shared among the processors. Finally, CMP designs are based on duplicates of the same core, which eases design scalability, and produces a product with lower risk of design error.

The major disadvantage of the CMP designs is the great power dissipation that results in increasing chip temperatures. A CMP chip may consume less power than *n* equivalent uniprocessor chips, however the total amount of power consumption remains prohibitive. Not all the cores are able to function at the same time for a long period of time, due to the fact that the circuitry will melt down. A solution to this problem suggests to dynamically switching on and off some of the available cores, in order to lower the consumption level. From an architectural point of view, ultimately, single CPU designs may make better use of the silicon surface area than multiprocessing cores.

## **1.2 Releated Work**

Many projects have undertaken the task of designing and implementing multiprocessor designs, in order to evaluate new architectures and ideas. Some of them [16, 17] come from the early 90s, when the *proof by construction* approach was very popular. In recent years, however, high financial cost and human effort of fabricating chips in modern process technologies have made building more daunting, and as a result fewer projects [18, 19, 20] have endeavored to build a full implementation.

The J-Machine [16] and the MIT Alewife multiprocessor [17] come from the parallel computers family, the predecessor architecture of the CMP organization. They are both organized as multinode systems, using a mesh network to connect all the components. The J-Machine uses messages to communicate data between the processors, while the Alewife multiprocessor follows the shared memory approach, using directory based coherence. However, there is also a hardware-software cooperation to support some sort of messaging among the processors.

The architecture of the Hydra Chip Multiprocessor [18] comes closer to the one studied here. The Hydra chip features four MIPS-based processors and their primary caches on a single chip together with a shared secondary cache. Each processor incorporates separate instruction and data caches, connected on a bus-based interconnect. An invalidation snooping coherency protocol is used to maintain coherency among shared data. To simplify parallel programming, the Hydra CMP supports thread-level speculation and memory renaming.

The Piranha architecture [19] follows the same approach with the Hydra CMP, however there are a number of differences. The Piranha has eight cores, each one of them having private first level cache. The second level cache, which does not maintain inclusion, is shared among processors, while the cache controllers use a more complex protocol to maintain coherence. A high-speed switch is used to connect the on-chip cores, instead of the bus that Hydra uses. Finally, the Piranha architecture is designed to provide scalability past a single chip by integrating the required on-chip functionality to support glueless multiprocessing.

The Raw CMP [20] is the first chip to organize its processors in a mesh. Specifically, it comprises of sixteen *tiles*; each one incorporating a compute processor, routers, network wires, and instruction and data memories. Raw distinguishes itself from others by being a modeless architecture and supporting all forms of parallelism, including ILP, DLP, TLP and streams. It uses messages to communicate data among the processors, while the on-chip interconnects belong to the class of scalar operand networks.

# Chapter 2

# **Design and Implementation**

In this chapter a detailed description about the design and the implementation of the whole system is given. Steps followed and choices made, concerning the different kinds of alternative solutions that could be followed, are presented and discussed.

### 2.1 General Description

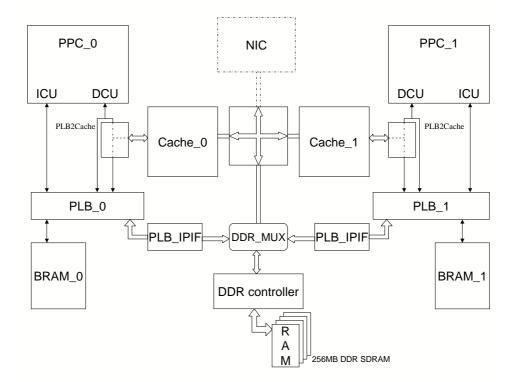

The architectural organization of the system can be seen in Figure 2.1. The whole system is organized based on the two IBM-PowerPC processors [9]. Each one of them is connected to a private bus, the architecture of which follows the "Processor Local Bus" specification given by the IBM [21]. The connection is established through the two PLB-master interfaces, Instruction-Side PLB (ISPLB) and Data-Side PLB (DSPLB). ISPLB is responsible for fetching instructions into the PowerPC's Instruction Cache Unit (ICU) and the DSPLB for fetching the required data into the Data Cache Unit (DCU). Physical memory is provided to the processors by internal BRAM blocks and external DDR memory. Instructions and private data can be stored in either the external or internal memory, while shared data can be stored only in the external DDR memory. BRAM blocks are directly connected to the corresponding PLB bus using an appropriate PLB-slave controller. The external DDR memory can be addressed in two different ways, regarding the kind of memory being accessed. If a processor accesses shared memory the only way to reach it is through the coherent memory system, otherwise private data and instructions located in the external memory are being accessed through the PLB2IPIF bridge, bypassing the coherent memory hierarchy. Requests for the external DDR memory are being multiplexed before reaching the DDR controller. DDR\_MUX is responsible for this operation, selecting and forwarding one request at a time to the DDR controller.

Figure 2.1: Architecture of the System

PowerPC's accesses, upon their initiation, are being separated to shared and private. The disjunction is performed based on the address provided by the processor. This operation is performed by the PLB2Cache module, which filters memory accesses considered to be shared and redirecting them towards the coherent memory system. In order this to become feasible the PLB2Cache module is inserted between the DCU pins of the PowerPC and the PLB bus.

The next step on the coherent path are the coherent caches. Both of them are equipped with a MESI-like cache coherent protocol in order to enforce cache coherency. The size of each cache is fully parameterized in order to try different organizations, while their associativity and the size of the cache lines are fixed and configured to 2-way and 8 words per cache line, respectively (as the internal caches of the PowerPC are). Regarding to the write policy, both caches handle "dirty" blocks following the write-back approach; every cache block that has been modified is written back to main memory when evicted by the cache and not when it is modified. Finally, evictions are handled in an LRU fashion.

When an access is forwarded to the cache there are two possibilities, either it can be handled by

#### 2.2. POWERPC 405

the cache or the request should be forwarded to the next level of the memory hierarchy. There are three reasons why an access cannot be handled by the cache. The first one is that the address requested lies in a non-cacheable shared address space and thus the request should be forwarded to the DDR controller. The second reason is that the requested block is not present in the cache and thus it should be requested by the next level of the memory hierarchy, and finally, the third reason is that the specific cache may have the requested data, but it doesn't hold the appropriate privileges to access them. In any of the above cases the coherency protocol must decide the set of actions required to satisfy the processor's request while preserving coherency. Simultaneously with processor's requests, the coherent cache is designed to receive requests issued by the adjacent processor, too. The coherency protocol is again responsible to detect any conflict that will result in loss of coherence and enforce a sequence of actions that will preserve coherency. Local and remote accesses to the cache can be handled in parallel, provided that there is no conflict, since tag information is stored in BRAM memory, which disposes two write ports and two read ports.

Finally, the two coherent caches and the DDR controller are connected to a memory interconnect, which is used to transfer requests and shared data to and from the participants. The interconnect has been designed to have the properties of a bus. Every memory access that doesn't hit in the local cache is being broadcasted. The remote cache snoops the bus activity in order to respond to requests issued by the local cache. If the requested data are found in the remote cache, which is called a remote-hit, they are sent back to the local cache. Otherwise, a negative respond is issued and the bus then forwards the request to the DDR controller. When the data become available are eventually sent to the local cache is able to send another request. This means that the bus doesn't support interleaved accesses and it starts to serve the next request only after having finished serving the previous one.

The rest of the chapter presents all the entities involved one by one. The behavior and the details of all the functional blocks designed and implemented are presented. Furthermore, basic blocks, which are part of the Xilinx EDK library, are also presented and their behavior is analyzed.

### 2.2 **PowerPC 405**

The PowerPC 405 is a 32-bit implementation of the PowerPC embedded-environment architecture that is derived from the PowerPC architecture [9, 10, 11]. Xilinx Virtex-II Pro FPGA family is equipped with two embedded PowerPC 405 processors, as hard blocks within the circuitry of the FPGA.

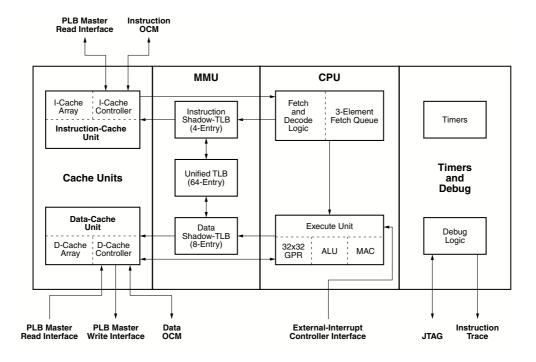

Figure 2.2 shows the internal structure and organization of the PowerPC 405. The centralprocessing unit (CPU) implements a 5-stage instruction pipeline consisting of fetch, decode, execute, write-back, and load write-back stages. The fetch and decode logic sends a steady flow of instructions to the execute unit, which are executed in-order.

Figure 2.2: PowerPC 405 Organization

Memory accesses initiated by the pipeline pass through the Memory Management Unit (MMU) before they reach the caches. Two modes of address translation, real and virtual, are supported. When operating in real mode the addresses generated by the program (logical address space) running on the processor is used directly by the hardware to access the data. In virtual mode, there is an intermediate step, where the logical address is translated (mapped) to a physical address, according to the translation found in the Translation Look-aside Buffer (TLB) table.

An instruction-cache unit and a data-cache unit are found next to the MMU. Each cache unit contains a 16 KB, 2-way set-associative cache array, plus control logic for managing cache accesses. The caches contain copies of the most frequently used instructions and data and can typically be accessed much faster than system memory. Each cache line stores 32 bytes of continuous and aligned memory, a tag used to identify the line within the set, a dirty bit that indicates whether the cacheline has been modified since the time that was loaded into the cache and an LRU bit, which specifies if

the specific line was (or not) the one least-recently used in the set. This information is used by the cache-line replacement algorithm when it is necessary to evict a cache line in order to fetch a new one. In that case, the least recently used cacheline is evicted.

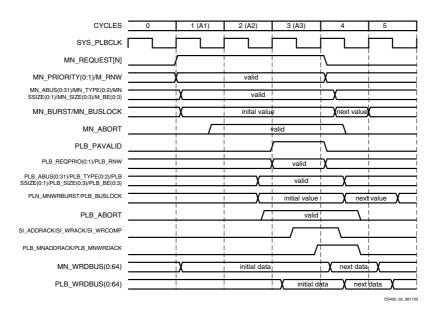

# 2.3 PLB Bus Interconnect

The Xilinx PLB [21] is an IBM CoreConnect compliant interconnect which allows multiple masters and multiple slaves to be connected to the bus. It consists of a central bus arbiter, the necessary bus control and gating logic, and all the necessary bus OR/MUX structures. The entire Xilinx PLB bus structure is provided as soft-core and allows for direct connection for up to 16 masters and 16 slaves. It supports both 64-bit and 32-bit peripherals to be connected at the same time. Each access requires 3-cycles for bus arbitration before the corresponding peripheral becomes aware of the request. At the end of the third cycle, the request can be safely latched by the peripheral. Figure 2.3 depicts a 3-cycle arbitration scenario.

Figure 2.3: 3-cycle PLB Arbitration

Except for the multiple masters, the PLB implementation also supports pipelining of the requests, permitting the existence of more than one pending requests. This capability maximizes PLB-transfer throughput by reducing dead cycles between multiple requests. Finally, in order to differentiate the importance of each of the multiple masters, four levels of dynamic master request priority are available.

# 2.4 PLB BRAM Controller, BRAM blocks and PLB2IPIF Controller

The PLB BRAM controller provides the opportunity of connecting some of the available BRAM memory to the PLB bus, and thus provides to the processors an easy way to access the embedded memory. It is attached to the PLB bus as a slave peripheral and translates the PLB protocol to a simpler form, which is recognizable by the BRAM block module.

The BRAM block is a reconfigurable memory module that provides the abstraction of the distributed memory available in the FPGA. Each block of memory has a size of 18432 bits, and can be available in different organizations, e.g. 512 lines x 36 bits per line. The Virtex-II Pro FPGA family has the physical block memory placed in columns equally distributed in the area of the FPGA. The total amount of BRAM memory available in an FPGA is relevant to the size of the FPGA. The bigger the FPGA the more available block ram embedded.

The PLB IPIF controller is a Xilinx soft-core [22], which targets to make the connection between User IPs and the PLB bus easier. It provides a bi-directional interface between a User IP core and the PLB 64-bit bus standard. For the purpose of this study two PLB2IPIF controllers were used, each one attached to a PLB bus. Both of them are connected as slave peripherals to the PLB. They were used as an additional way for the processor to access the external DRAM memory, through the DDR MUX block. The memory accessed this way is supposed to be private for each processor. However, for debugging purposes only, the PLB2IPIF controllers can be programmed to have a full view of the DRAM memory.

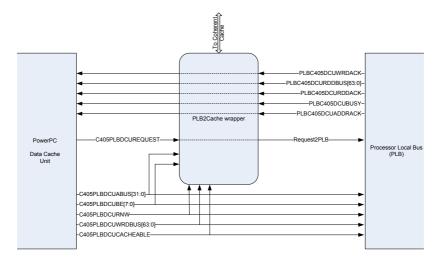

# 2.5 PLB2Cache module

PLB2Cache module is one of the two modules that connect the PowerPC with the rest of the units available on the system. Figure 2.4 presents the connection between the PowerPC, the PLB bus, and the PLB2Cache module. As it can be seen, the PLB2Cache module stands between the processor and the PLB bus. Its purpose is to examine all the requests generated by the DCU and filter out those that access shared memory. Filtered requests are forwarded towards the coherent memory system, while requests that access private memory are served by the PLB bus. Filtering of the accesses is based on the same signals that are used to connect the DCU to the PLB.

As it is shown in the figure the signals leaving the DCU C405PLBDCUABUS, C405PLBDCUBE, C405PLBDCURNW, C405PLBDCUABORT, C405PLBDCUWRDBUS, and C405PLBDCUCACHEABLE are connected to both the PLB and the PLB2Cache module. Sig-

Figure 2.4: Connection between the PowerPC, the PLB2Cache module, and the Bus

nal C405PLBDCUREQUEST, which was until now connected directly to the PLB bus, it passes through the PLB2Cache module. Every time the DCU generates a new PLB request, the PLB2Cache module examines the address. If the address accessed lies in private memory the request propagates through the PLB2Cache module reaching the PLB. Otherwise, the propagation of the request is stopped in the PLB2Cache module, the PLB never becomes aware of the request, which is forwarded and served by the coherent memory system. In the other way around signals PLBC405DCUADDRACK, PLBC405DCUBUSY, PLBC405DCURDDACK, PLBC405DCURDDBUS, PLBC405DCUWRDACK, and PLBC405DCUSBUSYS that were connecting the PLB to the DCU are now routed through the PLB2Cache module. They are driven by the PLB when a read PLB access returns data or by the PLB2Cache module when a shared memory read returns data.

Placing the PLB2Cache module between the processor and the bus offers many advantages. Accesses to shared memory are not served by the PLB bus. This means that they don't sustain the timing costs of the arbitration and the sharing of the bus with the ICU, which is also connected to the PLB. For these accesses, the DCU transfers data at its fastest speed, since the custom design (PLB2Cache, Cache) is aware of the potentials of the DCU and tries to take advantage of them every time an external cache hit occurs. Furthermore, when the DCU operates in maximum speed, many accesses are acknowledged as soon as possible, which favours pipelined requests to take place. Finally, filtering out some memory accesses favours the rest of the instructions and private data requests to be served

faster, since less traffic passes through the PLB bus.

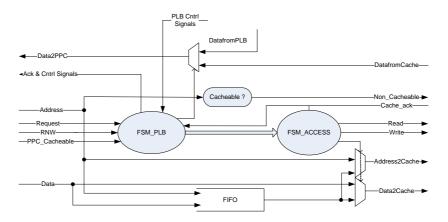

# 2.5.1 PLB2Cache Module Architecture

Figure 2.5 depicts the internal organization of the PLB2Cache module. The organization of the whole module is based on the two FSMs that co-operate in order to make the DCU communicate with the coherent cache. The left one, FSM\_PLB, is responsible for listening and filtering requests whose addresses lie in the shared memory region. It simulates the behaviour of a PLB slave peripheral in order to give the illusion to the DCU that is still directly connected to the PLB bus. The logic generated for FSM\_PLB also contains the signals from PLB to DCU. When a request is served by the PLB, these signals are forwarded to the DCU. When a request is served by the coherent cache, equivalent signals driven by custom logic are forwarded to the DCU. The right one FSM, FSM\_ACCESS, is responsible for translating the PLB protocol to a simpler format. This format is used from the PLB2Cache module in order to communicate with the coherent cache. The need of having two FSMs in parallel comes from the intention to operate the DCU in its maximum speed for the shared memory accesses. In order this to become feasible, both read and write accesses must complete (with respect to the DCU) as soon as possible. Read requests cannot complete before the requested data become available,

Figure 2.5: PLB2Cache Architecture

however, write requests can complete in two cycles time. Additionally, in any kind of request (read or write) the first phase, which has to do with the acknowledgement of the address, can also complete very fast, specifically in the first cycle of the request. Following this tactic the DCU will operate in its maximum speed and the number of overlapping data accesses will increase, since requests are acknowledged immediately.

No matter how fast requests are acknowledged, they cannot be considered completed until the

action is considered to have finished for the rest of the coherent memory system, too. Acknowledging requests that fast requires storing them in a queue in order to be served in the future. This is accomplished by the use of a FIFO, in which pending requests are stored. The FIFO has a depth of 16 words. Every time the FSM\_PLB identifies a new access to shared memory and FSM\_ACCESS is busy with a previous request, the new request is pushed into the FIFO. If it is a read request it will occupy only one word, otherwise a write request occupies two. During the cycle that the address of the request is acknowledged, it is also pushed into the FIFO. In the following cycle the data is also written, in case of a write access. When the FSM\_ACCESS becomes available it will serve the first request in the queue. Since write requests are able to complete (with respect to the DCU) in two cycles time, the FIFO will usually contain some write requests that will have been gathered and will be waiting to be served. At some point in time the program will eventually generate a read request, which will be pushed at the end of the queue. The execution of the program will be blocked waiting for the read to complete. As it can be seen, acknowledging and queueing requests improve the performance in a short-term period. However, in a longer-term period a read access will face the cumulative delay of all the previous accesses, balancing the progress of the execution of the program.

Finally, within the range of shared addresses there is a sub-range, which corresponds to noncacheable shared data. The addition of this feature was considered to be crucial, since many processors use non-cacheable accesses to read or write device registers or other special I/O components. The size of that space is parameterized and must be defined before the implementation of the system. The PLB2Cache module is designed to check some most significant bits of the address provided by the processor in order to identify a non-cacheable access to shared data. This happens in parallel with the examination of the address that recognizes a shared memory access.

# 2.6 Coherent Cache

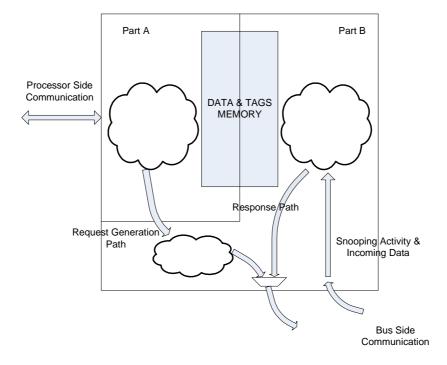

The next step, after the PLB2Cache module, in the coherent memory system is the coherent cache. As explained in the previous chapter, the role of a coherent cache is twofold. It acts as a normal cache, providing access to commonly used data, but it's also responsible for maintaining the shared data coherent with respect to other processors as well. For this study, a bus-based coherence scheme was chosen to be implemented. Figure 2.6 depicts a coarse description of the coherent cache architecture. As it can be seen, the whole module is organized around the BRAMs that store data and tag information, and is divided in two parts. Part A is responsible for serving the processor's requests that come

from the PLB2Cache module. Part B is responsible for sending requests generated by part A to the bus, and serving requests that are received from the bus. Both parts are responsible for maintaining coherency among data, thus, both of them must have access to tag information and run the coherency protocol.

Figure 2.6: Coherent Cache General Description

Modern microprocessors achieve this by making a duplicate of the tags memory. In this study, the two parts take advantage of the BRAM architecture. BRAMs can be configured to have two two-port interfaces, without paying any area or hardware cost. Each interface provides read and write ports, and thus simultaneous access to data. However, care must be taken when both interfaces access the same address. The architectural definition of the BRAMs doesn't provide any guaranty of what can happen in this case, except for the fact that the hardware will not be damaged. Solution to this problem was given by clocking the two interfaces with clocks of the same frequency but different phase. More details about that will be given below.

## 2.6.1 Cache Characteristics

The coherent cache was designed to have similar characteristics with the internal caches of the PowerPC, without losing the ability of making slight transformations in order to simulate different operational parameters. The size of the coherent cache is fully parameterized, while its associativity is programmed to be 2-way. The size of the cache line is fixed and set to 8 words per cache line. As far as the write policy is concerned, the cache follows the write-back scheme. In order to resolve block conflicts, the cache is equipped with an LRU algorithm. An LRU-bit corresponds to each set of cache lines. Every time an access occurs, this bit stores the information of which associate of the set served the corresponding access. Specifically, the bit is cleared if the access is served by the associate '0', or set to '1' if the access is served by the associate '1'. In this way the least recently used line within the set is unmarked. When a block conflict occurs, it is resolved by evicting the least recently used cache line of the set. Finally, in order to decrease cache miss penalty, the cache is organized to return the requested word within the line as soon as the word becomes available. The cache requests the missing cache line providing the address of the word that caused the miss. If the entity that responds to the cache sends the requested cache line transmitting the "critical" word first, then the cache follows the critical-word-first scheme. Otherwise, if the cache line is sent to the cache in a lowest-to-highest address order then the cache follows the early-restart scheme.

#### 2.6.2 Tags and Data Memory Organization

The internal distributed BRAM blocks are used to store tag and data information. The amount of BRAM memory required is not fixed, since the size of the cache is parameterized. However, the organization of the BRAMs is predefined. A set of BRAM blocks is assigned to each associate in order to store data and tags information. The BRAM blocks that form the data part are organized in order to handle 32-bit wide words, while words that lie in the same cache line are stored in subsequent addresses. On the other hand, the tag-word has not a fixed size. Its size depends on the whole size of the cache, since the information stored contains a part of the address provided by the processor. Addressing of the data and tag parts is similar. The tag memory is addressed using the 'index' part of the initial address, while the data part uses the 'index' along with the 'block offset'. The index bits are calculated by the formula:

$$2^{index} = \frac{Cache \ size}{block \ size \cdot \ set \ associativity} \tag{2.1}$$

The block size and the associativity are constant, 32 bytes and 2-way, respectively. The size of the address given by the processor is 32-bit wide. The two least significant bits are not used by the cache. Bits 2 to 4 form the block offset, which is the address of each word in the cache line. Bits 5 to 5 + index - 1 are the index bits, and the rest bits of the address are the tag bits.

A tag-word includes the tag part of the address that corresponds to the specific cache line, 2 bits for the coherency protocol and one 'dirty' bit. Tag information for both the associates is being kept in different BRAM blocks. This is justified by the fact that two tag-words don't fit in 36 bits, which is the actual width of a BRAM block. If tag information for both the associates was supposed to be kept in a single word, then each tag-word should be at most 18-bits wide. This corresponds to 15 bits of tag size, which is equivalent to cache size of at least 256KBytes.

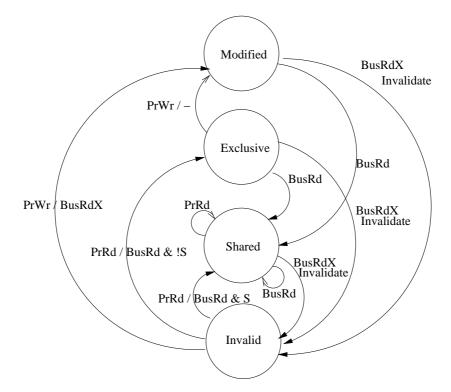

#### 2.6.3 Coherency Protocol

The coherency protocol used in this study is a typical four-state MESI protocol. The protocol uses 4 states to encode the status of a cache line. These are: Invalid, Shared, Exclusive and Modified. Cache lines that don't store any data are marked as invalid. Shared means that the block is present in an unmodified state in this cache, the main memory is up-to-date, and zero or more other caches may also have an up-to-date copy. The exclusive state has the same meaning with the Shared, however no other cache has a copy of the block. Finally, Modified means that only this cache has a valid copy of the block and main memory is out-of-date. Figure 2.7 depicts a state diagram of the protocol.

Figure 2.7: Coherency Protocol State Diagram

Actions that cause each transition to occur can be seen next to the vertices. Table 2.1 shows the

#### 2.6. COHERENT CACHE

| Block's State | Processor's Request |            |  |  |

|---------------|---------------------|------------|--|--|

| Block's State | PrRd                | PrWr       |  |  |

| Ι             | BusRd               | BusRdX     |  |  |

| S             | -                   | Invalidate |  |  |

| E             | -                   | -          |  |  |

| М             | -                   | -          |  |  |

Table 2.1: Generation of Coherent Requests

bus messages that will be generated for each one possible situation. PrRd stands for processor's read actions and PrWr for write. BusRd, Invalidate and BusRdX are the messages that are generated in order to maintain coherency. BusRd is generated every time a processor's read misses in the cache. Invalidate is generated when a processor's write doesn't have the privileges to complete, which means that the block is found in shared state, and BusRdX when a processor's write misses in the cache.

The letter 'S', in Figure 2.7, next to the actions denotes the status of the requested block in all the other caches. 'S' means that the block is found shared in at least one cache, while 'S' that the block is not shared at any cache. Transitions between states are caused by processor or bus accesses. When the block is first read by a processor a BusRd message is broadcasted. If a valid copy exists in another cache, then it enters the cache in the Shared state. However, if no other cache has a copy at that time, the block enters in the Exclusive state. When the block is written by the same processor, it can directly transition from the Exclusive state to Modified state, without generating any bus transaction. If another cache has obtained a copy in the meantime, the state of the block would have been denoted from Exclusive to Shared. In that case an Invalidate message is broadcasted to notify every other cache to invalidate the copy they hold. When a processor tries to write a cache block but the block is absent from the cache a BusRDX message is broadcasted. The caches that hold a copy of the requested block will invalidate it. One of these caches will transmit the cache block back to the cache that requested the write privileges. The block enters the cache in Exclusive state and then immediately transits to Modified (with the completion of the write access). From the side of the bus, a BusRd message always results in a demotion of the block's state to Shared, if the block is found in the cache. A BusRdX message also demotes the block's state, if the block is found in the cache, but the resulting state is the Invalid state. Same things hold for the Invalidate bus message. BusRd and

BusRdX messages always cause the transmission of a cache block. On the other hand, an Invalidate message doesn't create any other traffic, except for the message itself. That's the difference between the BusRdX and the Invalidate message. They both demotes the privileges of the cache block, when the block is found in remote caches, but only a BusRdX message requires a respond to be generated.

An extra property has been given to the cache, which has to do with the capability of receiving update messages. Any MESI-like protocol is based on invalidating copies of the same block when exclusive access is required. Thus, the kind of update messages supported in this study doesn't modify the state of the block updated. When an update message is issued (by a coherent network interface maybe, but not a cache) it is broadcasted to all the participants, including the main memory. The state of the block, wherever it resides, doesn't change. However, the data do change, resulting to everyone having an up-to-date version of the block.

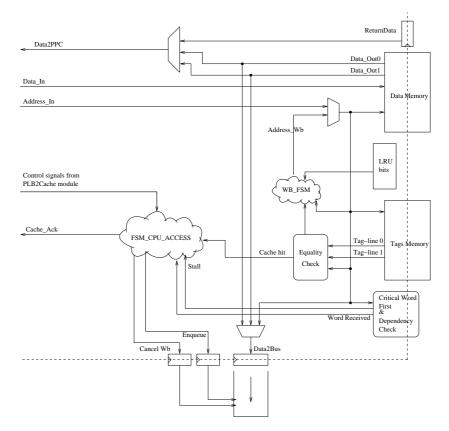

#### 2.6.4 Part A: Cache's Processor side

Figure 2.8 shows a block diagram for the processor's side part of the coherent cache. Part A operates with the same clock that the processor uses to generate requests. The same clock is used by the PLB2Cache module and the PLB bus. It receives the following signals from the PLB2Cache module: Read\_Cmd, Write\_Cmd, Address, Data\_In and Non\_cacheable\_access. It returns an acknowledge signal, Cache\_Ack, and the Data\_Out signal. During a cache access all input signals are stable and valid, and remain so until the cache asserts the Cache\_Ack signal. This signal remains high for only one positive edge in order to mark the completion of the access. If the access that finishes is a read access (cacheable or non-cacheable), signal Data\_Out carries the requested data.

There are two FSMs that handle this part, FSM\_CPU\_ACCESS and WB\_FSM. FSM\_CPU\_ACCESS manages every single request made by the processor and is also responsible for maintaining coherence. It is one of the basic blocks of logic that run the coherency protocol to decide the next actions that should be followed. Every time a cache block doesn't have the appropriate sharing status for the processor's access to complete FSM\_CPU\_ACCESS generates a bus message. The message is forwarded to part B in order to be broadcasted on the interconnection network. WB\_FSM is responsible for handling write back activity. Write back activity corresponds to transferring modified blocks back to main memory. This transfer takes place when an access that misses in the cache requires a new cache block to be loaded in. The new block that comes in conflicts with the two blocks that are already present in the cache. These two blocks occupy the whole specific set, in which the new block is mapped. The replacement algorithm is called to resolve this conflict by

#### 2.6. COHERENT CACHE

choosing a block to be evicted from the cache. The block that is least recently used is chosen to leave the cache. If that block is 'clean' then the incoming block just over-writes it. If, however, the chosen block has been modified, it must be written back to main memory.

A write-back transfer is not considered to be a separate bus transaction. It is hidden behind the block transfer that generated the eviction. That is feasible because the implementation of the bus offers different sub-buses for transferring data from and to the cache. Immediately after the bus request has been transferred, the write-back action is initiated. The address of the evicted block is first transferred and then the data in a critical-word-first fashion.

Figure 2.8: Part A block diagram

Apart from the two FSMs, other important entities in the figure are the equality check modules and the dependency check logic. The purpose of the equality check module is to compare (for equality) the tag part of the incoming address with the tag stored in each of the two associates. The use of the '==' Verilog operator is interpreted by the Xilinx flow as the instantiation of a complete comparator, from which only the equality operation is used. This adds extra area and timing cost. The solution to this was the implementation of a simpler module, which is checking bit by bit the tag parts of the

addresses. Finally, the purpose of the dependency check module is to compare the addresses that are accessed by the processor and the bus. If both of them want to use the same cache block for conflicting purposes (read and write, write and write) an order must be enforced and one of them to wait. In this case the processor side is chosen to wait. The dependency check module blocks the processor's access until part B finishes its operation on the data. This module also implements the "critical-word-first" feature of the cache.

#### **Dependency Check module**

As mentioned above, concurrent accesses by the processor and the bus must be checked in order to verify that they touch different cache blocks. If not, ordering is imposed to them by making processor's access to wait for the completion of the bus access. Not all combinations of accesses require ordering even if they access the same data.

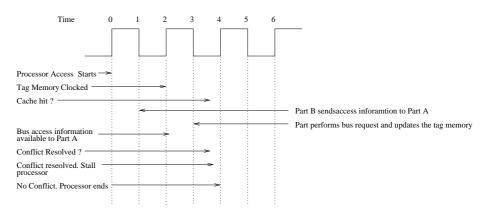

Figure 2.9: Two First Cycles of a Processor Access

Figure 2.9 presents the first two cycles of a processor's access and the two crucial periods, the periods that part B modifies the tag memory, of a bus access. The processor's access is placed starting at time 0 and finishing at time 4. Such an access is a cache hit. There would be no meaning to talk for cache misses, since they never conflict with bus accesses. During the first cycle, from time 0 to time 2, address becomes stable on the address pins of the tag memories. The memories are clocked at time 2 by the positive edge of the clock and return data somewhere between time 2 and time 3 (actually, 1.5 ns after time 2). Then the tags are compared with the address accessed to check for cache hit. Cache hit is resolved and at time 4 the access completes by either returning data to the processor, in case of a read, or data written in cache, in case of a write. Part B doesn't operate with the same clock. It uses a clock of the same frequency but different phase. Actually, it uses the negation of part A's clock. Thus,

#### 2.6. COHERENT CACHE

|                 | BusRd | BusRdX | Invalidate | Update |

|-----------------|-------|--------|------------|--------|

| Processor Read  | No    | No     | No         | Yes    |

| Processor Write | Yes   | Yes    | Yes        | Yes    |

Table 2.2: Combinations of Accesses

events as memory accesses in part B may take place in time 1 or time 3 etc. All of the bus requests shown in Table 2.2 may modify the tag information of the cache block they access. BusRd, BusRdX and Invalidate messages modify the tag and read the data, while Update messages modify both the tag and the data. Thus, processor accesses compete with BusRd, BusRdX and Invalidate accesses for accessing the tag memories, when both sides request the same cache block. On the other hand processor accesses must wait the completion of an Update message if they access the block that is being updated.